译码器专题

数电知识复习3------编码器和译码器

目录 1.编码器类型 1.1 二进制编码器 1.2 二- 十进制编码器 1.3优先编码器 2.译码器的概念和类型 2.1 二进制译码器 2.2 3-8译码器 2.3 4-10译码器 2.4 数码显示译码器 1.编码器类型 1.1 二进制编码器 1.2 二- 十进制编码器 1.3优先编码器 2.译码器的概念和类型 2.1 二

数字电路与逻辑设计实验-MSI译码器逻辑功能测试

一.实验目的 1.掌握中规模(MSI)集成译码器的逻辑功能和使用方法; 2.验证3—8线译码器和七段显示译码器的逻辑功能; 3.掌握数码管与译码器配合使用的方法。 二.实验原理 译码器的作用是进行代码间的“翻译”,将具有特定含义的二进制码进行辨别,并转换成控制信号。 译码器分通用译码器和显示译码器两大类。前者又分为变量译码器和代码变换译码器。 l.变量译码器(又称二进制译码器)

Huffman编译器和译码器设计(一)

1. 需求分析 设计一个哈夫曼算法的编码和译码系统,重复地显示并处理以下项目,知道选择退出为止。 将权值数据存放在数据文件中;分别采用动态和静态存储结构; 1. 读权重数据文件获得权重和字符的对应数组2. 手动输入字符与对应权重值3. 通过权重字符对应数组生成哈弗曼树4. 利用建立好的哈弗曼树生成哈弗曼编码5. 通过建立好的哈弗曼树解析哈弗曼编码生成译码

【EP2C35F672C8 EDA试验箱下载 38译码器实现】

文章目录 前言一、实验设备1.实验箱2.下载器: 二、编译工程1.编译工程2.添加tcl引脚配置文件2.1将tcl文件拷贝到工程目录下:2.2 在软件中添加tcl文件 3.tcl文件简答讲解 三、下载四、实验结果总结 前言 提示:这里可以添加本文要记录的大概内容: 课程需要:展示EP2C35F672C8 EDA试验箱 38译码器实验下载验证 提示:以下是本篇文章正文内

实验3 7段数码管译码器动态显示

实验目的: 1、构建基于verilog语言的8位7段断数码管的驱动实验; 2、掌握数码管的数显原理。 3、完成如下功能:8位数码管循环显示0123456789。 实验内容及步骤: 一、实验原理 1、数码管结构 当数码管特定的段加上电压后,这些特定的段就会发亮,以形成我们眼睛看到的字样了。如:显示一个“2”字,那么应当是a亮b亮g亮e亮d亮f不亮c不亮dp不亮。发光二极管的阳极连接到一

基于proteus的51单片机仿真实例七十八、使用BCD译码器实现8位数码管显示应用实例

1、在此前有关数码管显示的例子中,单片机必须要发送段码才能够让数码管显示正确的数字。 本例使用7段数码管显示译码器4511,单片机可以直接输出BCD码,4511能够自动将BCD码转换为数码管的段码。 2、在keil c51中新建工程ex66,编写如下程序代码,编译并生成ex66.hex文件 //使用BCD码译码器控制数码管显示

基于proteus的51单片机仿真实例七十四、4-16译码器74HC154应用实例

1、本例通过4-16译码器74HC154实现用4个IO口控制16个LED循环点亮 2、在keil c51中新建工程ex62,编写如下程序代码,编译并生成ex62.hex文件 //4-16线译码器实例 #include <reg51.h> //延时函数 void delayms(unsigned int x) { unsigned char i; whil

基于proteus的51单片机仿真实例七十三、3-8译码器74HC138应用实例

1、本例在单片机的P2端口的低三位(P2.0-P2.2)上连接3-8译码器74HC138的3线输入端,然后在8线输出端连接8个LED,通过译码器控制8个LED循环点亮。 具体操作需要参照74HC138的真值表来进行。 2、在keil c51中新建工程ex61,编写如下程序代码,编译并生成ex61.hex文件 // 3-8译码器74HC138应用实例 #include

11 - 三八译码器和存储器组织

---- 整理自B站UP主 踌躇月光 的视频 1. 38译码器 1.1 真值表 A2A1A0O7O6O5O4O3O2O1O00000000000100100000010010000001000110000100010000010000101001000001100100000011110000000 O 0 = A 2 ‾ A 1 ‾ A 0 ‾ O 1 = A 2 ‾ A 1 ‾

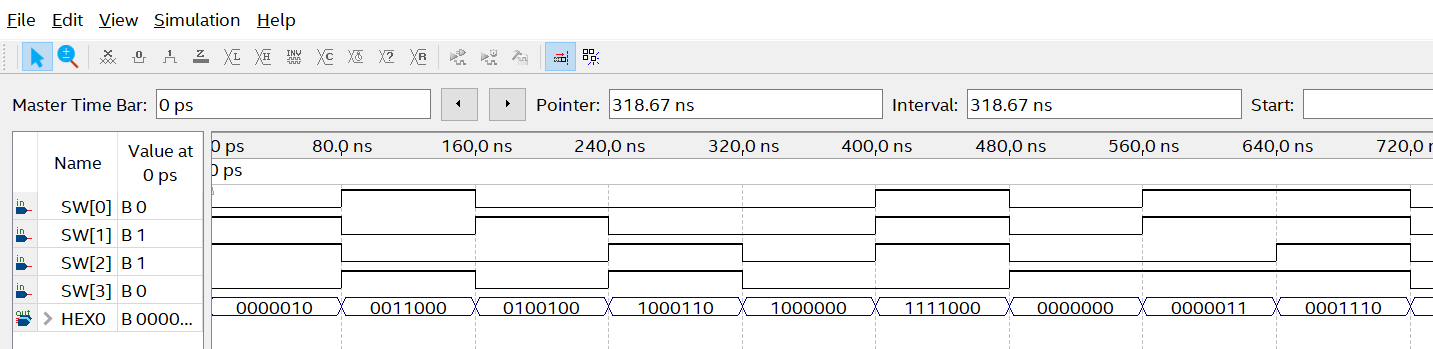

第17篇:七段数码管译码器

Q:之前我们设计实现的逻辑电路最终输出结果都是通过LED显示,本篇我们将实现用七段数码管来显示输出结果。 A:七段数码管显示基本原理:DE2-115开发板有8个共阳极数码管,即低电平逻辑值0点亮数码管段、逻辑值1来使数码管段熄灭。七段数码管译码器有4个输入端口,7个输出端口连接数码管的七个段。4个输入共有16种不同状态组合,对应十六进制数0~F。数码管显示比如0时,第6段是熄灭状态,给它的是高电

组合逻辑电路(二)(译码器和编码器)

目录 译码器 简单逻辑门译码器 二进制译码器 2线-4线译码器 3线-8线译码器 二-十进制译码器 4线-10线译码器 七段显示译码器 编码器 二进制普通编码器 二-十进制普通编码器(8421BCD码编码器) 优先编码器(Priority Encoder) 译码器 将输入的代码译为特定对象(如逻辑电平),用于检测特定数字状态的组合逻辑电路 译码 利用译码表将具有特定含义的文字

低密度奇偶校验码LDPC(八)——QC-LDPC译码器FPGA设计概要

往期博文 低密度奇偶校验码LDPC(一)——概述_什么是gallager构造-CSDN博客 低密度奇偶校验码LDPC(二)——LDPC编码方法-CSDN博客 低密度奇偶校验码LDPC(三)——QC-LDPC码概述-CSDN博客 低密度奇偶校验码LDPC(四)——双对角线结构的QC-LDPC编码-CSDN博客 低密度奇偶校验码LDPC(五)——译码算法概述-CSDN博客 低密度奇偶校验

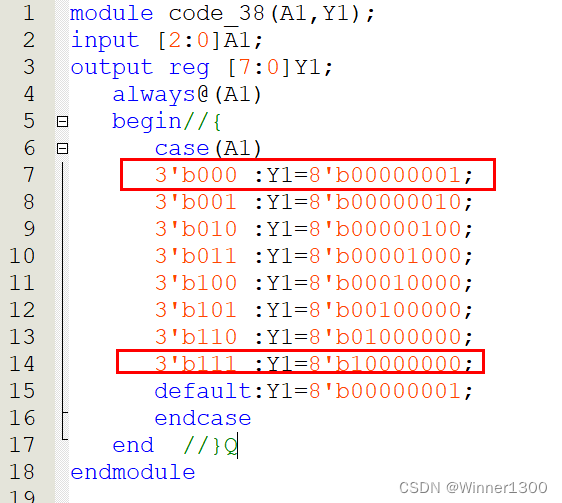

FPGA学习之三-八译码器(板间实现)

FPGA第二个例程 3-8译码器 用三个拨码开关控制八个led灯中的某一个灯点亮 代码如下: module cy4(input ext_clk_25m, input ext_rst_n, input[3:0] switch, output reg[7:0] led ); //-------------------------------------always @

【数据结构 】哈夫曼编译码器

数据结构-----哈夫曼编译码器 题目题目描述基本要求算法分析 代码实现初始化编码解码打印代码打印哈夫曼树 总结 题目 题目描述 利用哈夫曼编码进行信息通信可大大提高信道利用率,缩短信息传输时间,降低传输成本。 要求:在发送端通过一个编码系统对待传数据预先编码;在接收端将传入的数据进行译码(复原)。对于双工信道(即可以双向传输信息的信道),每端都需要个完整的编/译码系统。试为

FPGA学习之三-八译码器(板间实现)

FPGA第二个例程 3-8译码器 用三个拨码开关控制八个led灯中的某一个灯点亮 代码如下: module cy4(input ext_clk_25m, input ext_rst_n, input[3:0] switch, output reg[7:0] led ); //-------------------------------------always @

4.4 基于switch语句的译码器(C语言实现)

【题目描述】给定一个前缀码表如下:a—1,b—01,c—001。又有一个0/1字符串为“001011101001011001”,编写一个C程序,按照给定的前缀码表为该字符串译码。 【题目分析】前缀码是一种无二义性的编码,因此可以作为一种编码体制被广泛应用。一些编码,例如:a—001,b—0011,c—1,这就会出现所谓的译码时的二义性,也就是说当翻译到0011时无法确定是b还是ac。因此如果设计长

[数字电路]用与非门实现BCD译码器驱动数码管

Hello,大家好。这里是xdd_core,好久不见。今天来和大家聊聊大一数字电路课程的一个课设。 Key word:BCD Decoder,Proteus8.x,NAND Gate,Digital Circuit 流程:Proteus8.x仿真电路并绘制PCB导出Gerber文件打样,最终实物验证。 以下为我对这个课设的report(里面对整个设计做了详细介绍,并设计了完整的验证电路)

维特比译码器(Viterbi Decoder)硬件架构(一)--卷积码及编解码算法介绍

1. 卷积码(convolution code) 卷积码在无线通信里用的非常广泛,通常卷积码编码器开始工作前都要进行初始化,按编码器的初始状态不同可以分为两类: 1.1 末尾补零卷积码(Tail-bits): 通常卷积码编码器开始工作时都要进行初始化,编码开始前将编码器的所有寄存器单元都进行清零处理。而在编码结束时,需要添加0到码流末尾(Tailed Termination),使编码器状态归

北邮22级信通院数电:Verilog-FPGA(7)第七周实验(2):BCD七段显示译码器(关注我的uu们加群咯~)

北邮22信通一枚~ 跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章 持续关注作者 迎接数电实验学习~ 获取更多文章,请访问专栏: 北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客 关注作者的uu们可以进群啦~ 一.verilog代码 1.1 decoder_led.v module decoder_led(A,RBI,LT,BI_RBO,seg_le

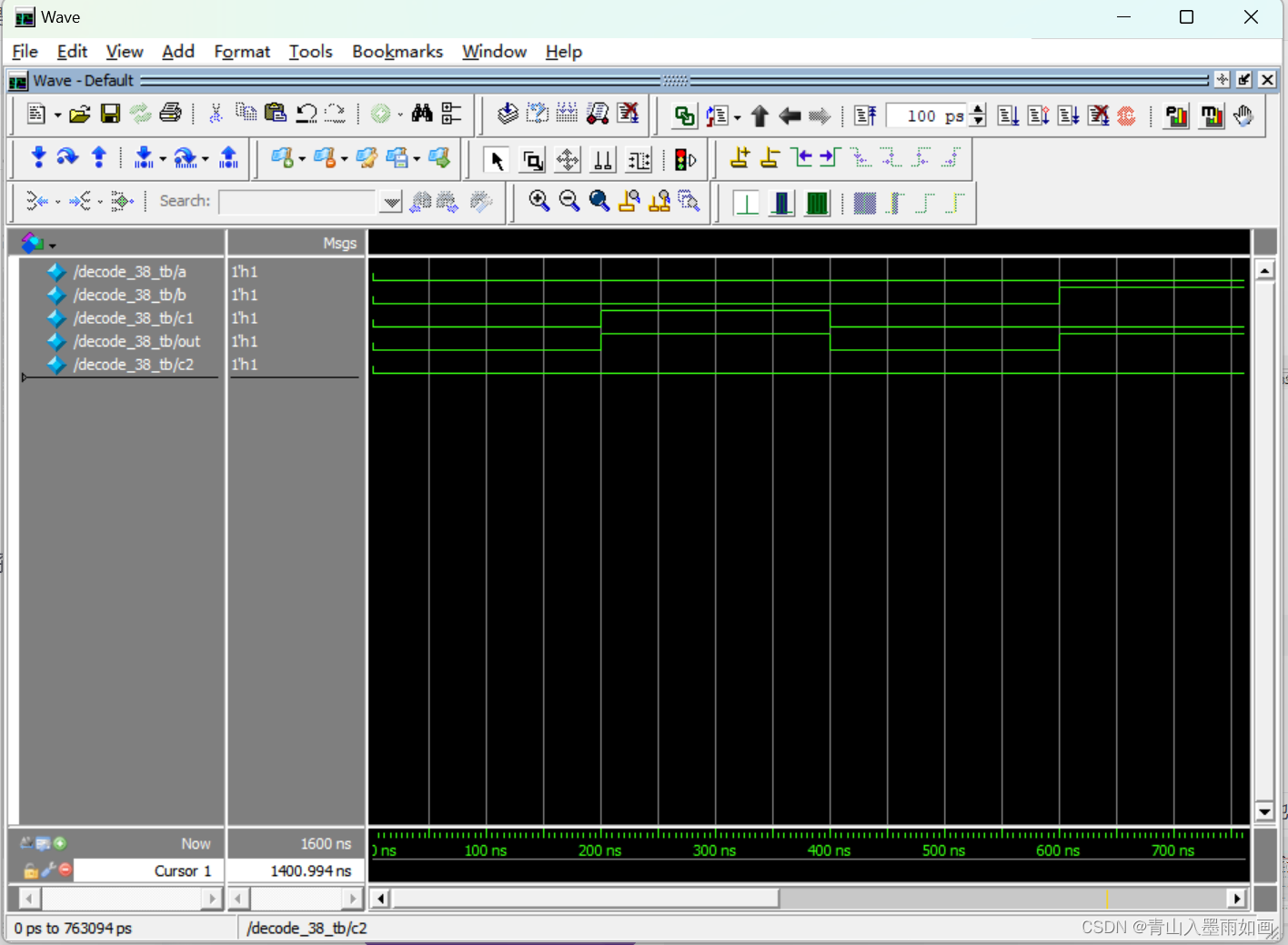

北邮22级信通院数电:Verilog-FPGA(7)第七周实验(1):带使能端的38译码器全加器(关注我的uu们加群咯~)

北邮22信通一枚~ 跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章 持续关注作者 迎接数电实验学习~ 获取更多文章,请访问专栏: 北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客 关注作者的uu们可以进群啦~ 目录 方法一:modelsim仿真检验结果 1.1verilog代码 1.1.1 decode_38.v(顶层模块) 1.1.2dec

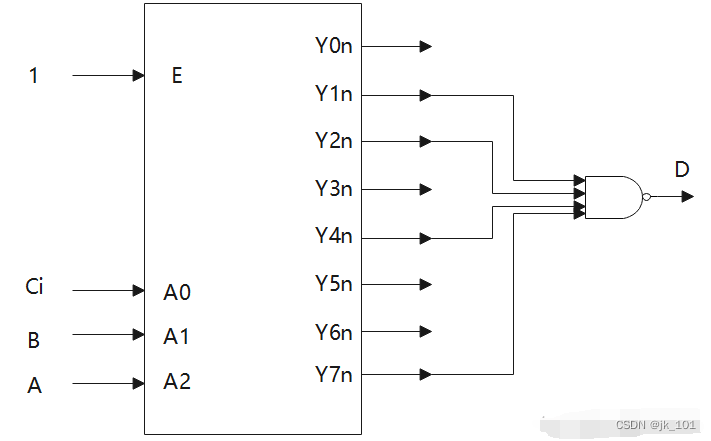

用3-8译码器实现全减器

描述 请使用3-8译码器和必要的逻辑门实现全减器,全减器接口图如下,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位。 3-8译码器代码如下,可将参考代码添加并例化到本题答案中。 module decoder_38(input E ,input A0 ,input

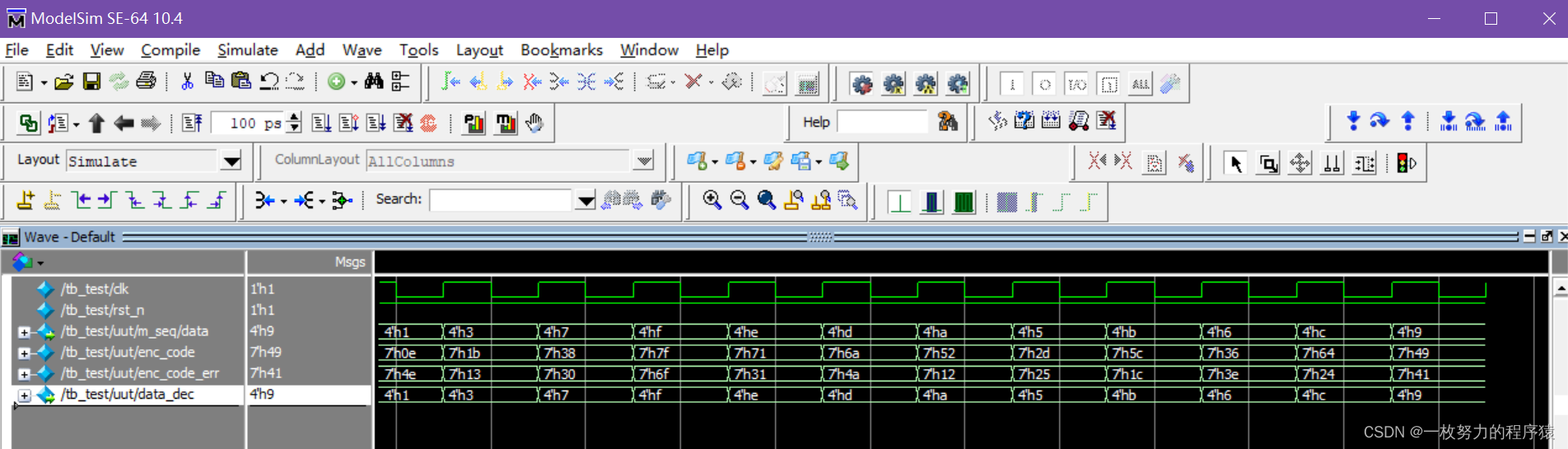

基于VHDL(Verilog)语言的汉明码编码器和译码器的设计(串行设计)

基于Verilog语言的汉明码设计,刚开始根据汉明码的原理,设计了并行的输入和clk,产生数据。 汉明码的实质及原理 汉明码实质上是个多重奇偶校验,实现原理为:在有效信息位中加入几个校验位形成汉明码,使码距比较均匀的拉大,最大的特点:具有校验并纠正一位错误的能力。 原来的设计(课程设计大部分都这么设计) 后面发现要求不对,输入信号需要自己使用m序列产生。并且采用串行的方式 总体思

![[数字电路]用与非门实现BCD译码器驱动数码管](https://img-blog.csdnimg.cn/20200801125212989.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM2MjI5ODc2,size_16,color_FFFFFF,t_70)