本文主要是介绍用3-8译码器实现全减器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

描述

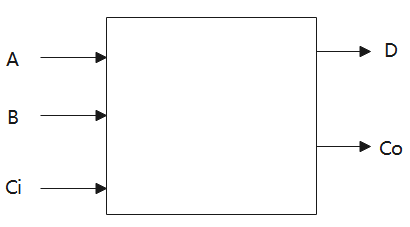

请使用3-8译码器和必要的逻辑门实现全减器,全减器接口图如下,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位。

3-8译码器代码如下,可将参考代码添加并例化到本题答案中。

module decoder_38(input E ,input A0 ,input A1 ,input A2 ,output reg Y0n , output reg Y1n , output reg Y2n , output reg Y3n , output reg Y4n , output reg Y5n , output reg Y6n , output reg Y7n

);always @(*)beginif(!E)beginY0n = 1'b1;Y1n = 1'b1;Y2n = 1'b1;Y3n = 1'b1;Y4n = 1'b1;Y5n = 1'b1;Y6n = 1'b1;Y7n = 1'b1;end else begincase({A2,A1,A0})3'b000 : beginY0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b001 : beginY0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b010 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b011 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b100 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b101 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;end 3'b110 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;end 3'b111 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;end default: beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;endendcase end

end endmodule

输入描述

input A ,input B ,input Ci 输出描述

output wire D ,output wire Co 解题分析

3-8译码器实现全减器

38译码器的输出实际上包含了输入A2 A1 A0组成的所有最小项,而全减器作为组合电路,其输出最终可化简为最小项的形式。

由于译码器的输出为最小项取反,而逻辑函数可以写成最小项之和的形式,故可以利用门电路和译码器实现逻辑函数。

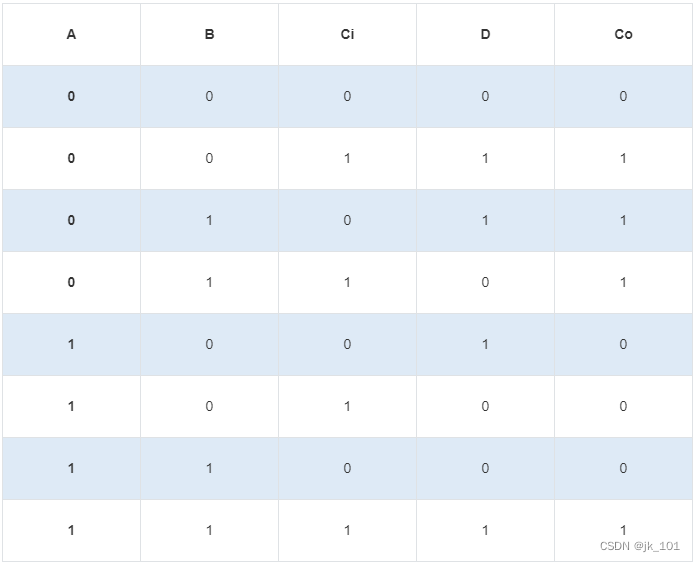

需先列出全减器的真值表。

由真值表可得出,输出D的逻辑表达式用最小项表示为:

D = m1+m2+m4+m7输出Co的逻辑表达式用最小项表示为:

Co = m1+m2++m3+m7由于译码器的输出为最小项取反,下面需要将表达式中的最小项转换为最小项取反的形式。根据反演定理,转换结果如下:

D = (m1’m2’m4’m7’)’;Co=(m1’m2’m3’m7’)’‘表示取反。

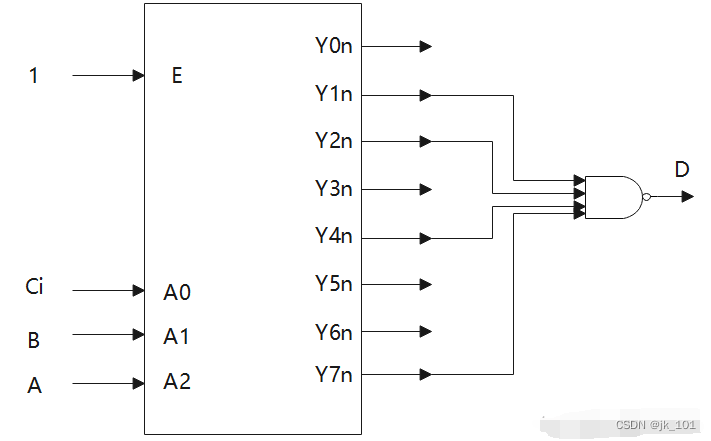

由上式可知,采用与非门即可实现该电路的组合逻辑输出。关键电路如下:

上图中D和Co的输入端来自同一各译码器。

结合电路图,将电路转换成Verilog代码描述如下:

wire Y0_n ; wire Y1_n ;wire Y2_n ;wire Y3_n ;wire Y4_n ;wire Y5_n ;wire Y6_n ;wire Y7_n ;decoder_38 U0(.E (1'b1),.A0 (Ci ),.A1 (B ),.A2 (A ),.Y0n (Y0_n), .Y1n (Y1_n),.Y2n (Y2_n),.Y3n (Y3_n),.Y4n (Y4_n),.Y5n (Y5_n),.Y6n (Y6_n),.Y7n (Y7_n));assign D = ~(Y1_n & Y2_n & Y4_n & Y7_n);assign Co = ~(Y1_n & Y2_n & Y3_n & Y7_n);参考代码

`timescale 1ns/1nsmodule decoder_38(input E ,input A0 ,input A1 ,input A2 ,output reg Y0n , output reg Y1n , output reg Y2n , output reg Y3n , output reg Y4n , output reg Y5n , output reg Y6n , output reg Y7n

);always @(*)beginif(!E)beginY0n = 1'b1;Y1n = 1'b1;Y2n = 1'b1;Y3n = 1'b1;Y4n = 1'b1;Y5n = 1'b1;Y6n = 1'b1;Y7n = 1'b1;end else begincase({A2,A1,A0})3'b000 : beginY0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b001 : beginY0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b010 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b011 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b100 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b101 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;end 3'b110 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;end 3'b111 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b0;end default: beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;endendcase end

end endmodulemodule decoder1(input A ,input B ,input Ci ,output wire D ,output wire Co

);wire Y0_n ;

wire Y1_n ;

wire Y2_n ;

wire Y3_n ;

wire Y4_n ;

wire Y5_n ;

wire Y6_n ;

wire Y7_n ;decoder_38 U0(.E (1'b1),.A0 (Ci ),.A1 (B ),.A2 (A ),.Y0n (Y0_n), .Y1n (Y1_n), .Y2n (Y2_n), .Y3n (Y3_n), .Y4n (Y4_n), .Y5n (Y5_n), .Y6n (Y6_n), .Y7n (Y7_n)

);assign D = ~(Y1_n & Y2_n & Y4_n & Y7_n);

assign Co = ~(Y1_n & Y2_n & Y3_n & Y7_n);endmodule注:解题分析来源于网友,如有侵权,请告删之。

这篇关于用3-8译码器实现全减器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!