全减器专题

[Verilog语言入门教程] Verilog 减法器 (半减器, 全减器, 加减共用)

依公知及经验整理,原创保护,禁止转载。 专栏 《元带你学Verilog》 <<<< 返回总目录 <<<< “逻辑设计是一门艺术,它需要创造力和想象力。” - 马克·张伯伦(Mark Zwolinski) 减法器是数字电路中常见的组件,用于减去两个二进制数的和。 在Verilog中,可以实现减法运算的有以下3种方式: 1. 半减器 半减器是一种简单的减法器,能够用于将两个单独

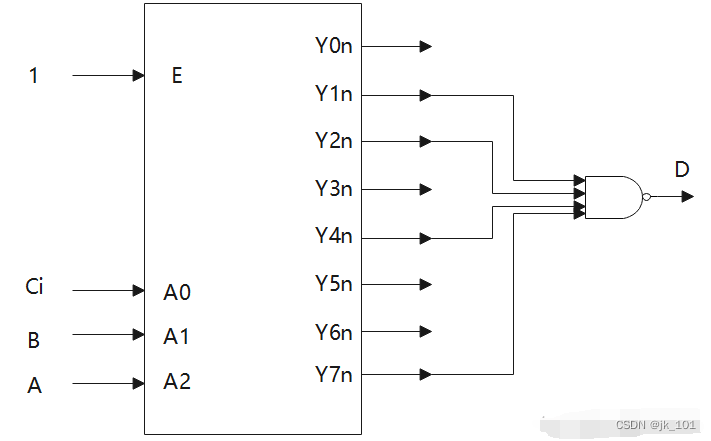

用3-8译码器实现全减器

描述 请使用3-8译码器和必要的逻辑门实现全减器,全减器接口图如下,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位。 3-8译码器代码如下,可将参考代码添加并例化到本题答案中。 module decoder_38(input E ,input A0 ,input

![[Verilog语言入门教程] Verilog 减法器 (半减器, 全减器, 加减共用)](/front/images/it_default.jpg)