本文主要是介绍基于VHDL(Verilog)语言的汉明码编码器和译码器的设计(串行设计),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

基于Verilog语言的汉明码设计,刚开始根据汉明码的原理,设计了并行的输入和clk,产生数据。

汉明码的实质及原理

汉明码实质上是个多重奇偶校验,实现原理为:在有效信息位中加入几个校验位形成汉明码,使码距比较均匀的拉大,最大的特点:具有校验并纠正一位错误的能力。

原来的设计(课程设计大部分都这么设计)

后面发现要求不对,输入信号需要自己使用m序列产生。并且采用串行的方式

总体思路:

使用m序列发生器,产生输入信号,经过串并转换为汉明码编码器的输入,得到汉明码编码。再随机产生错误,输入到汉明码译码器中,得到正确输出。经过并串转换,得到输出信号。

又仔细琢磨,对照仿真图,发现输入输出数据不一致,简单记录一下排查过程

上代码(译码部分):

always@(posedge h_clk)//同步检测

begind_shift[0]<=dataerror;d_shift[6:1]<=d_shift[5:0];if(decode_cnt==3'd6)begind_buff[6:0]<=d_shift[6:0];S2[2]<=d_buff[6]^d_buff[5]^d_buff[4]^d_buff[2];S2[1]<=d_buff[6]^d_buff[5]^d_buff[3]^d_buff[1];S2[0]<=d_buff[6]^d_buff[4]^d_buff[3]^d_buff[0];S1<=S2;if((S1&S2)!=0)decode_cnt<=3'd6;elsedecode_cnt<=3'd0; o_buff[3]<=d_buff[6]^((d_buff[6]+d_buff[5]+d_buff[4]+d_buff[2])&(d_buff[6]+d_buff[5]+d_buff[3]+d_buff[1])&(d_buff[6]+d_buff[4]+d_buff[3]+d_buff[0]));o_buff[2]<=d_buff[5]^((d_buff[6]+d_buff[5]+d_buff[4]+d_buff[2])&(d_buff[6]+d_buff[5]+d_buff[3]+d_buff[1])&(~(d_buff[6]+d_buff[4]+d_buff[3]+d_buff[0])));o_buff[1]<=d_buff[4]^((d_buff[6]+d_buff[5]+d_buff[4]+d_buff[2])&(~(d_buff[6]+d_buff[5]+d_buff[3]+d_buff[1]))&(d_buff[6]+d_buff[4]+d_buff[3]+d_buff[0]));o_buff[0]<=d_buff[3]^((~(d_buff[6]+d_buff[5]+d_buff[4]+d_buff[2]))&(d_buff[6]+d_buff[5]+d_buff[3]+d_buff[1])&(d_buff[6]+d_buff[4]+d_buff[3]+d_buff[0]));//纠错endelsedecode_cnt<=decode_cnt+3'd1;

end上仿真结果

输入和输出数据对应补上,虽然在串转并和并转串的过程中存在延时,但也不应该影响数据的输出。

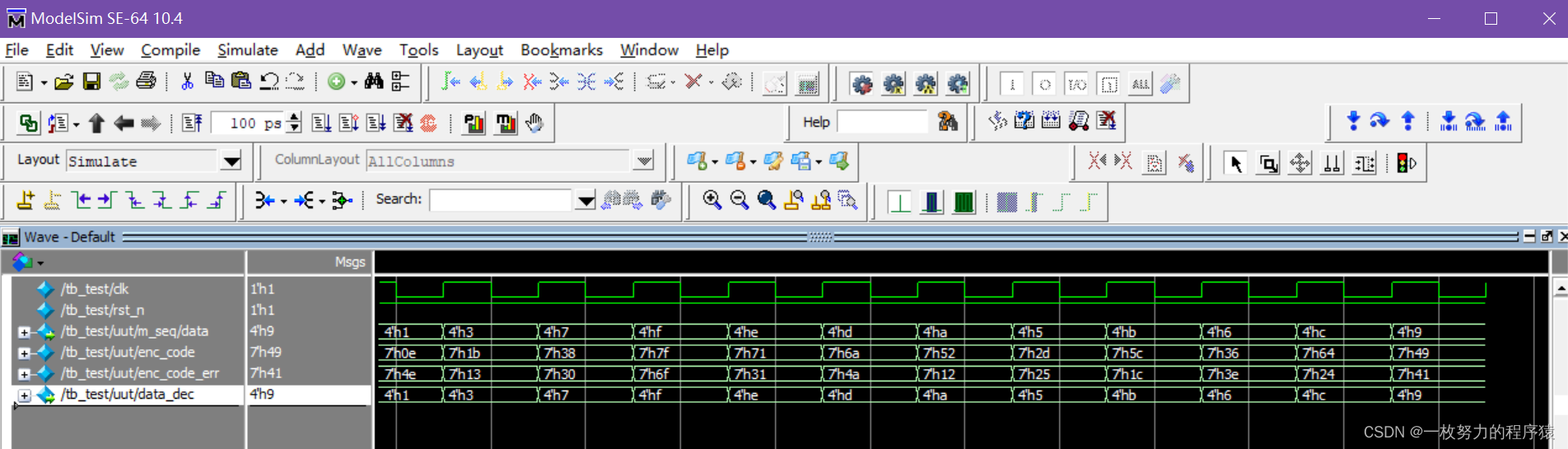

上面这个波形明显不对,后来经过大神的指点,研究了很久,重新写了代码,终于出现了正确波形,上图

输入数据和输出数据,中间都产生了一位错误,但都可以产生正确的输出,具有一位纠错功能。

关注 一枚努力的程序猿

一起学习一起成长

这篇关于基于VHDL(Verilog)语言的汉明码编码器和译码器的设计(串行设计)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!