本文主要是介绍低密度奇偶校验码LDPC(八)——QC-LDPC译码器FPGA设计概要,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

往期博文

低密度奇偶校验码LDPC(一)——概述_什么是gallager构造-CSDN博客

低密度奇偶校验码LDPC(二)——LDPC编码方法-CSDN博客

低密度奇偶校验码LDPC(三)——QC-LDPC码概述-CSDN博客

低密度奇偶校验码LDPC(四)——双对角线结构的QC-LDPC编码-CSDN博客

低密度奇偶校验码LDPC(五)——译码算法概述-CSDN博客

低密度奇偶校验码LDPC(六)——SPA和积译码算法-CSDN博客

低密度奇偶校验码LDPC(七)——SPA和积译码算法的简化-CSDN博客

QC-LDPC的FPGA实现

基于QC-LDPC编码的循环移位网络的FPGA实现_5g ldpc编码 桶形移位寄存器-CSDN博客

一、译码器的FPGA架构设计

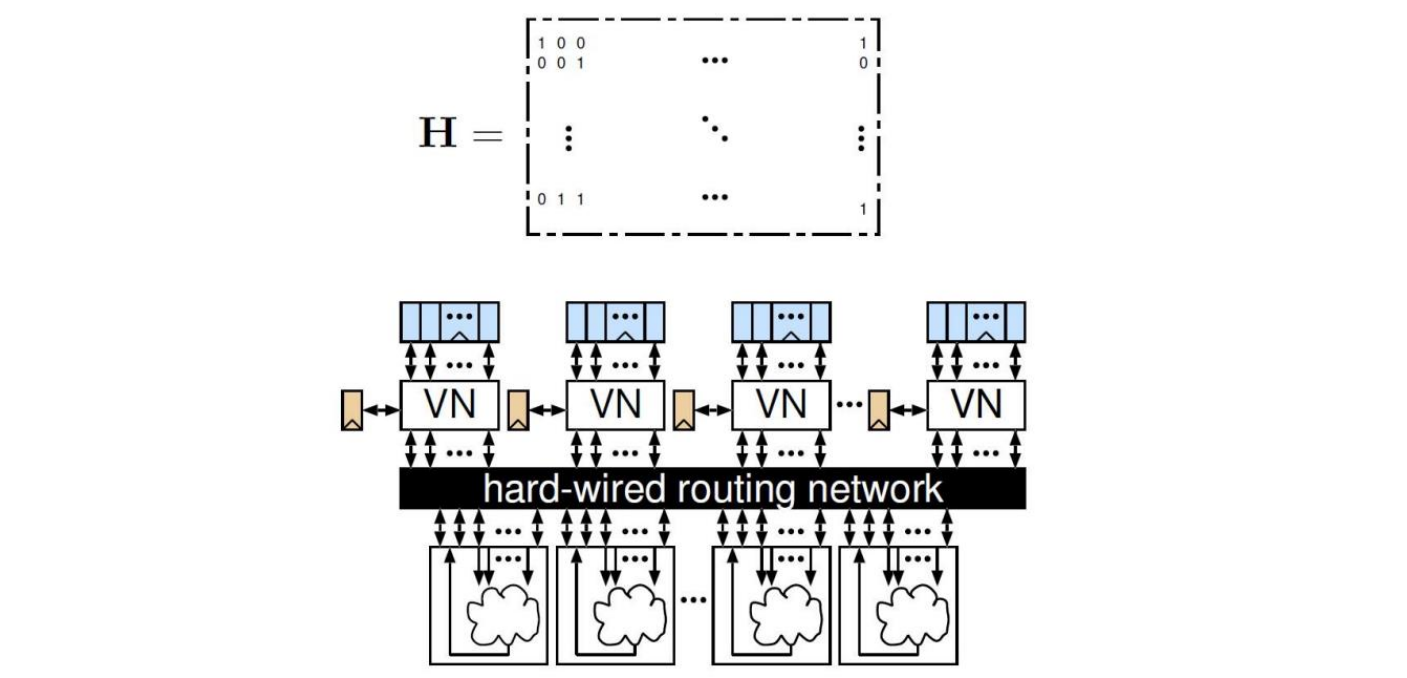

全并行(Full-Parallel Architectures)

行并行(Row-Parallel Architectures)

块并行(Block-Parallel Architectures)

参考文献

[1] 白宝明 孙韶辉 王加庆. 5G 移动通信中的信道编码[M]. 北京: 电子工业出版社, 2018.

[2] William E. Ryan, Shu Lin. Channel Codes - Classical and Modern[M]. Cambridge University Press, 2009.

[3] Roth C, Cevrero A, Studer C, et al. Area, throughput, and energy-efficiency trade-offs in the VLSI implementation of LDPC decoders[C]// IEEE International Symposium of Circuits and Systems (ISCAS). 2011: 1772-1775.

[4] 钟志伟. 面向5G编译码的硬件设计研究[C]. 南京: 东南大学, 2020.

这篇关于低密度奇偶校验码LDPC(八)——QC-LDPC译码器FPGA设计概要的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!