systemverilog专题

systemverilog、verilog的部分常用内部函数

1. $ceil 作用:将给定的实数或浮点数向上取整。示例:$ceil(3.2) 返回 4。 2. $floor 作用:将给定的实数或浮点数向下取整。示例:$floor(3.9) 返回 3。 3. $value$plusargs 作用:从命令行读取传递给仿真器的参数。格式:$value$plusargs("格式", 变量),格式 用来匹配命令行的参数,变量 是用来存储匹配到的值。示例:$

systemverilog中的DPI-C用例介绍

文章目录 前言一、dpi_longint二、dpi_packed_array三、dpi_structure四、相关参考总结 前言 本文主要基于VCS内置的三个关于DPI-C的使用用例,记录一下DPI-C的使用方法。测试用例的路径为$VCS_HOME/doc/examples/testbench/sv/。测试用例包括:dpi_longint,dpi_packed_arra

讲个SystemVerilog disable语句的坑

前言 记录个使用SystemVerilog disable语句时遇到的坑,这个坑有点反直觉,以至于我当时有点不信,觉得可能是EDA仿真工具的问题。后来查看了SystemVerilog手册和使用不同EDA工具进行验证,才慢慢接受了。结论是:SystemVerilog disable block_name或task时,会把hierarchy一致的block_name或task的线程都停掉。 正

利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

在集成电路设计的复杂世界中,验证环节是确保设计满足预期功能和性能要求的关键步骤。随着系统级芯片(SOC)和特定应用集成电路(ASIC)的规模和复杂性不断增加,传统的验证方法已经难以满足高效、准确的验证需求。因此,采用先进的验证方法学和工具变得尤为重要。 SystemVerilog(SV)和通用验证方法学(UVM)作为当前硬件验证领域的两大支柱,提供了一套完整的框架和工具,用于构建可扩展、可重用的

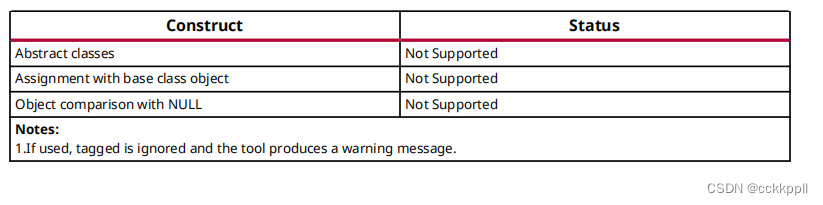

SystemVerilog Interface Class的妙用

前言 Interface Class是在SystemVerilog 2012版本中引入的,但目前在验证中几乎很少采用,大多数验证工程师要么不知道它,要么没有看到使用它的任何好处,这使得Interface Class成为一个未被充分使用和不被重视的特性。本文将举两个Interface Class的使用例子,在这些例子中,Interface Class提高了验证环境的灵活性和质量,同时进一步提高了其

基于FPGA的SystemVerilog练习

文章目录 一、认识SystemVerilogSystemVerilog的语言特性SystemVerilog的应用领域SystemVerilog的优势SystemVerilog的未来发展方向 二、流水灯代码流水灯部分testbench仿真文件 三、用systemVerilog实现超声波测距计时器测距部分led部分数码管部分采样部分顶层文件引脚绑定效果 四、SysTemVerilog与veril

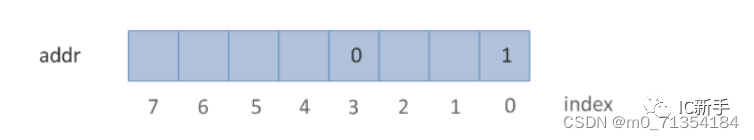

systemverilog中位的选择

常用的变量类型就是 reg 和 wire ,这两种类型可以定义 一位的变量,也可以定义多位,其中 1 bit 的变量称为 标量(scalar),多 bit 的变量称为 向量(vector),如下所示: wire o_nor; // single bit scalar netwire [7:0] o_flop; // 8-bit vect

IEEE SystemVerilog Chapter21.6:Command line input

读取文件以获得在仿真中使用的信息的替代方案是用调用仿真器的命令指定信息。该信息以可选参数的形式提供给仿真器。这些参数与其他仿真器参数的区别在于它们以加号(+)字符开头。 以下称为plusargs的这些参数可通过以下系统函数访问: $test$plusargs ( string )$value$plusargs ( user_string, variable )

systemverilog:这都不会错!!!其实很合理,提醒下自己。

这个贴子专门放一些第一眼看上去是错的代码,但是仔细看看,想想确实很合理的,提醒下自己。 1问 下面的代码好奇怪啊,这应该会报同时赋值的error吧,但是为什么通过了呢? 1答 这是明明顺序赋值,是正确的。看看这个代码 http://blog.csdn.net/tingtang13/article/details/46331283 ,里面比这个还复杂一丢丢 只不过这个

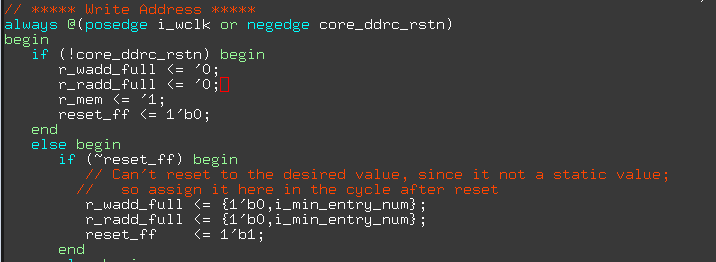

systemverilog : register value after reset must be static value

问:register 在reset之后,有时候想要是其他register的 default value ( or reset value),为什么这时候可能会有风险? 答:你怎么知道到底是哪个register的先被reset呢? 1.如果是右边的register还没有reset或者正在reset,它现在还是不稳定的值。 2.但是左边我们要赋值的regis

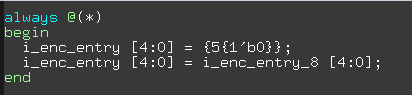

systemverilog中for循环一个多bits variable的严格正确写法与综合比较

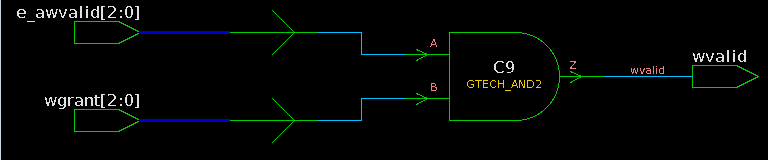

1.首先看某大厂给出的一小段代码: 这段code什么意思呢? 起初: 1)我认为是wvalid = 0; 2)下面循环的任何一次为1,就把wvalid赋值成1; 3)结果就是一旦wvalid为1,那么就永远为1,不管循环了多少次。 4)但是仔细想想,怎么会有这么vagary的逻辑呢?一定不是这样的,百思不得骑姐啊!!! 5)只好综合一下了,看下图: 原来是把

systemverilog 信号声明和仿真的关系

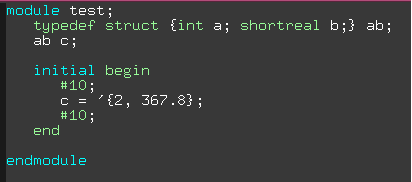

1.先看下图,先#10,后声明struct 编译器会报错,只说语法错误。 2.把信号声明放到前面两行,#10下移。 编译通过。 原因: 信号声明和信号定义,可以理解为“0”时刻,被编译器解析。但是第一个和#10有冲突,所以报错。修改后先声明,后延时,遂通过。 属于编译原理知识,那么C语言的变量声明不是这样,有一种impromptu的感觉。并不是严格要求定义在最前面,w

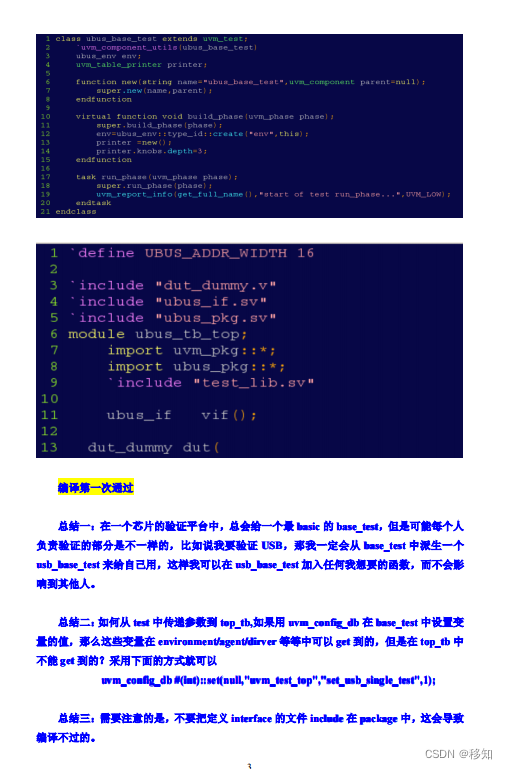

UVM基础知识4:Systemverilog 验证 12.6.1实例

来源:systemverilog验证 测试平台编写指南(书籍) 1 新建invert.c文件 vi invert.c typedef struct {unsigned char b, g, r;} *p_rgb;void invert (p_rgb rgb) {rgb->r = ~rgb->r;rgb->g = ~rgb->g;rgb->b = ~rgb->b;io_print

UVM基础知识3:Systemverilog 验证 12.2.2实例

来源:systemverilog验证 测试平台编写指南(书籍) 1 新建counter7.c文件 vi counter7.c #include<svdpi.h>#include<malloc.h>#include<veriuser.h>typedef struct {unsigned char cnt;} c7;void* counter7_new() {c7* c = (

SystemVerilog学习笔记(九)

本文思维导图如下: 1. 线程控制 1.1 并行线程 Verilog中与顺序线程begin…end相对的是并行线程fork…join。 1.1.1创建线程 SV引入了两种新新的创建线程的方法,fork…join_none和fork…join_any。 fork…join fork…join需要所有并行的线程都结束以后才会继续执行。fork…join_any fork…join

【SystemVerilog】结构体真是太好用了~

前言 Verilog最大的缺陷之一是没有数据结构。在SystemVerilog中可以使用struct创建结构,struct只是把数据组织到一起,是数据的集合,所以是可综合的。 结构体是可以通过模块接口进行传递的,这就是本文想描述的内容。 一、结构体的创建 1.1使用typedef创建新的类型 typedef语句用来创建新的类型。在veril

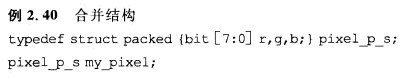

芯片验证从零开始系列(二)——SystemVerilog数据结构

芯片验证从零开始系列(二)——SystemVerilog数据结构 SystemVerilog的数据类型二值逻辑定宽数组合并数组队列关联数组数组的方法数据类型选择的经验灵活性存储量排序 自定义类型联合合并结构类型转换静态转换流操作符 枚举字符串 🔈声明: 🔑未经作者允许,禁止转载 🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈

SystemVerilog构造、包

包 包提供了一种共享不同构造的附加方式。他们的行为与VHDL包。包可以包含函数、任务、类型和枚举。的语法包是: package package_name; items endpackage : package_name 最终的package_name不是必需的,但它使代码更易于阅读。包是import命令在其他模块中引用。以下是语法: import packag

SystemVerilog Constants、Processes

SystemVerilog提供了三种类型的精化时间常数: •参数:与最初的Verilog标准相同,可以以相同的方式使用。 •localparameter:与参数类似,但不能被上层覆盖模块。 •specparam:用于指定延迟和定时值;因此,该值不是 在Vivado合成中得到支持。 还有一个名为const的运行时常量声明。 类型运算符 类型运算符允许将参数指定为数据类型,这允许模块具有

vim语法高亮---verilog/systemverilog

原文: http://www.vim.org/scripts/script.php?script_id=1586 descriptionThis script extends Verilog syntax highlighting, which comes along with Vim 6.3, and adds SystemVerilog stuff to it. It will

vcs编译systemverilog并且用verdi查看波形

转载自:http://blog.chinaaet.com/weiqi7777/p/5100017757 对于编写的systemverilog代码,在linux下,可以使用vcs编译,但是编译的时候,要注意,要加入几个选项。 整个过程,linux使用的是64位的redhat,vcs使用的是vcs2015,verdi使用的是verdi2015。如以下的systemverilog代码。

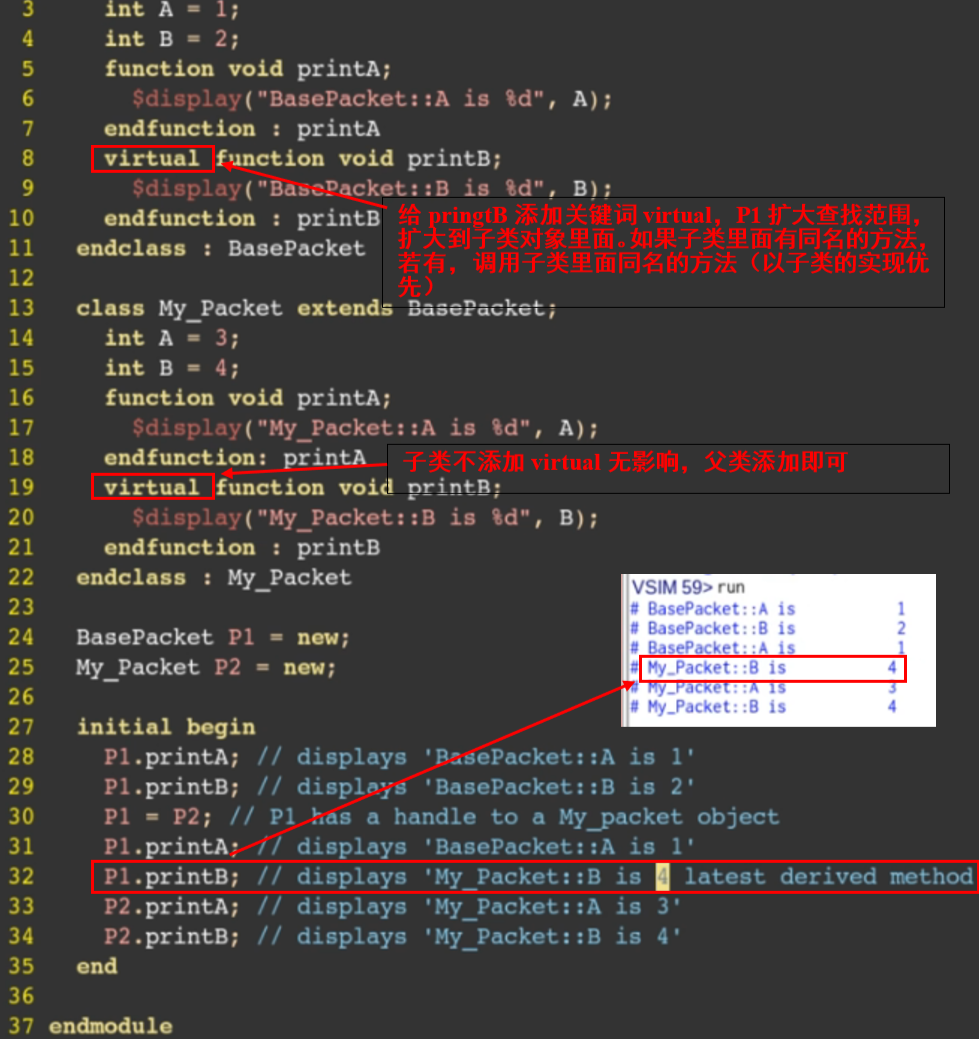

虚方法——systemverilog,SV

引言 类的继承是继承父类的成员变量和成员方法。默认情况下,子类覆盖的方法并不会继承父类的同名方法,只有通过super.method()的方式显式执行,才会达到继承父类方法的效果。 默认情况下,子类中重写的方法对父类是不可见的。子类对象中,即有从父类继承而来的,也有子类扩展的方法和变量。而子类所扩展的方法默认对父类是不可见的。 要想子类重写父类的方法能被父类看到,那就需要虚方法。虚方法就是一个基本

对象拷贝——systemverilog

使用场景 当需要赋值一个对象,以防止对象的方法修改原始对象的值,或者在一个发生器中保留约束时,可以对对象做拷贝 1.使用new操作符赋值 new操作符会创建了一个新的对象,并且复制了现有对象的所有变量,但是不会调用已经定义的任何new()函数。 class Transaction;bit[31:0] addr,crc,data[8];Statistic stas;//指向Statistic

定义交叉覆盖率技巧——systemverilog

2022/03/18 此文章结论不正确。 纠正:当你在coverpoint中自己建仓了(设置了bin),系统就不会再自动建仓,覆盖率数值限制在你设置bin值得范围。 引言 定义两个coverpoint a,b,如果cross a和b,假定a中有4个bin,b中有5个bin,cross之后一定有20个bin吗? 不一定。如果a中的bin没有将所有可能的值涵盖完,那么系统会分配默认的bin,那么

枚举类型enum——systemverilog

enum的基础语法 enum提供方法来描述抽象变量的合法值范围,其每个值都需要提供一个用户自定义的名字 enum{red,green.blue} RGB; // RGB是一个枚举类型变量// red,green.blue是枚举常量 枚举数据默认(缺省类型)的存储类型为int型(32位有符号二值逻辑),且数值从0开始递增 。 枚举类型也可以直接赋初值 enum logic [2:0

二值逻辑和四值逻辑——systemverilog

systemverilog中常用的数据类型 SV中引入了二值逻辑(取值0和1)的变量,这样可以减小仿真时的内存消耗。 类型数据类型四值逻辑integer logic reg net-type(如 wire 和 tri )二值逻辑bit byte shortint int longint无符号位logic bit reg net-type(如 wire 和 tri )有符号位byte(8bit)