本文主要是介绍systemverilog : register value after reset must be static value,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

问:register 在reset之后,有时候想要是其他register的 default value ( or reset value),为什么这时候可能会有风险?

答:你怎么知道到底是哪个register的先被reset呢?

1.如果是右边的register还没有reset或者正在reset,它现在还是不稳定的值。

2.但是左边我们要赋值的register已经reset,那他岂不是得到了一个不稳定的值。

3.所以LRM上是这么教导我们的,reset赋值要给 “static”,也就是一个干干净净,老老实实的数。

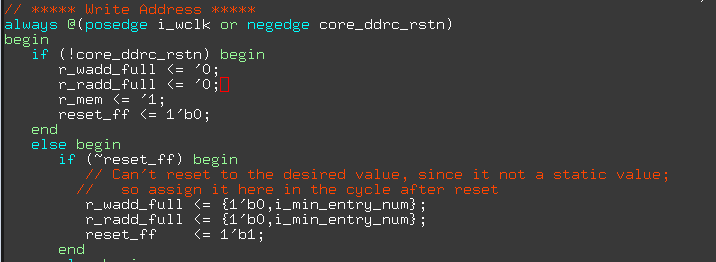

4.在reset的下一拍在把左边的register赋值成它要的右边register的value。如下图:

reset_ff 就是reset的edge。其实如果做的不规范,nLint 或 综合也应该能检查出来吧,我没试过哦。

这篇关于systemverilog : register value after reset must be static value的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!