本文主要是介绍systemverilog中for循环一个多bits variable的严格正确写法与综合比较,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

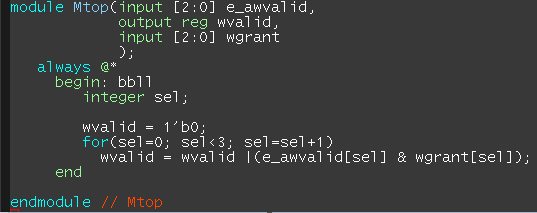

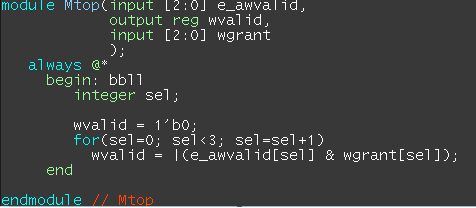

1.首先看某大厂给出的一小段代码:

这段code什么意思呢?

起初:

1)我认为是wvalid = 0;

2)下面循环的任何一次为1,就把wvalid赋值成1;

3)结果就是一旦wvalid为1,那么就永远为1,不管循环了多少次。

4)但是仔细想想,怎么会有这么vagary的逻辑呢?一定不是这样的,百思不得骑姐啊!!!

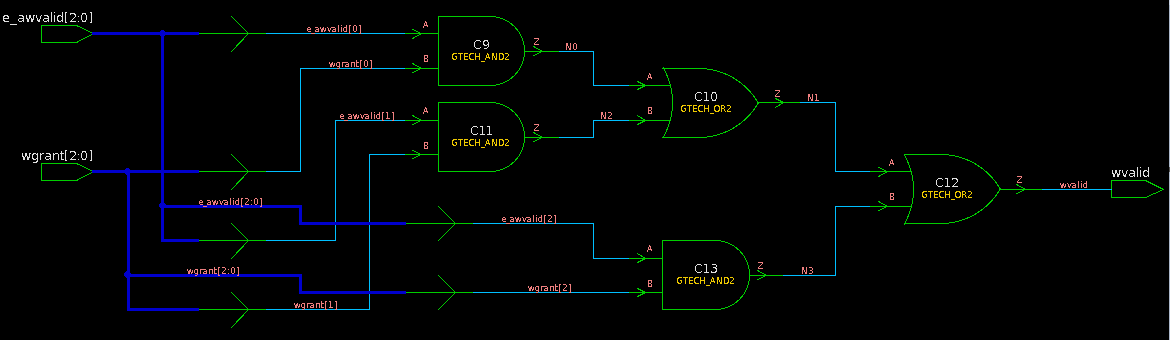

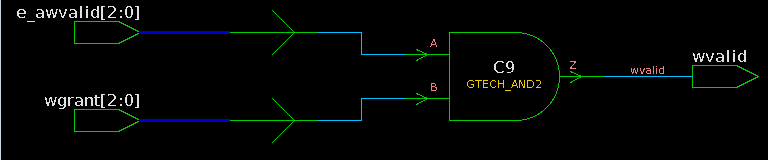

5)只好综合一下了,看下图:

原来是把各个对应位作AND,然后在把所有AND结果做OR(或者说和上一次循环的结果做OR),这样就舒服多了。有点像C 语言的a +=1 这种感觉。

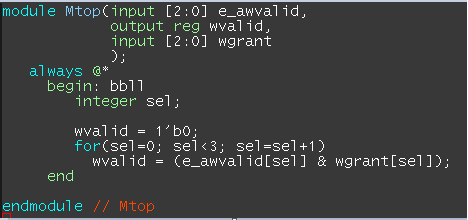

2.那如果去掉每次 “或wvalid” ,改成下面这样会怎么样呢?

可以预想一下,3bits 的结果怎么可能赋值给1 bit 的wvalid?直观上就是有问题的,但还是看看结果吧。

果不其然,这是个啥???至少我不确定,感觉很不稳妥。

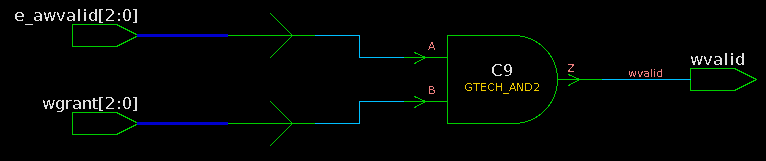

3.那在上面的基础上继续修改,既然上面不行,那就在前面加上一个 “ | ”,好多代码都是这么写的,感觉这样应该可以,嗯,只是感觉。

毕竟我是把 3bits variable 取或,自信满满哒,看下结果吧。

炸裂!!!居然和想象的不一样(综合的时候要有output,否则会优化掉,什么也看不到,居然会犯这种错误)。

不要问我为什么,我也不知道!

1)也许这就是客观世界存在,不需要原因。

2)也许这是vendor的问题,版本不一样。或者别人家的tools会不一样

3)也许是综合的时候加上某个command 会 enable 某个feather吧,但是我不知道哦。

总之呢,就严格按照第1种方法写就好了,其他的就不用考虑了。

这篇关于systemverilog中for循环一个多bits variable的严格正确写法与综合比较的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!