本文主要是介绍systemverilog 信号声明和仿真的关系,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

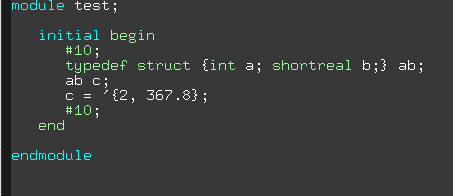

1.先看下图,先#10,后声明struct

编译器会报错,只说语法错误。

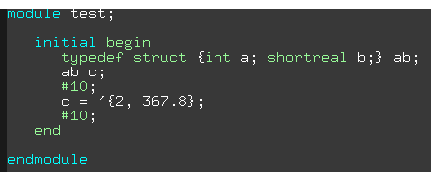

2.把信号声明放到前面两行,#10下移。

编译通过。

原因:

信号声明和信号定义,可以理解为“0”时刻,被编译器解析。但是第一个和#10有冲突,所以报错。修改后先声明,后延时,遂通过。

属于编译原理知识,那么C语言的变量声明不是这样,有一种impromptu的感觉。并不是严格要求定义在最前面,why?据说老的编译器也会报错,后来改了。。。。

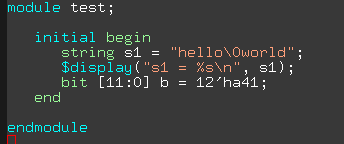

3.同样下面的片段也是有问题的,因为在display之后又有新的信号声明。原因:display已经开始仿真,但是要求在仿真之前compiler吃掉所有的signal declaration,在后面又有当然error撒!!!

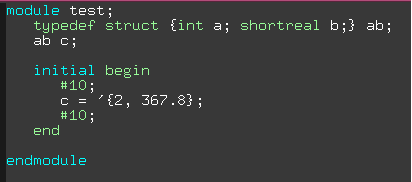

4.但是最严格的定义应该是下面这样,声明在initial 外面

这样想delay就delay咯!!!!

这篇关于systemverilog 信号声明和仿真的关系的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!