ddr3专题

【转】DDR3中的ODT

ODT是什么鬼?为什么要用ODT?在很多关于DDR3的博文和介绍中都没有将清楚。在查阅了很多资料并仔细阅读DDR3的官方标准(JESD79-3A)之后,总算有点了头绪,下面来整理整理。 1、首先ODT是什么? ODT(On-Die Termination),是从DDR2 SDRAM时代开始新增的功能。其允许用户通过读写MR1寄存器,来控制DDR3 SDRAM中内部的终端电阻的连接或者断开。在D

ddr3 vivado 设计

目录 一、如何知道器件所支持的时钟频率? 1.1DDR3芯片的带宽、位宽和最大IO时钟频率 1.3FPGA所支持的最大频率 二、时钟结构 三、MIG IP核的时钟: 3.1clock period时钟 3.2 ui_clk 3.3 input clock period 3.4 Reference clock 四、行业术语 一、如何知道器件所支持的时钟频率? 举例说明:

Spartan6 FPGA DDR3 IP核调试及程序示例

Spartan6 FPGA芯片中集成了MCB硬核,它可以支持到DDR3。在ISE中提供了MIG IP核,可以用它来生成 DDR3 控制器,并通过 MIG 的 GUI 图形界面完成相关配置。可以参照其官方datasheet查看其用法--UG388MCB模块信号和架构框图如图3所示,了解内部框图有助于梳理IP核的逻辑架构,更好的完成用户端的逻辑设计。IP核将Memory的控制已经做好并封装起来,提供了

『FPGA通信接口』DDR(4)DDR3内存条SODIMMs读写测试

文章目录 前言1.MIG IP核配置2.测试程序3.DDR应用4.传送门 前言 不论是DDR3颗粒还是DDR3内存条,xilinx都是通过MIG IP核实现FPGA与DDR的读写。本文区别于DDR颗粒,记录几个与颗粒配置不同的地方。关于DDR的原理与MIG IP的简介,请查看前面文章,链接在文末。本文提供了配套的工程源码,链接在文末,本文用的内存条为MT16KTF1G64HZ

【专篇】DDR3 SDRAM-01总体介绍

概念 DDR3 SDRAM(Double-Data-Rate 3 Synchronous Dynamic Random-Access Memory,第三代双倍速率同步动态随机存取存储器)是计算机存储技术的一种重要进步,它在前代DDR2 SDRAM的基础上进行了多项改进和优化。以下是DDR3 SDRAM的特点介绍: 双倍速率(DDR):DDR3 SDRAM采用双倍速率数据传输技术,即在每个

DDR3的DQS_p/n信号电平摆幅变化不一致现象

环境: zynq7100, MT41J64M16 现象: (1) 处理器读DDR3的操作,DQS_p/n信号与DQn信号一道,由DDR3发出,处理器接收。 测量发现,DQS信号电平摆幅低低高高的现象,摆幅高时能达到正常摆幅要求,低时只是正常摆幅的一半左右。 (2) 处理器写DDR3的操作,DQS_p/n与DQn一道,由处理器发出,DDR3接收。 测量信号正常,DQS信号差分摆幅一

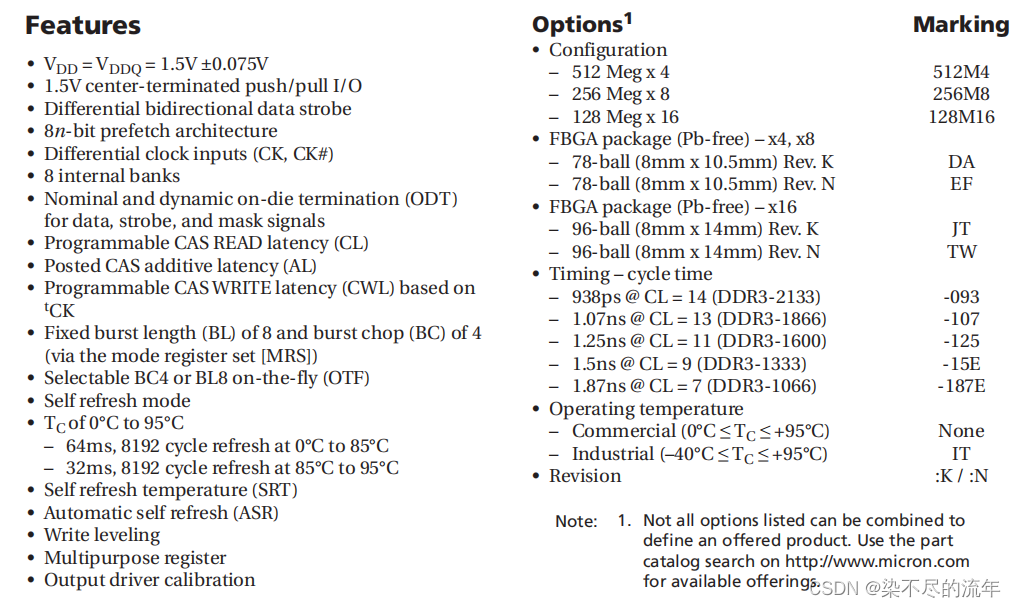

『FPGA通信接口』DDR(3)DDR3颗粒读写测试

文章目录 前言1.配套工程简介2.测试内容与策略3. 测试程序分析4.程序结果分析5.一个IP控制两颗DDR36.传送门 前言 以四颗MT41K512M16HA-125AIT颗粒为例,介绍如何在一块新制板卡上做关于DDR3的器件测试。前面两篇介绍了什么是DDR,并介绍了xilinx给出的FPGA与DDR完美结合的方案MIG IP核,请按照顺序阅读DDR相关文章,链接在文末。D

Xilinx Kintex-7系列XC7K410T-FFG900外设之DDR3硬件设计

引言:基于K7+C665x为核心的电路板中用到了DDR3存储芯片,现将FPGA外接DDR3时硬件设计中的一些心得做一个简单的分享。 1. DDR3与K7-410T互联设计 在数据速率带宽约束方面,DDR3运行速度受限于其与K7-410T FPGA互联的I/O Bank 管脚以及FPGA器件的速度等级。如下表所示,当FPGA选定时,如需DDR3运行最大工作频率时,需要将DDR3互联至FPGA的H

Zedboard 如何从PL端控制DDR3(二)--AXI4总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的。 AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3

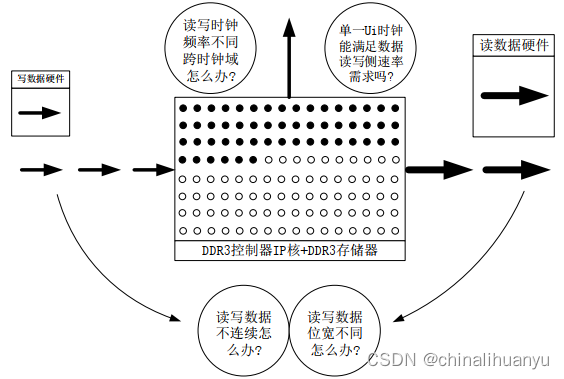

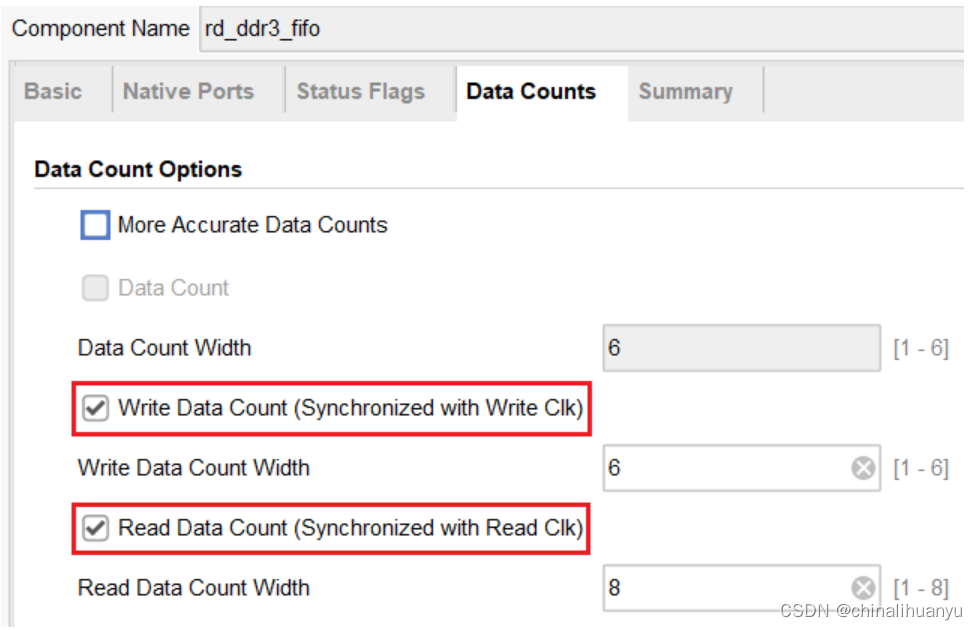

将Xilinx DDR3 MIG IP核的AXI_FULL接口封装成FIFO接口(含源码)

MIG IP除了支持前文讲解的APP接口,还支持axi_full接口,因此本文使用MIG IP的axi_full接口封装为FIFO接口,取代以太网传输图片工程中的DDR3读写控制模块。 回顾前文APP接口的DDR3读写控制模块,框图如下所示,本文需要将MIG IP的APP接口更换为axi_full接口时序,从而ddr3_rw模块需要重新设计。 图1 DDR3读写控制模块

FPGA——DDR3的IP核

FPGA——DDR3的ip核 IP核配置基于MIG核代码基于AXI接口的DDR3 IP核配置 1 2 3 4 5 6 基于MIG核代码 控制MIG核的信号进行读写 module MIG_APP_Drive(input i_ui_clk ,input i_ui_rst

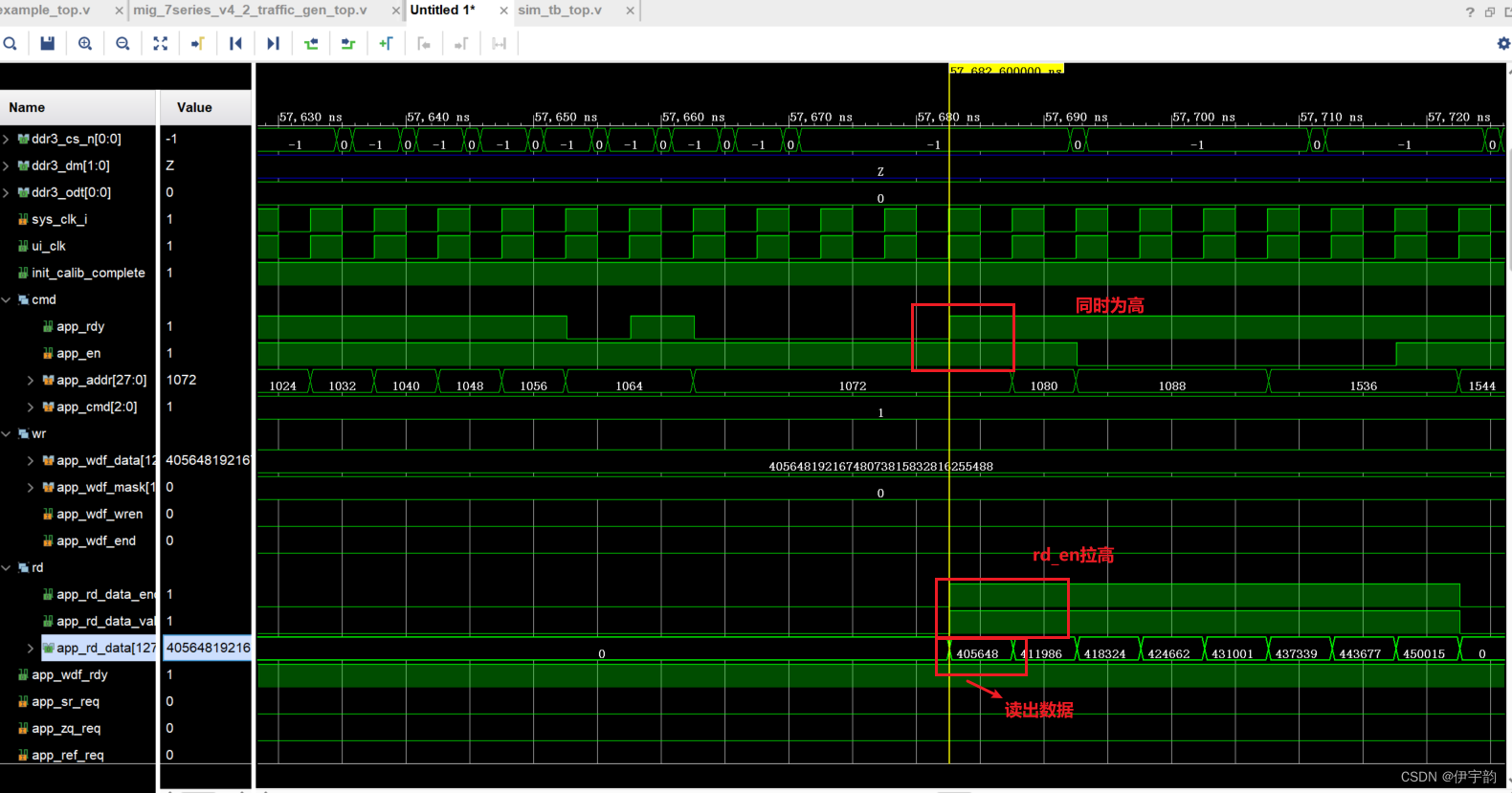

Verilog 入门之ddr3读写遇到的那些坑!(新人报道

FPGA ddr3 踩过的那些坑!(流泪 1.从另一个模块中请求数据的时候,一般间隔一个周期再采集数据。(因为另一个模块在这周期收到数据请求,在下一个周期才能给出数据) 例如图中在3519-3520时间段内,wr_burst_req拉高,向用户请求数据,而有效的数据是从3520时刻才开始的,相当于滞后一周期,相应地,数据通道的使能也应滞后一周期打开,如图中app_wdf_wren和ap

DDR3 APP接口的两种时序写法

写法一: 1.当写数据FIFO内的数值达到一次burst事件的需求的时候,进行请求; 2.请求通过仲裁器传递到写模块,启动写; 3.完成写操作以后地址增加这一整个burst的便宜了; 读操作和写操作类似,仅把FIFO的请求规则改换即可; 写法二: 1.创建命令FIFO CMD FIFO; 2.每当写数据时,利用写数据使能来增加计数器; 3.每当计数器来到一次burst事件的总需求的

从内部结构分析DDR2到DDR3的变化及DDR3原理图分析

1、概述 内存的升级都是为容量和读写速度服务的,每次升级无疑会使容量、读写速度增加、功耗降低,从而引起的一些硬件和时序变化。 从SDRAM芯片内部结构分析其原理,从内部结构讲解SDRAM与DDR的变化,从内部结构讲解DDR到DDR2的变化。 下图列出了从SDRAM到DDR3每代内存的时钟频率范围和预取长度,SDRAM内核时钟频率和接口时钟频率一致,在每个时钟的上升沿传输数据,不需

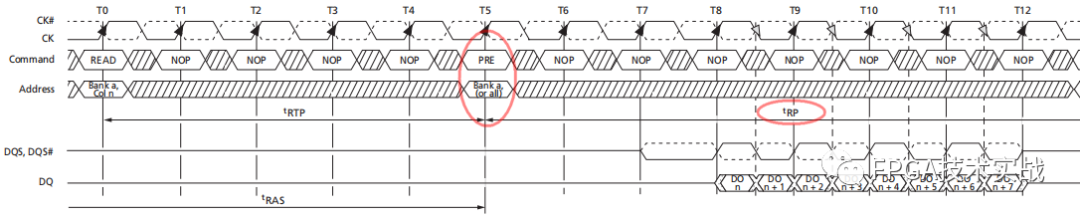

【FPGA】DDR3学习笔记(一)丨SDRAM原理详解

本篇文章包含的内容 一、DDR3简介1.1 DDR3 SDRAM概述1.2 SDRAM的基础结构 二、 SDRAM操作时序2.1 SDRAM操作指令2.2 模式寄存器(LOAD MODE REGISTER)2.3 SDRAM操作时序示例2.3.1 SDRAM初始化时序2.3.2 突发读时序2.3.3 随机读时序2.3.4 突发写时序2.3.5 随机写时序2.3.6 写-写时序2.3.7 写-

FPGA DDR3简介及时序

一,DDR3基础知识 1、DDR3全称第三代双倍速率同步动态随机存储器。 特点:①掉电无法保存数据,需要周期性的刷新。 ②时钟上升沿和下降沿都会传输数据。 ③突发传输,突发长度Burst Length一般为8 2、DDR3的存储: bank、行地址和列地址 数据怎么存入到DDR3:先指定一个Bank地址,再指定行地址,最后指定列地址。 DDR3容量计算

DDR3和DDR2和DDR的工作原理及技术区别

DDR2与DDR的区别 (1)DDR的定义: 严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,部分初学者也常看到DDR SDRAM,就认为是SDRAM。DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系。 SDRAM在一个时钟周期内只传输

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(前导)

ACM9238 高速双通道ADC模块自助服务手册AD9238 Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一)-CSDN博客 一、AD9238 模块在各方面参数性能上与AD9226保持一致。但是在设计上优化了信号调理电路,将单端信号先转成差分信号,再送入ADC转换,已获得更小的采样误差。 功能参数 1、±5V电压输入范围 2、每通道65Msps最高采样速率 3

Zynq—AD9238数据采集DDR3缓存千兆以太网发送实验(一)

ACM9238 高速双通道ADC模块自助服务手册AD9238 一、实验目的 本次实验通过电脑上的网络调试助手,将命令帧进行发送,然后通过ACZ7015开发板上的以太网芯片接收,随后将接收到的数据转换成命令,从而实现对ACM9238模块采样频率、数据采样个数以及采样通道的配置。配置完成之后,ACM9238模块开始采集数据,将采集的数据存储至ddr中,然后通过网口以UDP协议传输到电脑

zynq7000 PL读写DDR3----实验笔记

环境:vivado2018.3 芯片: xc7z100ffg900-2 本实验参考资料主要来源:https://www.eefocus.com/antaur/blog/17-08/423773_0818c.html 实验目的:将ADC接收的数据先存入DDR3,待PS端读取完成后,再存入一批。 1、工程规划 DDR芯片的管脚是绑定到Zynq的DDR接口上的。 而Zynq系统的

vivado下ddr3的读写和测试详解

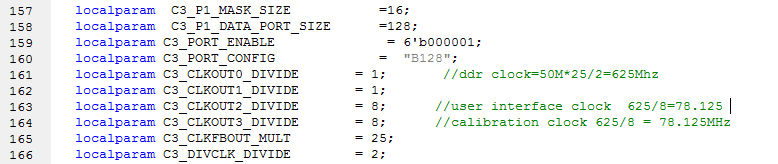

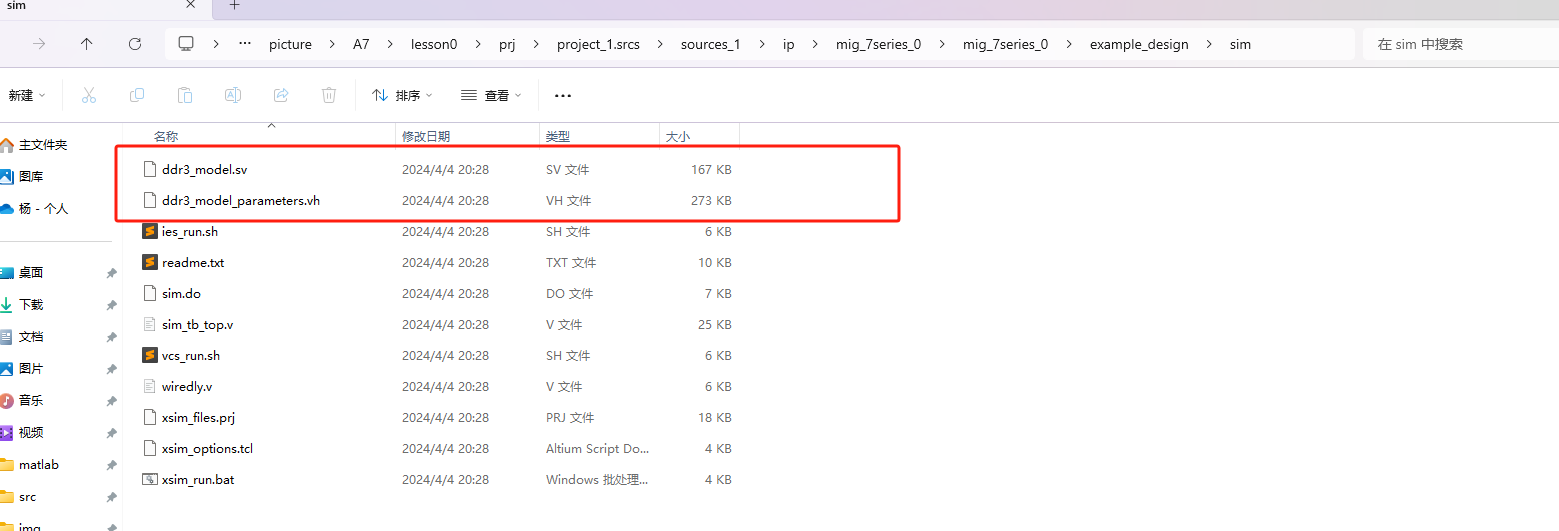

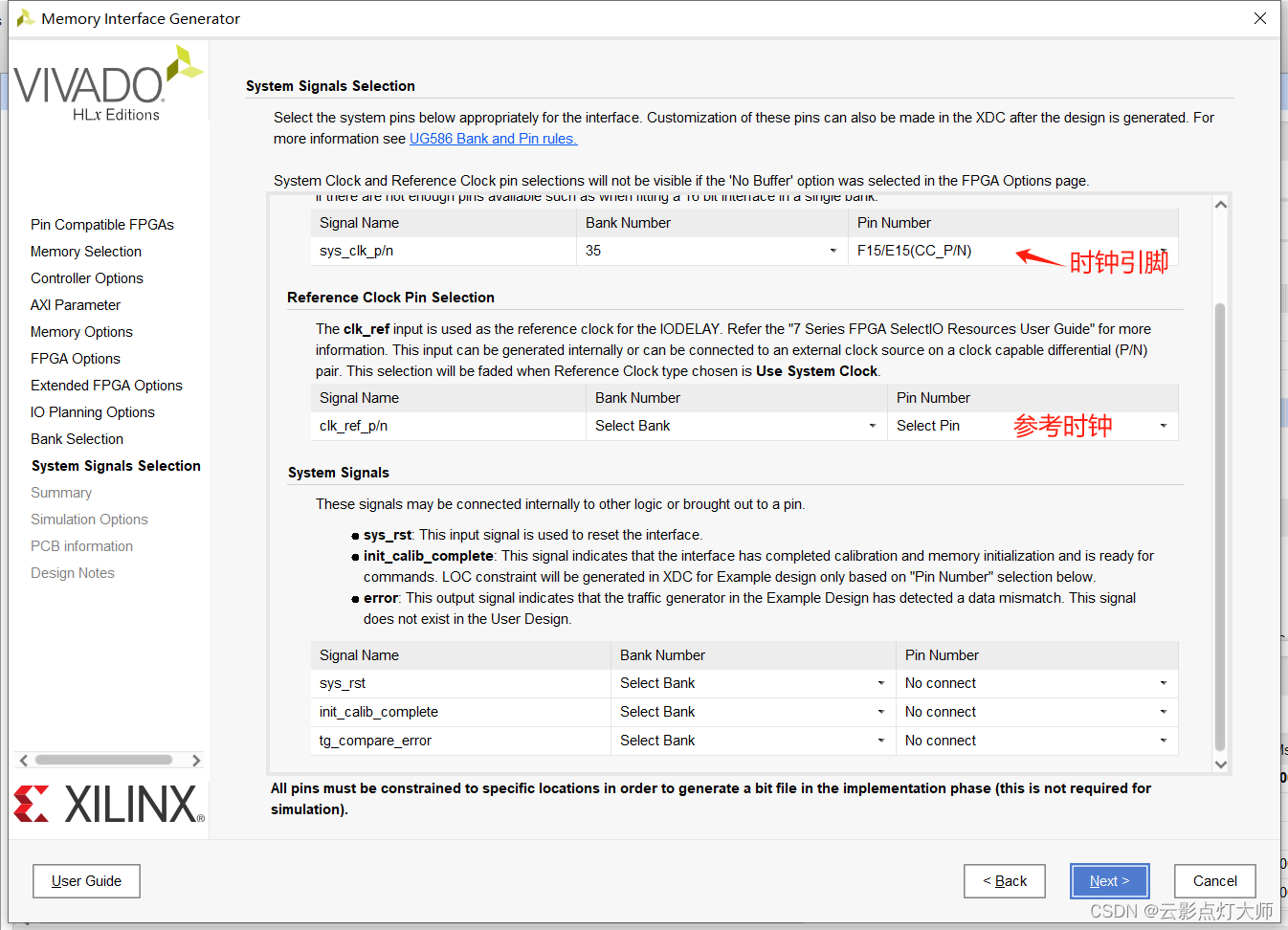

最近博主在根据例程做ddr3的读写测试,发现根本看不到好吧,虽然之前博主做过SDRAM的读写测试,但是ddr3更加复杂,时序写起来很吃力,所以需要用到vivado下自带的ip核。具体来看下面例化过程: 1.在ip核下搜索mig 双击打开 2.直接next 然后在当前界面修改你的ddr3ip核的名字 这里博主是因为已经例化了ip核,所以名字不能修改,然后next 3.这是要不要兼容

DDR3通信协议介绍篇

一.DDR3简介 DDR核心技术点就在于:(1)双沿传输。(2)预取prefetch. DDR的频率:(1)核心频率 (2)时钟频率 (3)数据传输频率;核心频率就是内存的工作频率;DDR1内存的核心频率是和时钟频率相同的,到了DDR2和DDR3时才有了时钟频率的概念,就是将核心频率通过倍频技术得到的一个频率。数据传输频率就是传输数据的频率。DDR1预读取是2

vivado下ddr3的读写和测试详解

最近博主在根据例程做ddr3的读写测试,发现根本看不到好吧,虽然之前博主做过SDRAM的读写测试,但是ddr3更加复杂,时序写起来很吃力,所以需要用到vivado下自带的ip核。具体来看下面例化过程: 1.在ip核下搜索mig 双击打开 2.直接next 然后在当前界面修改你的ddr3ip核的名字 这里博主是因为已经例化了ip核,所以名字不能修改,然后next 3.这是要不要兼容