本文主要是介绍【转】DDR3中的ODT,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

ODT是什么鬼?为什么要用ODT?在很多关于DDR3的博文和介绍中都没有将清楚。在查阅了很多资料并仔细阅读DDR3的官方标准(JESD79-3A)之后,总算有点了头绪,下面来整理整理。

1、首先ODT是什么?

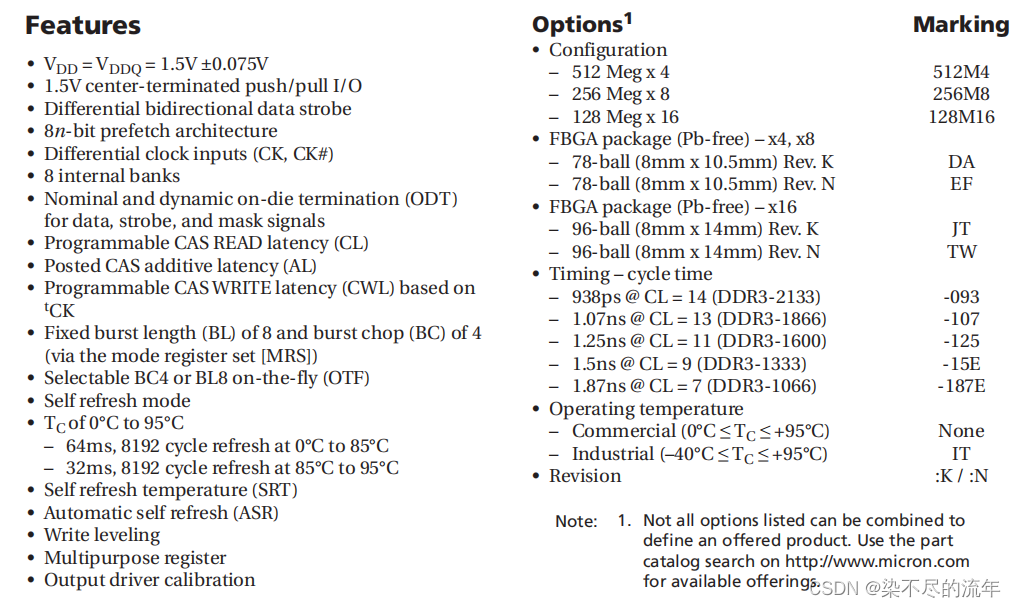

ODT(On-Die Termination),是从DDR2 SDRAM时代开始新增的功能。其允许用户通过读写MR1寄存器,来控制DDR3 SDRAM中内部的终端电阻的连接或者断开。在DDR3 SDRAM中,ODT功能主要应用于:

·DQ, DQS, DQS# and DM for x4 configuration

·DQ, DQS, DQS#, DM, TDQS and TDQS# for X8 configuration

·DQU, DQL, DQSU, DQSU#, DQSL, DQSL#, DMU and DML for X16 configuration

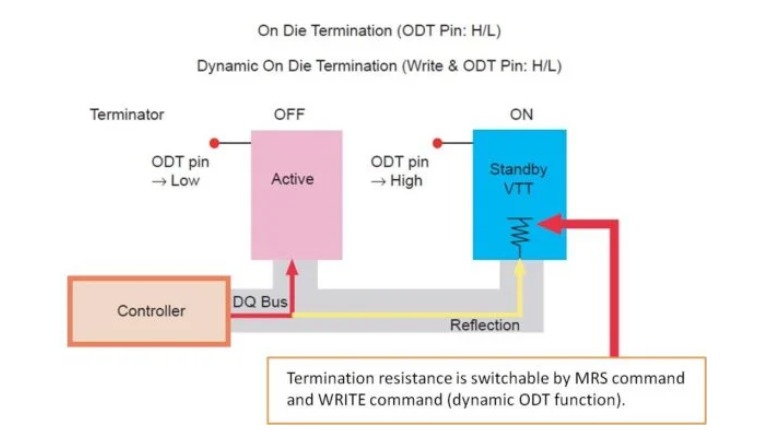

具体的结构图如下:

2、为什么要用ODT?

一个DDR通道,通常会挂接多个Rank,这些Rank的数据线、地址线等等都是共用;数据信号也就依次传递到每个Rank,到达线路末端的时候,波形会有反射(有兴趣的去啃几口《信号完整性分析》的书吧,个人表示好难),从而影响到原始信号;因此需要加上终端电阻,吸收余波。之前的DDR,终端电阻做在板子上,但是因为种种原因,效果不是太好,到了DDR2,把终端电阻做到了DDR颗粒内部,也就称为On Die Termination,Die上的终端电阻,Die是硅片的意思,这里也就是DDR颗粒。

所以,使用ODT的目的很简单,是为了让DQS、RDQS、DQ和DM信号在终结电阻处消耗完,防止这些信号在电路上形成反射,进而增强信号完整性。用JESD79-3A的原话就是:

The ODT feature is designed to improve signal integrity of the memory channel by allowing the DRAM controller to independently turn on/off termination resistance for any or all DRAM devices.

总的来说,ODT技术的优势非常明显。

第一,去掉了主板上的终结电阻器等电器元件,这样会大大降低主板的制造成本,并且也使主板的设计更加简洁。

第二,由于它可以迅速的开启和关闭空闲的内存芯片,在很大程度上减少了内存闲置时的功率消耗。

第三,芯片内部终结也要比主板终结更及时有效,从而减少了内存的延迟等待时间。这也使得进一步提高DDR2内存的工作频率成为可能。

3、DDR3中的ODT

3.1、ODT的开启

The ODT Mode is enabled if any of MR1 {A9, A6, A2} or MR2 {A10, A9} are non zero.

3.2、ODT的关闭

The ODT pin will be ignored if the Mode Registers MR1 and MR2 are programmed to disable ODT and in self-refresh mode.

3.3、ODT阻值的选择

ODT的阻值可以通关配置MR1寄存器的 {A9, A6, A2} 进行修改

这篇关于【转】DDR3中的ODT的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!