本文主要是介绍什么是On-die Termination(ODT,片上端接),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在深入研究“片上端接”之前,让我们先了解一下“端接”的概念。为什么需要“端接”?

高速的数据传输速率和实时功能是电子设备的目标。这些共同的目标推动了电子设备不仅需要高速运行,而且还需要提供快速响应和实时性能,以满足各种应用和行业用户的需求。更高的传输速度、更低的上升时间和更长的传输线成为保持从发射器到接收器的信号完整性的巨大挑战。

确保信号完整性是一项重大挑战,因为我们的目标是更高的传输速度、减少信号的上升-下降时间以及更长的发射器和接收器之间的传输线。

因此,确定适当的端接技术来端接信号线非常重要,这样才能保持信号的完整性。

信号完整性在高速数字系统中的重要性

随着设计迁移到更长的传输线长度上和更高的数据传输速率上,信号完整性变得越来越重要,因为它直接影响电子设备的性能、可靠性以及能效。

“信号完整性定义了通过传输线的信号的质量。它表示信号能够从发射机传播到接收机而不会失真“。所有高速互连都是传输线,需要最大限度地减少信号失真、串扰和电磁辐射。

信号端接简介

在传输线下端接阻抗非常重要。端接技术通过最大限度地减少信号反射、防止数据损坏和确保传输线上的可靠通信来保持信号完整性。在高速设计中,信号以更快的速度传播并遇到更显著的阻抗变化,有效端接有助于缓解“信号失真、过冲和下冲”等问题。

通过匹配线路阻抗并正确端接传输线,可以减少信号反射、优化通信通道的性能。这在高速数据网络、电信系统和高性能计算环境下尤为重要。

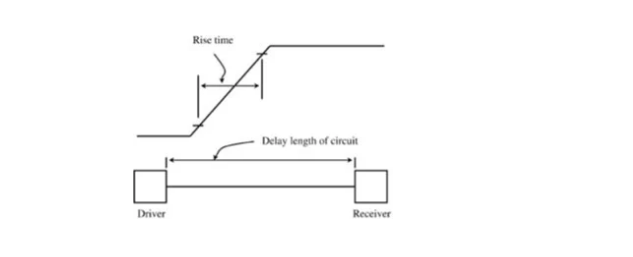

经验法则指出,“当PCB走线的单向传播延迟等于或大于所施加信号上升/下降时间的一半时,应端接传输线到其特性阻抗”

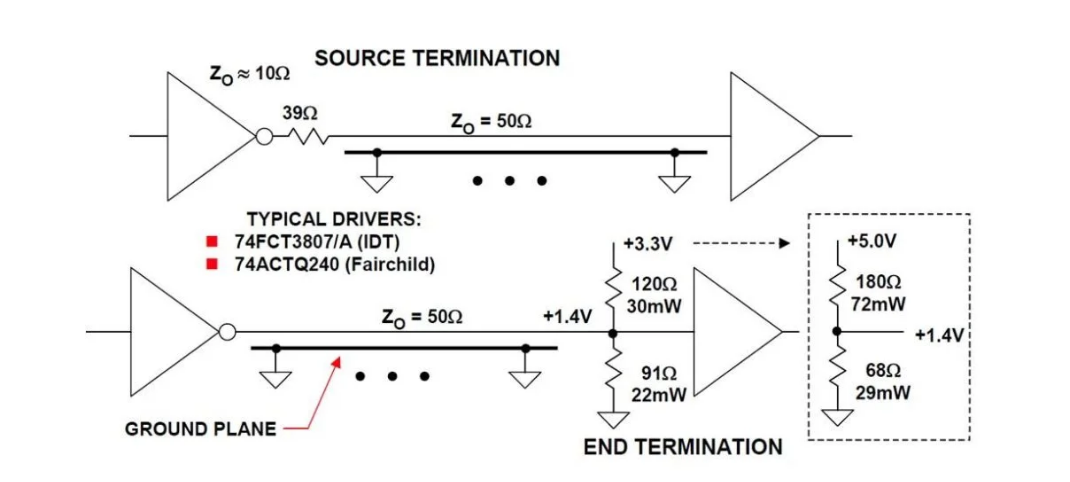

源端(source )端接方法涉及在源端端接传输线,如下图所示。这种方法通过采用与传输线相等的阻抗匹配来有效地吸收反射波形。在本例中,这需要大约39 Ω串联电阻,驱动器的内部输出阻抗通常约为10 Ω(ZO≈10Ω+串联端接电阻39 Ω= 特性阻抗为50 Ω)。

同样,末端(end)端接方法涉及在传输线的末端端接。

在上面的例子中,我们可以看到这些端接电阻被放置在PCB上。当在集成电路或芯片外部实现的端接方法时,这种类型的实现称为“片外端接”“OFF Chip Termination”。

On Die Terminations特性

端接输入信号:片上端接 (ODT) 通过匹配传输线的特性阻抗来端接输入信号。这对于防止可能降低信号质量的信号反射至关重要。通过正确端接信号,可以保持通信的完整性。

节省空间:片上端接 (ODT) 直接在集成电路 (IC) 芯片上实现,无需外部分立元件(如电阻器)。这样可以节省电路板上的空间。

降低成本:片上端接 (ODT) 无需额外的外部组件,有助于降低成本。当考虑到量产时,成本就是很关键的考虑因素了。

接收模式:片上端接 (ODT) 在接收模式下可用,它有助于端接输入信号以防止反射。

双向模式:在双向模式下,输入和输出信号均可采用片上端接 (ODT)。当 I/O(输入/输出)是双向的时,这一点尤其重要。

在DDR SDRAM 等存储器接口中,片上端接(ODT)通常用于匹配传输线阻抗并优化数据传输过程中的信号完整性。

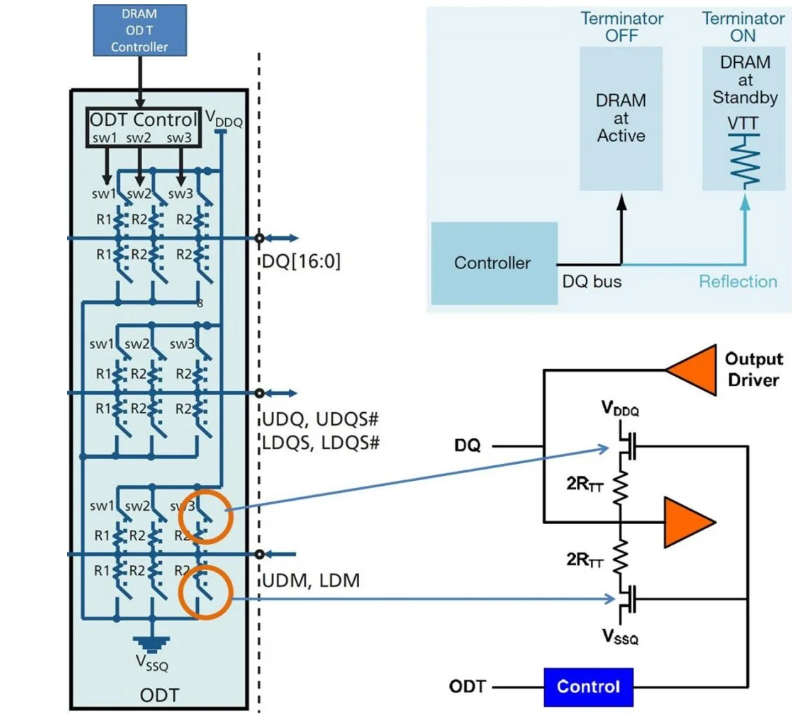

DRAM中的片上端接

DRAM(DDR2/DDR3/DDR4/DDR5)技术能够以比以前更高的速率传输数据,需要一些手段来增强数据总线的信号完整性,同时仍保持性能。下图描绘了具有片上端接 (ODT) 功能的 DRAM I/O driver,简化电路如下图所示,以便更好地理解。

片上端接(ODT)允许DRAM根据需要打开/关闭每个接口信号线的端接电阻和相关电路,从而增强了内存通道的信号完整性。

DRAM中的片上端接(ODT)如何工作?

使用片上端接 (ODT) 涉及两个步骤。首先,必须在 DRAM 中选择片上端接 (ODT) 值。其次,可以使用 ODT 控制器的 ODT 引脚动态启用/禁用它。要配置 ODT,可以使用不同的方法。对于 DRAM,它是通过使用适当的 ODT 值设置模式寄存器来完成的。

根据 DRAM 设备的状态,有时序要求。从本质上讲,片上端接 (ODT) 在数据传输之前打开,然后在数据传输后立即关闭。这种灵活性能够根据需要精确地进行最佳端接。

DRAM 数据信号

让我们尝试了解片上端接 (ODT) 在 DRAM 读写操作中的工作原理。数据信号在写入时由 DRAM 控制器驱动,在读取期间由 DRAM 存储器驱动。PCB上的这些布线不需要外部电阻器,因为DRAM控制器和存储器都配备了ODT。这两种情况下的接收器(写入时的 DRAMS 存储器和读取时的 DRAM 控制器)都将在适当的时间置位片上端接 (ODT)。下图显示了在写入和读取周期期间在这些网络上看到的阻抗。

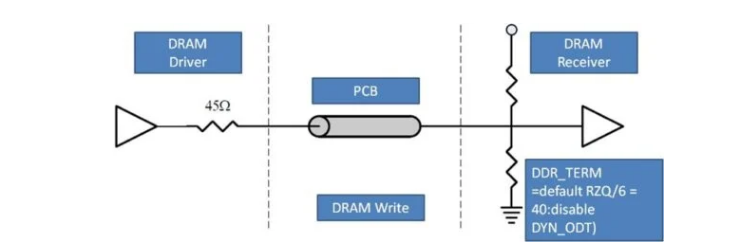

写入周期中的片上端接 (ODT)

让我们举个例子,在写入周期内在网络上看到的阻抗如下图所示。在写入过程中,DRAM器件的输出阻抗约为45Ω。假设RZQ电阻为240Ω,则端接电阻可以配置为提供RZQ/6的片上端接(ODT),有效端接为40Ω。

写入周期内的数据组阻抗

写入周期内的数据组阻抗

读取周期中的片上端接 (ODT)

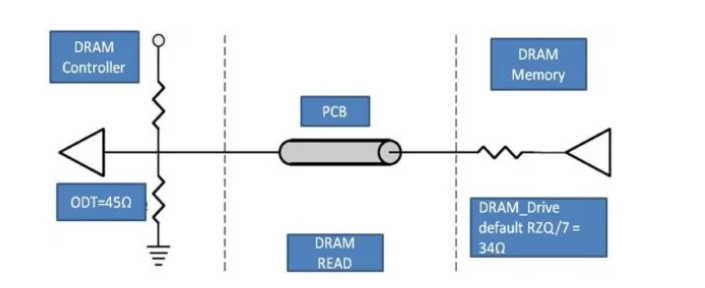

下图显示了在读取周期内在PCB网络上看到的阻抗。在读取过程中,建议将 DRAM 配置为 RZQ/7 或 34 Ω的有效驱动阻抗(假设 RZQ 电阻为 240 Ω)。DRAM控制器内的片上端接(ODT)的有效阻抗为45 Ω。

读取周期内的数据组阻抗

读取周期内的数据组阻抗

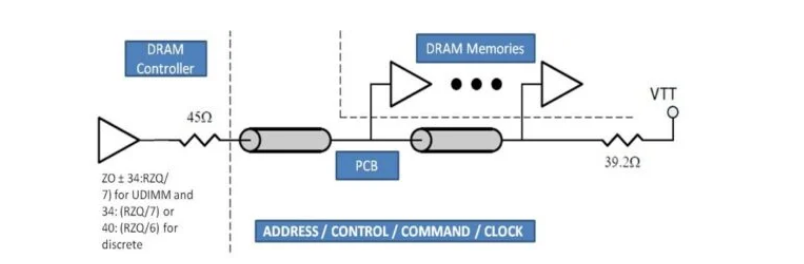

Fly-by信号

现在我们来谈谈fly-by信号,它包括地址、控制、命令和时钟走线。fly-by信号包括来自 DRAM 控制器的fly-by路由、每个 SDRAM 上的短线以及最后一个 SDRAM 之后的端接。在本例中,地址、控制和命令将通过电阻器端接。

DRAM控制器在驱动这些信号时将呈现45Ω的输出阻抗。

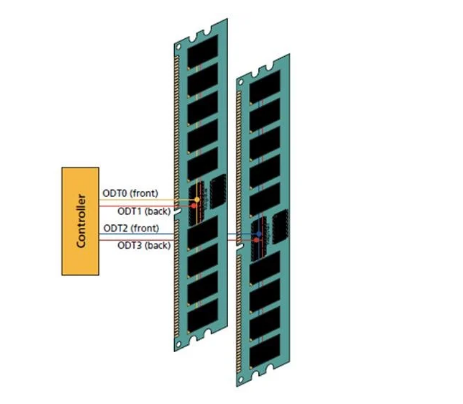

两个 DIIM 插槽片上端接 (ODT) 布线

下图显示了具有两个内存插槽的典型 PC 系统上的片上端接 (ODT) 路由。每个插槽包含两排内存(正面和背面)。单独的 ODT 信号被路由到每个存储器rank,以提供电源管理的灵活性和最佳的系统性能。

典型的 2 插槽 ODT 路由

DIIM 写入周期中的片上端接 (ODT)

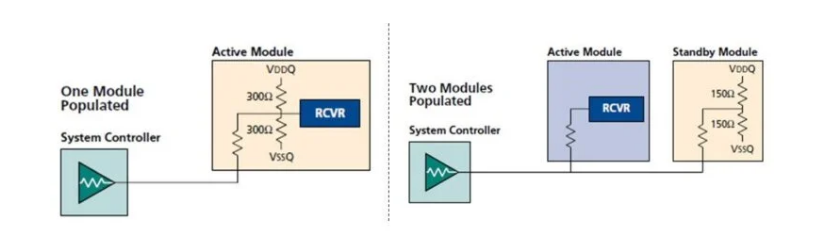

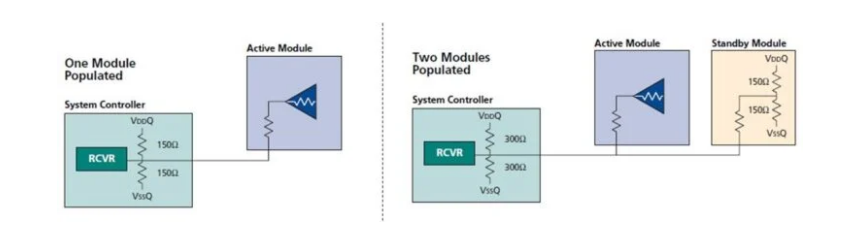

下图显示了一个模块(左)和两个模块(右)系统中写入数据的典型端接方案。

DRAM WRITE的典型ODT配置

DRAM WRITE的典型ODT配置

如果系统中只加载了一个模块,则在写入期间必须在模块上启用 150 欧姆等效端接(300 欧姆上拉和下拉)(上图左)。

如果将两个模块加载到系统中,则未接收写入数据的模块上的端接应在 75 欧姆等效端接电阻(150 欧姆上拉/150 欧姆下拉)。这种端接方案在信号完整性和电压摆幅之间实现了最佳平衡。

DIIM 的 READ 周期中的片上端接 (ODT)

对于读取,控制器上必须包含片上端接。例如,如果系统中只加载了一个模块,则应在系统控制器上启用 75 欧姆端接。如果加载了两个模块,则控制器端接应增加到 150 欧姆,未使用的模块应端接在 75 欧姆。

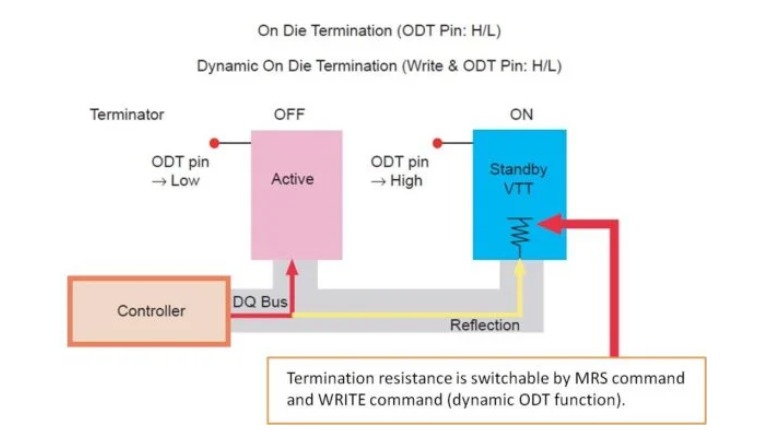

动态片上端接 (ODT) (动态片上端接)

DRAM技术(第3代及以上)可以以比以前高得多的速率传输数据。DRAM 引入了动态片上端接(ODT) 模式。在动态片上端接 (ODT) 中,端接电阻的阻抗可以随着数据模式、频率或温度的变化而动态变化。此功能允许在写入操作期间动态切换片上端接 (ODT) 电阻,而无需模式寄存器集 (MRS) 命令。动态片上端接 (ODT) 有助于优化不同条件下的端接,增强信号完整性和系统性能。

这篇关于什么是On-die Termination(ODT,片上端接)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![【DDR 终端稳压器】Sink and Source DDR Termination Regulator [C] S0 S1 S2 S3 S4 S5 6状态](https://img-blog.csdnimg.cn/direct/227ed36e2d5a4fefbb590fa1532e90b7.png)