本文主要是介绍Spartan6 FPGA DDR3 IP核调试及程序示例,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Spartan6 FPGA芯片中集成了MCB硬核,它可以支持到DDR3。在ISE中提供了MIG IP核,可以用它来生成 DDR3 控制器,并通过 MIG 的 GUI 图形界面完成相关配置。可以参照其官方datasheet查看其用法--UG388

MCB模块信号和架构框图如图3所示,了解内部框图有助于梳理IP核的逻辑架构,更好的完成用户端的逻辑设计。IP核将Memory的控制已经做好并封装起来,提供了FIFO接口给用户端控制,用户只要完成指令FIFO和数据FIFO的读写操作,就能顺利完成对DDR3物理芯片的控制,非常方便。

图3 MCB信号和内部架构框图

二、IP核生成步骤

图4-图17是在ISE14.7环境下生成DDR3 IP核的步骤,按照图中设置一步一步点到最后即可生成:

图4 选择MIG

图5 MIG初始界面

图6 IP核命名

图7 兼容型号选择

图8 存储器类型选择

图9 存储器型号参数设置

图10 终端匹配设置

图11 用户端口设置

图12 用户端口操作顺序设置

图13 时钟类型、终端电阻设置

图14 已设置信息

图15 仿真模型选择

图16 PCB设计参考文档推荐

图17 生成IP核

点击生成后会在相应的路径下产生三个新的文件夹如图18所示,其中docs为MCB的使用指南文档,example_design是IP核做好的测试范例,生成随机数写入到DDR3里面再读回来比较是否正确,可以用来测试DDR3是否工作正常,也有仿真激励,方便用户学习IP核相关信号的时序。user_design就是用户设计使用的逻辑代码,用户可根据IP核提供的用户端口信号时序进行写、读数据,完成对DDR3的操作。

图18 生成的IP核文件夹

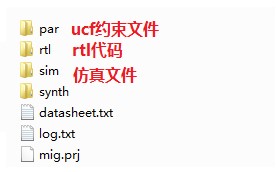

user_design包含的文件夹如图19,包括自动生成的ucf文件,rtl代码及仿真文件等。

图19 user_design内容介绍

三、MCB时序分析

DDR3 IP核提供了端口给用户操作,以FIFO的形式与MCB交互数据,时序简单容易操作。在生成IP核时有一步是选择用户端口模式,提供了5种端口模式供用户选择,不同模式仅与端口个数和位宽有关,操作时序和流程都是一致的,我们所要了解的就是根据时序按照流程完成对端口的操作,如图20所示:

(1)模式1:两路双向32位端口,四路单向32位端口(可配置为读或写,需读和写为一组)。

(2)模式2:四路双向32位端口。

(3)模式3:一路64位双向端口,两路32位双向端口。

(4)模式4:两路64位双向端口。

(5)模式5:一路128位双向端口。

图20 用户端口模式

每一路端口都有一组FIFO,包括指令FIFO,写数据FIFO和读数据FIFO,具体定义如下。

(1)指令FIFO,时序如图21所示。

图21 指令FIFO时序

pX_cmd_clk:指令FIFO同步时钟;

pX_cmd_en:MCB指令使能信号,高电平有效;

pX_cmd_instr[2:0]:MCB控制指令,一般为读或者写指令;

pX_cmd_bl[5:0]: MCB读或写一次的深度,最大为64;

pX_cmd_byte_addr[29:0]:DDR3的地址空间;

pX_cmd_empty:指令FIFO空标志,该FIFO最多可以缓冲3个指令;

pX_cmd_full:指令FIFO满标志,缓冲3个指令即满,

上图为指令FIFO的时序,以pX_cmd_clk为同步时钟,当pX_cmd_en(p0_cmd_en代表p0端口的指令使能信号,本文中设置使用一个端口p0,并且选择128bit的最大位宽)高电平有效一个pX_cmd_clk时钟周期,就能进行一条写或读指令。指令的具体形式是通过pX_cmd_instr来设置,一般常用的是读和写指令。当指令有效后,MCB就可以和DDR3物理芯片进行数据的交互。pX_cmd_bl是当前一次读写的深度,若pX_cmd_bl=63,此时MCB的位宽设置为128bit,那么每发送一条读或写指令,可以从DDR3中读或往DDR3中写128bitX64=1KB大小的数据。pX_cmd_byte_addr为此次数据的读或写的起始地址,完成一次操作后地址会自动增加。比如一次写128bitX64的数据,并且本次操作的起始地址 pX_cmd_byte_addr为0,那么读或写完后,结束地址则为1023,下次的读或写地址应当从 1024开始,可以看出地址空间是以Byte(8bit)的形式来计算的。pX_cmd_empty和pX_cmd_full则是指令FIFO的空和满的状态指示信号,最多可以缓冲3条指令。

(2)写数据FIFO,时序如图22所示。

图22 写数据FIFO时序

pX_wr_clk:写数据FIFO同步时钟;

pX_wr_en:写使能信号,高电平有效期间,每一个时钟的上升沿写入一个数据到FIFO;

pX_wr_mask[3:0]:数据屏蔽;

pX_wr_empy: FIFO空指示;

pX_wr_full:FIFO满指示;

pX_wr_underrun:FIFO溢出指示;

pX_wr_count[6:0]:写入FIFO的数据个数,计数器为异步信号,不准确,只能做参考。

通过MCB操作DDR3芯片,数据并不是直接发送给DDR3,我们先要把数据写入MCB的写数据FIFO中,然后DDR3的控制器再将数据从FIFO中读出,依照DDR3的指令写入到DDR3物理芯片中。

在pX_wr_en高电平期间,每个pX_wr_clk的上升沿写入一个数据到写数据FIFO中。当FIFO没有数据的时候,pX_wr_empy为高电平,当FIFO满的时候则pX_wr_full为高电平,在实际应用中应该避免 pX_wr_full信号有效,当pX_wr_underrun有效时就说明FIFO已经溢出了。pX_wr_count指示当前写入到FIFO的数据个数,由于pX_wr_count也是异步操作,并不能真实反映当前写入的数据个数,但可以作大概评估。比如当我们设置一次写入FIFO数据为64时,并不需要等FIFO写满才发送写指令,可以在pX_wr_count为32的时候就发写指令,能够提高内存的使用效率。

(3)读数据FIFO,时序如图23所示。

图23 读数据FIFO时序

pX_rd_clk:读数据FIFO同步时钟。

pX_rd_en:读使能信号,高电平有效期间,每一个时钟的上升沿从FIFO中读一个数据。

pX_rd_empy:FIFO空指示。

pX_rd_full:FIFO满指示。

pX_rd_underrun:FIFO空时仍然读的溢出指示信号。

pX_rd_count[6:0]:FIFO中可供读取的数据个数,不准确,只能做参考。

同样,如果需要从DDR3芯片中读取数据,也不能直接读取到,必须经过MCB的读数据FIFO。读取FIFO的数据之前,先要进行通过指令FIFO发送一次读 DDR3的指令,由MCB将数据从DDR3物理芯片搬运到读数据 FIFO中,用户再从FIFO中将数据读走。

当 pX_rd_empy 为低电平的时候,表示FIFO非空,则此时可以从FIFO中读取数据,当pX_rd_empy为高电平,表示FIFO为空,此时不能读FIFO。pX_rd_en高电平时,每一个pX_rd_clk的上升沿,可以从FIFO中读取一个数据。pX_rd_full表示FIFO数据满。pX_rd_underrun表示FIFO没有数据时还读出数据的错误指示。pX_rd_count也是异步操作信号,可用来大致评估FIFO中数据个数,当检测到 pX_rd_count大于32的时候,开始从FIFO中读取数据,便于提高利用效率。

四、应用实例

对MCB核有了一定的了解后,下一步就是进行实践操作了。本次工程设计了一个单端口128位模式下,对DDR3全地址空间写数据再读回来对比的测试,按照用户端口的操作流程,先写一个128bit数据到写数据FIFO中,再将写指令写到指令FIFO中,写指令发送完成后将数据和地址递增,直到写满整个地址空间。写完成后开始进行读数据操作,先发送读指令到指令FIFO中,然后等待读数据FIFO非空时将数据读走,将地址递增,直到读完整个地址空间。每读一个数据对比一次,如果不对,则将error信号置为1。

逻辑设计完后,将生成的位流文件烧写到板上验证,并且使用chipscope观测信号波形是否与时序一致,可以看到写操作波形如图24所示:

图24 写数据操作波形

用chipscope观测到的读操作波形如图25所示:

图25 读数据操作波形

以上操作完毕后开始修改代码

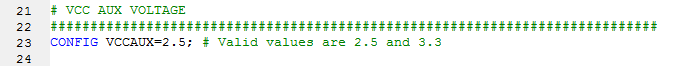

1. 首先打开上面生成的user_design文件夹里的par文件夹,找到里面的UCF文件,因为我的VCC AUX电压是2.5V所以不用修改,要是用的3.3就要修改为3.3V

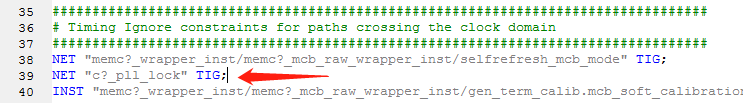

2. 把39行的NET "c?_pll_lock" TIG注释掉,这句不用

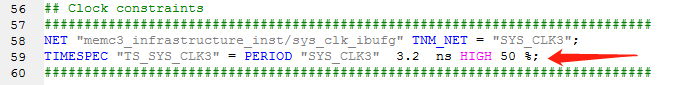

3. 修改系统时钟输入的周期为 20ns, 这需要跟你板子上的输入时钟频率一致,如果DDR的输入时钟是FPGA上PLL产生的就把下面这两句屏蔽了就行

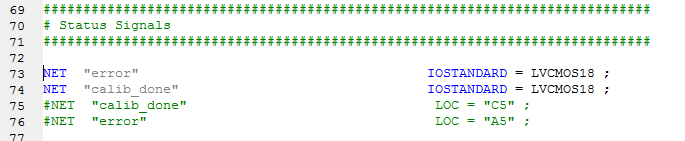

4. 如下两个信号的电平标准及引脚约束根据情况设置,如果DDR的输入时钟是FPGA上PLL产生的就把下面这四句屏蔽了就行5.

![]()

![]()

5. 下面的这些状态信号的电平标准需要修改,我没有用他们,直接屏蔽也行

打开上面生成的user_design文件夹里的rtl文件夹,打开主程序ddr3_demo.v(这个是你新建IP时命名的DDR3的名字),做如下修改

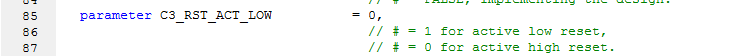

1. 首先设置复位信号是高电平复位还是低电平复位,根据板子情况修改

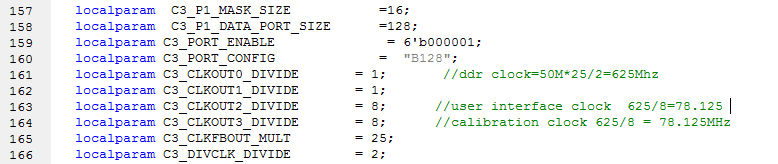

2. 由于板上的时钟输入为 50Mhz, 因为 DDR3 是上下沿采样,这样 FPGA 内部的 DDR3控制器的时钟需要625MHz ,所以这里需要倍频25,再分频2,得到625Mhz的CLKOUT0和 CLKOUT1,再分频 8 分别得到 user interface 的时钟CLKOUT2和 calibration 的时钟 CLKOUT3都设置为78.125Mhz。当然CLKOUT2可以设置为其他的时钟频率,但是calibration 的时钟 CLKOUT3一般设置为50M-100M之间,

设置完毕,下面是具体的读写例程,有时间再补上

………………………………………………

参考链接:https://blog.csdn.net/zhyl558/article/details/82018271

这篇关于Spartan6 FPGA DDR3 IP核调试及程序示例的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!