spartan6专题

Spartan6 FPGA DDR3 IP核调试及程序示例

Spartan6 FPGA芯片中集成了MCB硬核,它可以支持到DDR3。在ISE中提供了MIG IP核,可以用它来生成 DDR3 控制器,并通过 MIG 的 GUI 图形界面完成相关配置。可以参照其官方datasheet查看其用法--UG388MCB模块信号和架构框图如图3所示,了解内部框图有助于梳理IP核的逻辑架构,更好的完成用户端的逻辑设计。IP核将Memory的控制已经做好并封装起来,提供了

spartan6 MCB调试中碰到的问题

1、对于MCB自己产生的rst0输出信号,不是很可靠。 用这个rst0信号做全局reset,发现很多reset下必须为一个默认值的(全0的不算,不设置默认就是0)寄存器,统统不正常。开始还以为自己代码有问题,仔细仿真后发现功能没问题,reset下都能正常赋默认值,上板调试后发现和仿真结果不对。找了很久没找到原因,后来才顿悟到这个reset信号上。自己写了一个reset,马上正常。 正确的做法应

Spartan6 LX45 DDR3调试与分析

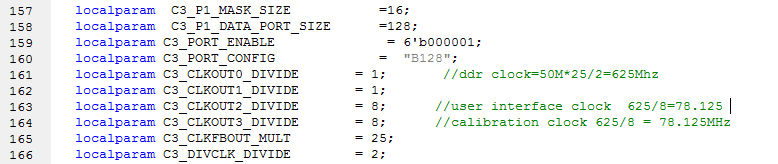

新的一年,新的开始。本文对最近的学习做个总结吧。最近在做spartan6的ddr3开发,FPGA采用的是spartan6的XC6LX45T,平台工具为ISE14.6,MIG的版本为3.92。采用的DDR3芯片为MT41J128M16XX-187E,并使用chipscope完成仿真调试(主要是实例的仿真学习)。 根据黑金Spartan6开发板的教程可以很快生成DDR3的MIG实例。首先了解下IP生