本文主要是介绍【FPGA】DDR3学习笔记(一)丨SDRAM原理详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本篇文章包含的内容

- 一、DDR3简介

- 1.1 DDR3 SDRAM概述

- 1.2 SDRAM的基础结构

- 二、 SDRAM操作时序

- 2.1 SDRAM操作指令

- 2.2 模式寄存器(LOAD MODE REGISTER)

- 2.3 SDRAM操作时序示例

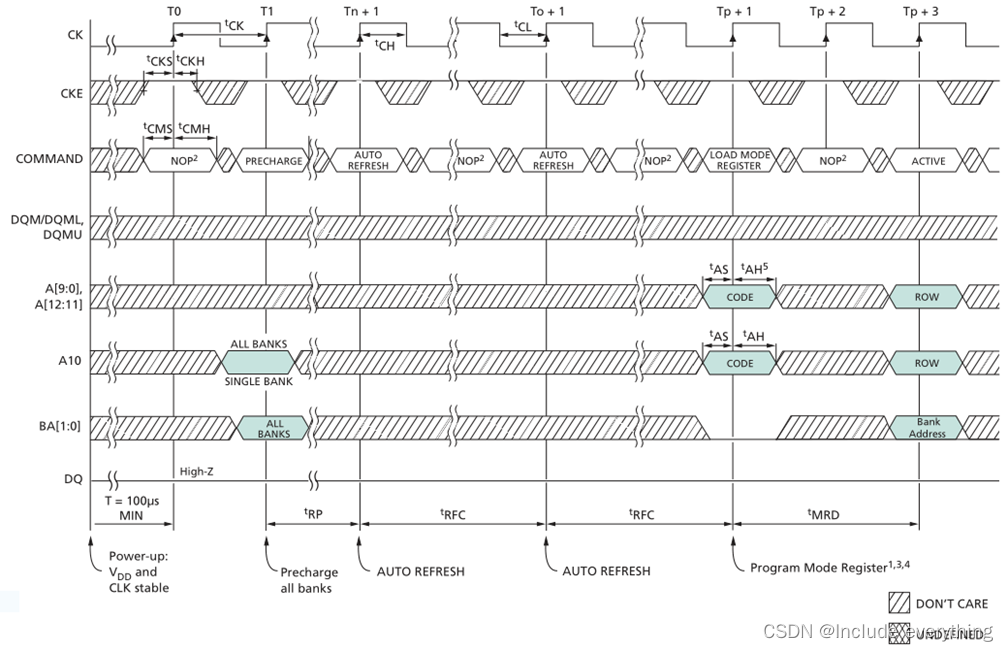

- 2.3.1 SDRAM初始化时序

- 2.3.2 突发读时序

- 2.3.3 随机读时序

- 2.3.4 突发写时序

- 2.3.5 随机写时序

- 2.3.6 写-写时序

- 2.3.7 写-读时序

- 2.3.8 写后预充电时序

- 2.3.9 打断突发写时序

- 2.3.10 掩码操作

- 2.3.11 刷新时序 Auto Refresh

- 2.3.12 (休眠)刷新 Self Refresh

笔者在这里使用的开发板是正点原子的达芬奇开发板,FPGA型号为XC7A35TFGG484-2。参考的课程是正点原子的课程手把手教你学达芬奇&达芬奇Pro之FPGA开发篇。本次实验的学习目的是通过熟悉DDR3的读取,为摄像头OV5640模块的使用做准备。

一、DDR3简介

1.1 DDR3 SDRAM概述

DDR3 SDRAM(Double Data Rate 3 Synchronous Dynamic RAM),即第三代双倍速率同步动态随机存储器。

- 双倍速率:DDR3在时钟的上升沿和下降沿都可以读取数据;

- 同步:DDR3读取数据是按时钟同步的,它的时钟频率与CPU前端总线的系统时钟频率相同,并且内部的命令发送与数据的传输都以它为基准;

- 动态:DDR3中的数据无法掉电保存,同时如果想要保存数据,需要对数据进行周期性的刷新;

- 随机存取:可以随机操作任意地址的数据,数据不是线性依次存储的,可以自由指定要读写的地址。

在设计DDR设备时,需要关注SDRAM的芯片位宽和物理Bank(Physical Bank,P-Bank) 之间的关系。

- 芯片位宽:每一片SDRAM缓存芯片本身的位宽。

- 物理Bank:传统内存系统为了保证CPU的正常工作,必须一次性传输完CPU在一个传输周期内需要的数据,控制内存与CPU之间数据交换的北桥芯片规定内存总线的数据位宽需要等同于CPU数据总线的位宽(CPU在一个传输周期内能够接受的数据容量),这个位宽就称为物理Back(Physical Bank)的位宽。

当芯片位宽小于物理Bank时,就可以将多片SDRAM级联工作,以达到CPU存储数据的需求。

1.2 SDRAM的基础结构

SDRAM中最核心的结构为逻辑Bank(Logical Bank,L-Bank),它是SDRAM内部空间划分的片区。每一个L-Bank都可以想象成一个巨大的“方格”矩阵,每一个方格中都可以存储和芯片位宽等长的数据,每一个方格都有对应的行编码和对应的列编码。

理论上说,SDRAM中完全可以只制造一个巨大的Bank来存放所有的数据,但是经过行业迭代的发展,没有这样做的原因大致可以分为如下几点:

- 只有一个Bank相较于多个Bank在工艺上很难实现,即使实现,成本也很高;

- 只有一个Bank最大的问题在于读写速度较慢,甚至可能出现读写错误。由于SDRAM的操作逻辑是激活Bank中的对应行和对应列将数据读出,巨大的Bank会使得一次激活的时间变长,甚至在行切换时导致数据读写错误,采用多个Bank级联存储的方式可以大大缩短读取时间。

SDRAM中存储数据是通过电容实现的。下面是一个bit的简单存储原理示意图。通过读取电容上的电量来判断该位为0还是1,并且需要不断刷新重复写入才能保证数据不丢失。

SDRAM的内部结构可以大致如下图所示,这只是一个相对简单的SDRAM内部结构示意图。

二、 SDRAM操作时序

2.1 SDRAM操作指令

理解SDRAM的工作时序之前有必要学习SDRAM的指令时序。为了提高数据读写效率,SDRAM没有独立的指令读取周期,而是通过不同控制线的组合实现不同的指令读取,不同指令对应控制线的真值表如上图所示。

特别需要注意的是:行激活ACTIVE指令后需要等待一段时间才能进行列激活,这一段时间称为 t R C D t_{RCD} tRCD,RCD(RAS to CAS Delay)称为行到列选择延迟时间。具体的延迟时间应参考器件手册。下面是一种情况下的时序示例:

- 数据刷新(Refresh)模式选择:

CKE,时钟使能。从字面意义理解,它仅仅是时钟输入的使能控制线,但是它最主要的功能是选择SDRAM内部数据刷新时钟的来源。当CKE为高电平时,SDRAM正常工作,所有指令都有效,并且刷新计数器的时钟来自CPU,即执行Auto Refresh模式;当CKE为低电平时,SDRAM处于休眠模式,屏蔽所有指令和数据读写,刷新计数器的时钟来源为芯片内部时钟,即执行Self Refresh模式。存储体中的存储电容最长有效数据周期为64ms,所以刷新一行数据的最长时间是64ms/行数。当一个L-Bank中有4096行时,最长刷新时间为15.625μs。Auto Refresh模式下还可以通过配置A10选择对所有Bank进行自刷新还是对所有的Bank进行自刷新。 - 预充电(Precharge):从原理上说,刷新和预充电对存储电容的操作是相同的,但是二者存在本质的区别:刷新是周期进行的,预充电是随着读写操作非周期进行的。由于读写和行选中操作会对存储电容中的电荷产生干扰,所以进行每一次读写操作后都需要重新对电容进行充(放)电,使0和1都回归到正常的电平。预充电操作需要在当前工作行操作结束,激活新行操作之间进行。充电可以手动执行,也可以配置芯片自动执行。Auto Perchage(AP) 在这里并不是指在结束读写操作后是否自动充电,而是定义了自动充电的范围,开启AP意味着每一次读写操作后都会对所有的Bank进行充电。虽然这样做会损耗一些芯片资源(对于没有操作过的行进行预充电意义不大),但是为了维护数据的稳定性作出这一点牺牲也未尝不可。AP是否开启通过地址线

A10控制,当A10为高电平时开启AP。 - 读写延迟(Delay):由于SDRAM内部芯片的关系,执行读写操作所用的时间并不完全相同。对于写操作,可以认为CPU将数据放在数据线上时SDRAM就完成了数据的写入;而对于读操作,执行完后需要等待两个时钟周期的时间数据才会正确出现在数据线上。

- 突发(Burst)模式:只在同一行中对连续的数据单元进行读写操作的模式,连续传输所需要的数据长度定义为突发长度(Burst Length,BL)。这个突发操作可以被Burst Terminate指令打断。

下面是一些操作指令的时序图,可以帮助理解。

2.2 模式寄存器(LOAD MODE REGISTER)

通过配置SDRAM的模式寄存器(Mode Register),我们可以修改如下参数:

-

突发长度(Burst Length,BL):突发操作时一次读取数据的单元数,通过

M0~M2配置。 -

突发模式(Burst Type):突发模式有两种,一种是连续模式(Sequential),一种是交替模式(Interleaved)。通过

M3进行配置,一般情况下都使用连续模式。

-

行地址选择脉冲延迟(CAS Latency,CL):CAS(Column Address Strobe)即行选择信号(同时进行读写命令发送),如果发送的是读信号,那么从发送信号到开始接受数据需要等待CL个时钟周期。一般这个值取2,根据数据手册可以查到不同的时钟频率对应的延迟时间应该是多少,通过

M4~M6配置。 -

写突发模式选择(Write Burst Mode):在突发写入数据时,如果希望逐个数据依次写入,可以将

M9配置为1,否则突发写入数据的BL将与突发读出数据的BL相同。 -

Op Mode和其他位:存储器厂商为了和其他产品兼容留下的配置位,对读写时序没有太大影响,可以忽略。

2.3 SDRAM操作时序示例

2.3.1 SDRAM初始化时序

2.3.2 突发读时序

2.3.3 随机读时序

2.3.4 突发写时序

2.3.5 随机写时序

2.3.6 写-写时序

笔者的理解是突发写还未结束就可以发送一个新的写指令。

2.3.7 写-读时序

2.3.8 写后预充电时序

2.3.9 打断突发写时序

2.3.10 掩码操作

下面是BL为4时的掩码操作时序示例。SDRAM写入数据是通过写入寄存器写入的,由DQM数据线控制写入数据是否被屏蔽。如下图所示,DQM为低电平时表示允许数据写入,DQM为高时为禁止数据写入。读指令时的时序类似,同样是在数据线上数据有效时操作DQM来控制数据是否正常输出,注意读数据时存在延时,这里不再列出时序图。

2.3.11 刷新时序 Auto Refresh

2.3.12 (休眠)刷新 Self Refresh

原创笔记,码字不易,欢迎点赞,收藏~ 如有谬误敬请在评论区不吝告知,感激不尽!博主将持续更新有关嵌入式开发、FPGA方面的学习笔记。

这篇关于【FPGA】DDR3学习笔记(一)丨SDRAM原理详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!