sdram专题

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR*(一篇文章就懂)

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR* 内存 内存(Memory)指的是内存存储器,又称为主存,是CPU用来直接寻址和存储的空间,它相当于一座桥梁,用以负责诸如硬盘、主板、显卡等硬件上的数据与处理器之间数据交换处理,我们可以把内存看作数据缓存区,一个高速的缓存区。内存之所以称为内存,是相对于硬盘这些外存而言,我们要用的软件数据都安装存放在外存上,但是当我

STM32HAL库--SDRAM实验(速记版)

STM32F429IGT6 自带了 256K 字节的 SRAM,对一般应用来说,已经足够了,不过在一些对内存要求高的场合, STM32F429 自带的这些内存就不够用了。比如使用 LTDC 驱动RGB 屏、跑算法或者跑 GUI 等,就可能不太够用,所以阿波罗 STM32F429 开发板板载了一颗 32M 字节容量的 SDRAM 芯片:W9825G6KH,满足大内存使用的需求。 1

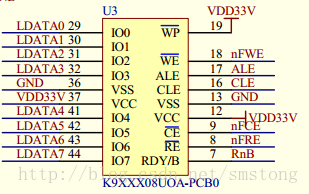

s3c2440和sdram

经过了一段时间考试,今天终于把SDRAM这块给学习了。 1、许多单片机像STM32一直是使用片上FLASH和RAM,MDK也是定义好了下载算法,进行简单地配置就可以了,而s3c2440确需要外扩FLASH和SDRAM(小于4K的程序可以不用配置SDRAM),使用前需要对其进行初始化。 S3C2440 有 27 根地址线 ADDR[26:0],2^27= 128Mbyte ,是一个bank的最大

[DDR5 Jedec 3]DDR5 SDRAM 状态图 和 基本功能

3000字, 依公知及经验整理,原创保护,禁止转载。 专栏 《深入理解DDR》 3.1 简化状态图 来源: Jedec Proposed DDR5 Full spec 缩写功能ACT激活PRE预充电PRE_A全部预充电MRS寄存器集模式REF刷新TEN边界扫描模式ReadRD, RDS4, RDS8Read ARDA, RDS4A, RDS8AwriteWR, WRS4, WRS8

MDK + Jlink + SDRAM 裸奔2440教程

MDK下裸奔2440教程 1、背景 很多人学习嵌入式编程都是从裸机开始的(我个人也是)。这并不是偶然,想要零基础入门嵌入式开发,玩转裸机绝对是最好的入手点。这样至少可以培养以下必备技能: l CPU体系结构,编程模式及汇编语言、指令结构的知识 l 芯片内部外设,如串口、定时器、LCD、Nandflash等的相关编程知识 l 编程环境(这里主要介绍MDK),调试

【专篇】DDR5 SDRAM-01总体介绍

概念 DDR5 SDRAM(第五代双倍数据率同步动态随机存取存储器)是一种正在开发的高带宽电脑存储器规格,属于SDRAM家族的存储器产品。DDR5重点提升了DRAM存储的密度和速率,支持单颗64Gbit的DRAM存储芯片,是DDR4最大允许容量(16Gbit)的四倍。DDR5相比DDR4具有更高的数据传输率(速度)、更多的带宽、更低的工作电压和更好的效率。 DDR5支持每列8Gb到64Gb的内

详解SDRAM基本原理以及FPGA实现读写控制

文章目录 一、SDRAM简介二、SDRAM存取结构以及原理2.1 BANK以及存储单元结构2.2 功能框图2.3 SDRAM速度等级以及容量计算 三、SDRAM操作命令3.1 禁止命令: 4'b1xxx3.2 空操作命令:4'b01113.3 激活命令:4'b00113.4 读命令:4'b01013.5 写命令 :4'b01003.6 突发中止命令 :4'b01103.7 预充电命令 :4'

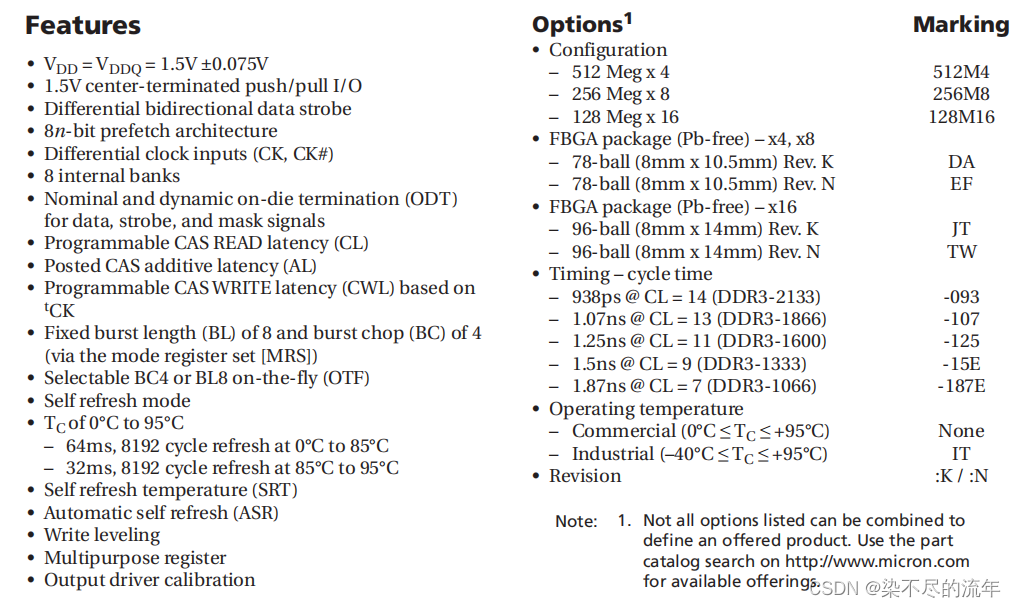

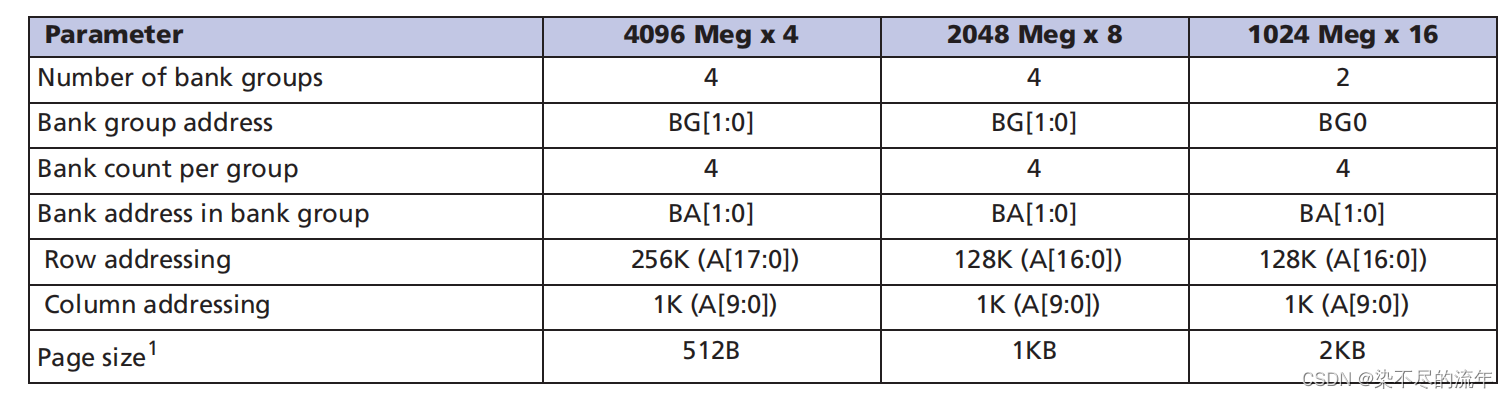

【专篇】DDR3 SDRAM-01总体介绍

概念 DDR3 SDRAM(Double-Data-Rate 3 Synchronous Dynamic Random-Access Memory,第三代双倍速率同步动态随机存取存储器)是计算机存储技术的一种重要进步,它在前代DDR2 SDRAM的基础上进行了多项改进和优化。以下是DDR3 SDRAM的特点介绍: 双倍速率(DDR):DDR3 SDRAM采用双倍速率数据传输技术,即在每个

【专篇】DDR4 SDRAM-01总体介绍

概念 DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory)是一种先进的高性能存储器规格,是DDR3 SDRAM的后续产品。自2011年首次由三星电子制造并公布以来,它已经成为现代计算机系统中广泛采用的内存标准。 主要特点: 更高带宽: DDR4提供比DDR3更高的数

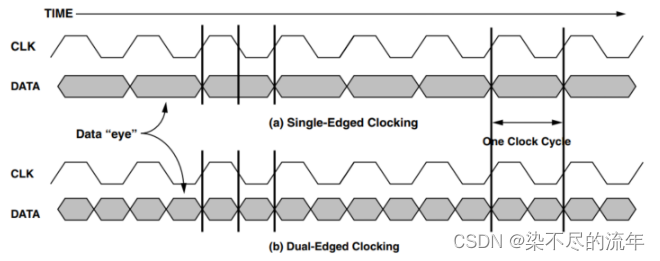

SDR SDRAM和DDR SDRAM的区别

SDR SDRAM(Single Data Rate Synchronous Dynamic Random Access Memory)和DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)是两种不同类型的内存技术,它们的主要区别在于数据传输速率和工作原理,具体如下: 数据传输速率: SDR SDRAM:只能在

【DRAM存储器二十八】DDR4介绍-DDR4 SDRAM的主要技术特性之ODT,为什么要新增RTT_PARK?

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考资料:《镁光DDR4数据手册》 、《JESD79-4B》 ODT DDR4的ODT相对DDR3又有更新。我们从DDR2到DDR4一起回顾一下。DDR2的终端电阻为RTT(NOM),由EMR的EMR的bit2和bit6进行设置:

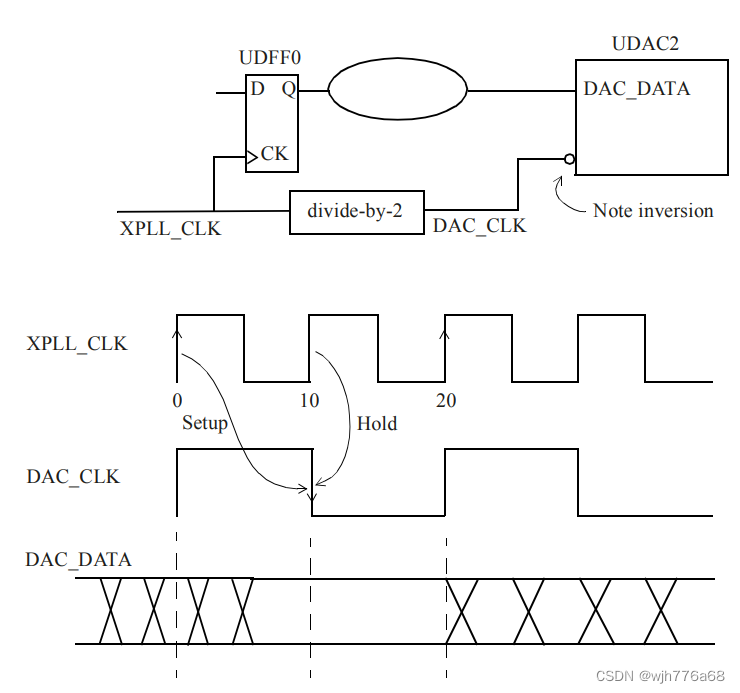

【STA】SRAM / DDR SDRAM 接口时序约束学习记录

1. SRAM接口 相比于DDR SDRAM,SRAM接口数据与控制信号共享同一时钟。在用户逻辑(这里记作DUA(Design Under Analysis))将数据写到SRAM中去的写周期中,数据和地址从DUA传送到SRAM中,并都在有效时钟沿处被锁存在SRAM中。在DUA从SRAM中取数据的读周期中,地址信号从DUA传送到SRAM中去,数据信号由SRAM输出给DUA。 DUA与SRA

STM32 SDRAM知识点

1.SDRAM和SRAM的区别 SRAM不需要刷新电路即能保存它内部存储的数据。而SDRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,功耗较SDRAM大 [1],相同容量的SDRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。同样面积的硅片可

DRAM,SRAM,SDRAM,DDR SDRAM区别!

http://blog.sina.com.cn/s/blog_5146fb2d0100hsar.html 问题1:什么是DRAM、SRAM、SDRAM? 答:名词解释如下 DRAM--------动态随即存取器,需要不断的刷新,才能保存数据,而且是行列地址复用的,许多都有页模式 SRAM--------静态的随机存储器,加电情况下,不需要刷新,数据不会丢失,而且一般不是行列地址复用的 SDRAM

【FPGA】DDR3学习笔记(一)丨SDRAM原理详解

本篇文章包含的内容 一、DDR3简介1.1 DDR3 SDRAM概述1.2 SDRAM的基础结构 二、 SDRAM操作时序2.1 SDRAM操作指令2.2 模式寄存器(LOAD MODE REGISTER)2.3 SDRAM操作时序示例2.3.1 SDRAM初始化时序2.3.2 突发读时序2.3.3 随机读时序2.3.4 突发写时序2.3.5 随机写时序2.3.6 写-写时序2.3.7 写-

SDRAM停产怎么办?Bordison承诺-长寿命不停产,量产再无忧!(

不少工程师发现,公司产品量产时突然采购告知所用SDRAM缺货或停产了,让工程师重新找一个替代的型号,轻则找一个PIN TO PIN兼容的就完事了,重则需要重新改PCB或修改程序。从而增加了产品研发周期和费用。因为在内存行业里,因为成本的压力,快则7~8个月,慢则1年时间就会改版,缩小芯片die以降低成本。正因为这种快速的更新换代,给工程师与采购带来了不少的麻烦。本文结合电子称行业的应用需

SRAM、SDRAM、FLASH三者的区别

Sram的好处是接口简单,速度快容易操作,用资源也比较少;sdram的最大好处是容量大,当然速度也比较快,但是接口复杂些,也耗逻辑资源多些;flash是非易失性存储器,速度慢。 目前,相同容量的SRAM价格是SDRAM的8倍左右,面积则将近大4倍,所以SRAM常用于快速存储的较低容量的RAM需求,比如Cache(缓存),比如CPU内部的L1 Cache和主板上的L2 Cache,一般只有几百K。

存储器(ROM、SDRAM、RAM、DRAM、SRAM、FLASH)的区别

个人学习,侵删 ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写。ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是在掉电之后就丢失数据,典型的RAM就是计算机的内存。 RAM有两大类,一种称为静态RAM(Static RAM/SRAM),另一种称为动态RAM(Dynamic RAM/DR

老SDRAM和DDR SDRAM时序图与信号完整性仿真结合运用(2) -版本博客图片丢失,增加图片后又不能上传,shit.

前一段时间只是以2410和6410时序图简单归纳了一下,现在将时序基础概念和详细计算过程彻底理一遍。 传播延迟 信号从缓冲器出来之后,就要经过传输线到接收终端,信号在传输线上的传输的延时我们称为传播延迟(propagation delay),属于器件外部的延迟,它只和信号的传播速度和线长有关。 最大/最小飞行时间 飞行时间(Flight T

STM32CbueMX之SDRAM

SRAM(静态随机存取存储器) 静态随机存取存储器(Static Random-Access Memory,SRAM)是随机存取存储器的一种。所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。相对之下,动态随机存取存储器(DRAM)里面所储存的数据就需要周期性地更新。然而,当电力供应停止时,SRAM储存的数据还是会消失(被称为volatile memory),这与在断电后

【STM32F429-DISCOVERY学习笔记】STM32F429驱动SDRAM(IS42S16400J)详解

http://bbs.armfly.com/read.php?tid=1942 驱动SDRAM的时序比较的麻烦一些,不像驱动SRAM,非常简单,网上搜索一下,估计有非常多的FPGA驱 动SDRAM的资料,而且是各种的给你讲时序问题,现在F429/439集成了控制 器以后就方便很多了,用户只需配 置 相应的寄存器即可,这里向大家推荐一篇文章,强烈的推荐, 不懂SDRAM为何

DDR2(SDRAM)初始化 28个步骤总结

S5PV210 DDR2初始化 28个步骤总结 首先在初始化DDR之前,引入一个关于DRAM Drive Strength的概念----DRAM Drive Strength(也被称为:driving strength),表示“DRAM驱动强度”。这个参数用来控制内存数据总线的信号强度,数值越高代表信号强度越高,增加信号强度可以提高超频的稳定性。但是并非信号强度高就一定好。所以,这里我们

深入了解DRAM和SDRAM:内存带宽的计算与封装形式的奥秘

SSD SDRAM DDR SDRAM简介 动态随机存取存储器DRAM(Dynamic Random Access Memory,DRAM)是一种半导体存储器。 其主要的作用原理是利用电荷内存储电荷的数量来代表一个二进制比特(bit)是1还是0。 由于在现实中品体管会有漏电电流的现象,导致电客上所存储的电荷数量并不足以正确的判别数据,而导致数据毁损。因此对于DRAM来说,周期性地充电是一个

TQ2440开发板学习纪实(8)--- 从NAND Flash读取数据,把代码搬运到SDRAM运行

因为依赖于S3C2440的开机自动从Nandflash复制数据到片内SRAM执行,目前我们的可执行程序体积仍然不能大于4KB的限制。而我们的程序目前已经非常接近这个限制大小了,为了能够继续开发,必须突破这个限制。为此需要实现代码搬运功能,把程序从Nandflash搬运到SDRAM中去,并跳转到SDRAM执行。 本文为啥不实现NandFlash写? 因为对于我们的实现目前尚未需求。更重要的是,写操

SDRAM驱动文档 (IS42S32800J-6BLI)

(一)SDRAM 信号线 CLK -> 时钟信号,在该时钟的上升沿采集输入信号 CKE -> 时钟使能,禁止时钟时,SDRAM 会进入自刷新模式 CS# ->片选信号,低电平有效 RAS# -> 行地址选通信号,低电平时,表示行地址 CAS# -> 列地址选通信号,低电平时,表示列地址 WE# -> 写使能信号,低电平有效 A0~A12 -> 地址线(行/列) BS0,BS1 -> BANK 地

DRAM、SDRAM和SRAM的区别

特点简介: SRAM : 静态 RAM , 不用刷新, 速度可以非常快, 像 CPU 内部的 cache , 都是静态 RAM , 缺点是一个内存单元需要的晶体管数量多,因而价格昂贵,容量不大。 DRAM : 动态 RAM ,需要刷新,容量大。 SDRAM :同步动态 RAM ,需要刷新,速度较快,容量大。 DDR SDRAM : 双通道同

![[DDR5 Jedec 3]DDR5 SDRAM 状态图 和 基本功能](https://img-blog.csdnimg.cn/direct/1539e07b5b744855a7397a81e7b8ae6f.png)