本文主要是介绍SDRAM驱动文档 (IS42S32800J-6BLI),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

(一)SDRAM 信号线

CLK -> 时钟信号,在该时钟的上升沿采集输入信号

CKE -> 时钟使能,禁止时钟时,SDRAM 会进入自刷新模式

CS# ->片选信号,低电平有效

RAS# -> 行地址选通信号,低电平时,表示行地址

CAS# -> 列地址选通信号,低电平时,表示列地址

WE# -> 写使能信号,低电平有效

A0~A12 -> 地址线(行/列)

BS0,BS1 -> BANK 地址线

DQ0~31 -> 数据线

FMC_NBL0-3 -> 数据掩码,表示 DQ 的有效部分

(二)存储单元

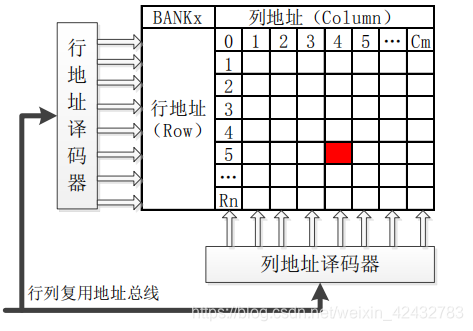

SDRAM 的存储单元(称之为:BANK)是以阵列的形式排列的,如图 1 所示。每个存储单元的结构示意图,如图所示:

对于这个存储阵列,可以将其看成是一个表格,只需要给定行地址和列地址,就可以确定其唯一位置,这就是 SDRAM 寻址的基本原理。而一个 SDRAM 芯片内部,一般有 4 个这样的存储单元(BANK),所以,在 SDRAM 内部寻址的时候,先指定 BANK 号和行地址,然后再指定列地址,就可以查找到目标地址。

SDRAM 的存储结构示意图,如图2所示,寻址的时候,首先 RAS 信号为低电平,选通行地址,地址线 A0~A12 所表示的地址,会被传输并锁存到行地址译码器里面,作为行地址,同时BANK地址线上面的BS0,BS1所表示的BANK地址,也会被锁存,选中对应的BANK,然后,CAS 信号为低电平,选通列地址,地址线 A0~A12 所表示的地址,会被传输并锁存到列地址译码器里面,作为列地址,这样,就完成了一次寻址。

IS42S32800J-6BLI的存储结构为:行地址:4096个;列地址:512 个;BANK 数:4 个;位宽:32 位;这样,整个芯片的容量为:40965124*32=32M 字节。

(三)数据传输

在完成寻址以后,数据线 DQ0~DQ31 上面的数据会通过数据控制逻辑写入(或读出)存储阵列。

特别注意:因为 SDRAM 的位宽,可以达到 32 位,也就是最多有 32 条数据线,在实际使用的时候,我们可能会以:8 位、16 位、24 位和 32 位等宽度来读写数据,这样的话,并不是每条数据线,都会被使用到,未被用到的数据线上面的数据,必须被忽略,这个时候就需要用到数据掩码(DQM)线来控制了,每一个数据掩码线,对应 8 个位的数据,低电平表示对应数据位有效,高电平表示对应数据位无效。

以 IS42S32800J-6BLI为例,假设以 16 位数据访问,我们只需要 DQ0~DQ15 的数据,而 DQ16~DQ31的数据需要忽略,此时,我们只需要设置 FMC_NBL0-1 为低电平,FMC_NBL2-3 为高电平,就可以了。

(四)控制命令

(五)初始化

初始化过程分为五步:

① 上电

此步,给 SDRAM 供电,使能 CLK 时钟,并发送 NOP(No Operation 命令),注意,上电后,要等待最少 200us,再发送其他指令。

② 发送预充电命令

第二步,就是发送预充电命令,给所有 Bank 预充电。

③ 发送自动刷新命令

这一步,至少要发送发送 8 次自刷新命令,每一个自刷新命令之间的间隔时间为 tRC。

④ 设置模式寄存器

这一步,发送模式寄存器的值,配置 SDRAM 的工作参数。配置完成后,需要等待 tMRD (也叫 tRSC),使模式寄存器的配置生效,才能发送其他命令。

⑤ 完成

经过前面四步的操作,SDRAM 的初始化就完成了,接下来,就可以发送激活命令和读/写 命令,进行数据的读/写了。

这里提到的 tRC、tMRD 和 tRSC 见 SDRAM 的芯片数据手册。

(六)写操作

SDRAM 的写流程如下:

① 发送激活命令

此命令同时设置行地址和 BANK 地址,发送该命令后,需要等待 tRCD 时间,才可以发送写命令。

这篇关于SDRAM驱动文档 (IS42S32800J-6BLI)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!