本文主要是介绍DDR3接口,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

mig IP核的配置

首先添加mig IP核

然后确认以下工程信息,主要是芯片型号以及编译环境,没什么问题后点击next.

如下图所示,这一页选择"Create Design",在"Component Name"一栏设置该IP元件的名称,这里取默认软件的名称,再往下选择控制器的数量,控制器的数量是指由多少片独立的DDR3,如果DDR3采用并联的方式则只需要一个控制器。我们采用的是两片DDR3并联的方式,因此只需要选择一个控制器就可以。最后是AXI4的接口,这里也勾选上。然后点击next。

如下图所示,这一页主要是让用户选择可以兼容的芯片,本工程默认不勾选,即不需要兼容其他的芯片。然后继续点击next。

如下图所示,这一页选择的是mig控制器控制的芯片,勾选DDR3即可,点击next。接下来正式配置mig IP核的参数。

如下图所示,接下来介绍这些可配置参数的意义。

(1)Clock Period:DDR3芯片的运行时钟周期,这个参数的范围和FPGA芯片的类型以及具体类型的速度等级有关。本试验选择2500ps,对应400M,这是本次试验所采用芯片可选的最大频率。注意这个时钟是MIG IP核产生,并输出给DDR3物理芯片使用的,它关系到DDR3的运行带宽。比如本次试验的开发板板载两颗DDR3芯片,数据位宽32位,且双边沿触发,带宽达到了 400 M ∗ 2 ∗ 32 b i t = 25.6 G b / s 400M*2*32bit=25.6Gb/s 400M∗2∗32bit=25.6Gb/s。

(2)PHY to Controller Clock Ratio:DDR3芯片的运行时钟和MIG IP核的用户端(FPGA)的时钟之比,一般有4:1和2:1两个选项。本次试验选择4:1。由于DDR芯片的运行时钟是400MHz,因此在MIG IP核的用户时钟(ui_clk)就是100MHz。一般来说高速传输场合默认4:1,要求低速场合选择2:1。这里还要指出,当DDR3时钟选择了350MHz到400MHz,比例只能默认的4:1,低于350MHz才有4:1和2:1两个选项。

(3)VCCAUX_IO:这是FPGA高性能bank的供电电压,Vccaux_io必须设置为2.0以实现最高数据速率。

在FPGA高范围bank中无法使用Vccaux_io。因为本试验使用的是高范围bank,所以未使用Vccaux_io。

(4)Memory Type:DDR3存储器类型选择。本试验选择Component。

(5)Memory Part:DDR芯片的具体型号。本实验选择MT41J128M16XX-125,这个型号其实和实际的硬件原理图上的型号NT5CB128M16FP-DI是不同的,但是也可以使用,只要用户的DDR芯片容量和位宽一致,大部分是可以兼容的。如果没有兼容的的器件,也可以点击"Create Custom Part(创建自定义器件)"按钮创建一个自定义器件。

(6)Memory Voltage:是DDR3芯片的电压选择,本试验选1.5V。

(7)Data Width:数据位宽选择,这里选择32,是因为两块DDR3拼接而成。数据宽度值可以根据之前选择的存储器类型选择。列表中显示了所选部件的所有支持的数据宽度。可以选择其中一个数据宽度。这些值通常是各个器件数据宽度的倍数。在某些情况下,宽度可能不是一个精确的倍数。例如16位是x16元件的默认数据宽度,但是8也是一个有效的值。

(8)ECC:ECC校验使能,数据位宽为72位的时候才能使用。本试验不使用它。

(9)Data Mask:数据屏蔽管脚使能。勾选它才会产生屏蔽信号,本试验没有用到数据屏蔽,但是还是把它勾选上。

(10)Number of Bank Machines:Bank Machine的数量原本用来对具体的某个或者几个来单独控制的,选择多了效率就会高,相应的占用的资源也多,本试验选择4个,平均一个Bank Machine控制两个Bank(本次试验的DDR3是八个Bank)。

(11)ORDERING:该信号用来决定MIG控制器是否可以对它接收到的指令进行重排序,选择Normal则允许,Strict则禁止。本试验选择Normal,从而获得更高的效率。

(12)Create Custom Part:用于自定义DDR3的型号参数。

配置完成后点击next。

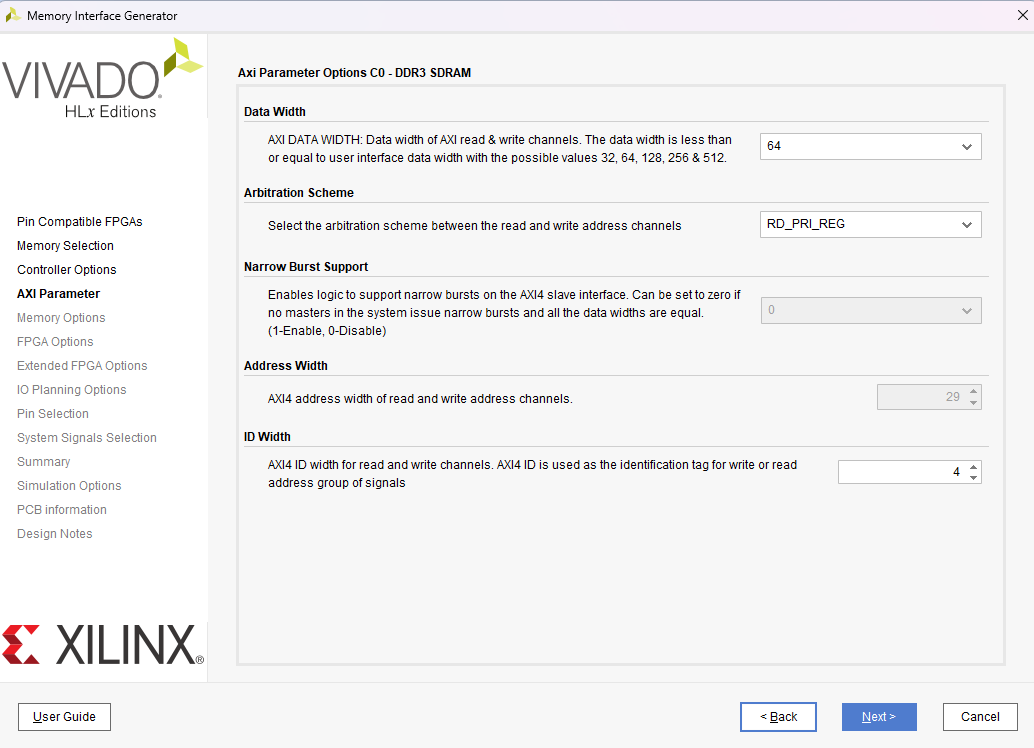

接下来配置AXI接口:

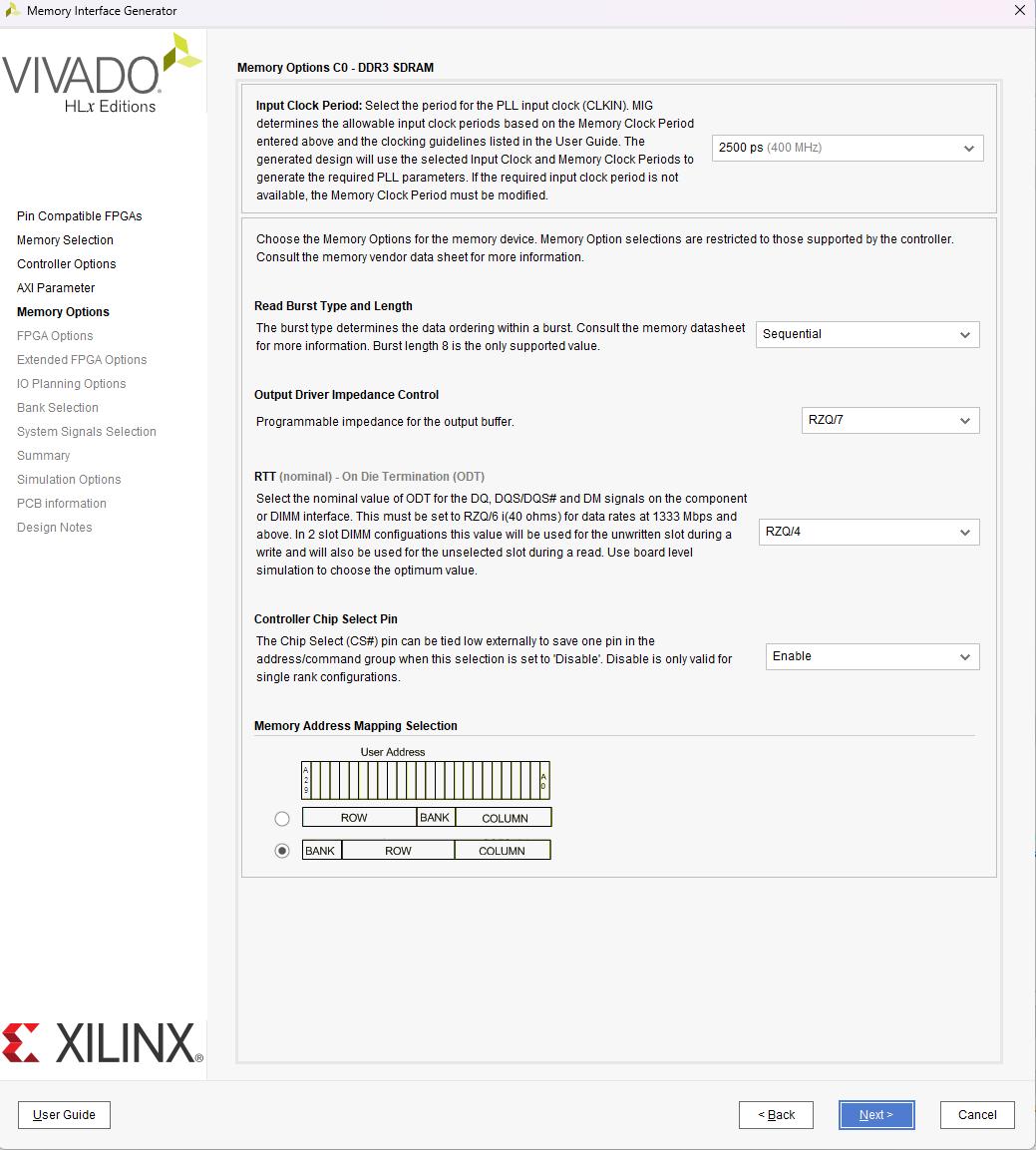

接下来内存的操作方式:

(1)Input Clock Period:MIG IP核的系统输入时钟,该输入时钟由FPGA内部产生,本次试验选择的时钟频率为5000ps(200MHz)。在Vivado软件20.2版本中存在一个软件BUG。生成IP后重新打开,会变成2500ps(400MHz),后续修改IP时注意此处。

(2)Read Burst Type and Length:突发类型选择,突发类型有顺序突发和交叉突发两种,本试验选择顺序突发,其突发长度固定为8。

(3)Output Driver Impdance Control:输出阻抗控制。本试验选择RZQ/7。

(4)RTT:终结电阻,可进行动态控制,本次试验选择RZQ/4。

(5)Controller Chip Select Pin:片选管脚输出使能。本试验选择enable,表示把片选信号cs#引出来,由外部控制。

(6)BANK_ROW_COLUMN:寻址方式选择。本试验选择第二种,即BANK-ROW-COLUMN的形式,这是一种常见的DDR3寻址方式,即要指定某个地址,先指定Bank,再指定行,最后指定列,这样就确定了一个具体地址。一般来说这样寻址有利于降低功耗,但是读写性能上不如ROW_BANK_COLUMN。配置完成点击NEXT。

接下来配置FPGA的操作模式:

(1)System Clock:MIG IP核输入时钟。本试验选择NO Buffer,因为IP核的输入时钟是单端时钟,是由内部MMCM产生的,MMCM所产生的时钟默认添加了buffer。

(2)Reference Clock:MIG IP核的参考时钟,同样选择NO Buffer,将有时钟模块生成。感兴趣的用户也可以选择Use System Clock这个选项。这时候的MIG IP系统时钟同时做了参考时钟,IP核的参考时钟要求是200MHz,而MIG IP核的系统时钟刚好也使用了200MHz的系统时钟。

(3)System Reset Polarity:复位有效电平选择。本试验选择ACTIVE LOW低电平有效。

(4)Debug Signals Control:该选项用于控制MIG IP核是否把一些调试信号引出来,他会自动添加到ILA,这些信号也包括一些DDR3芯片的校准状态信息。本试验选择OFF,不需要让IP核产生各种调试信息。

(5)Sample Data Depth:采样深度选择。当Debug Signals Control选择OFF时,所有的采样深度时不可选的。

(6)Internal Vref:内部参考管脚,表示某些参考管脚当成普通的输入管脚使用。由于开发板的IO资源较为紧张,因此这里要选择ON,把参考管脚当作普通的输入管脚来使用。

(7)IO Power Reduction:IO管脚节省功耗设置。本试验选择ON,开启。

(8)XADC Instantiation:XADC模块的例化。使用MIG IP核运行的时候需要进行温度补偿,可以直接选择XADC模块的温度数据引到MIG IP核来使用,否则需要额外提供温度数据,所以本试验选择Enable。配置完成点击NEXT。

接下来配置内部高性能bank端接匹配阻抗的设置,这里不去改它,默认50欧姆即可。接下来点击NEXT。

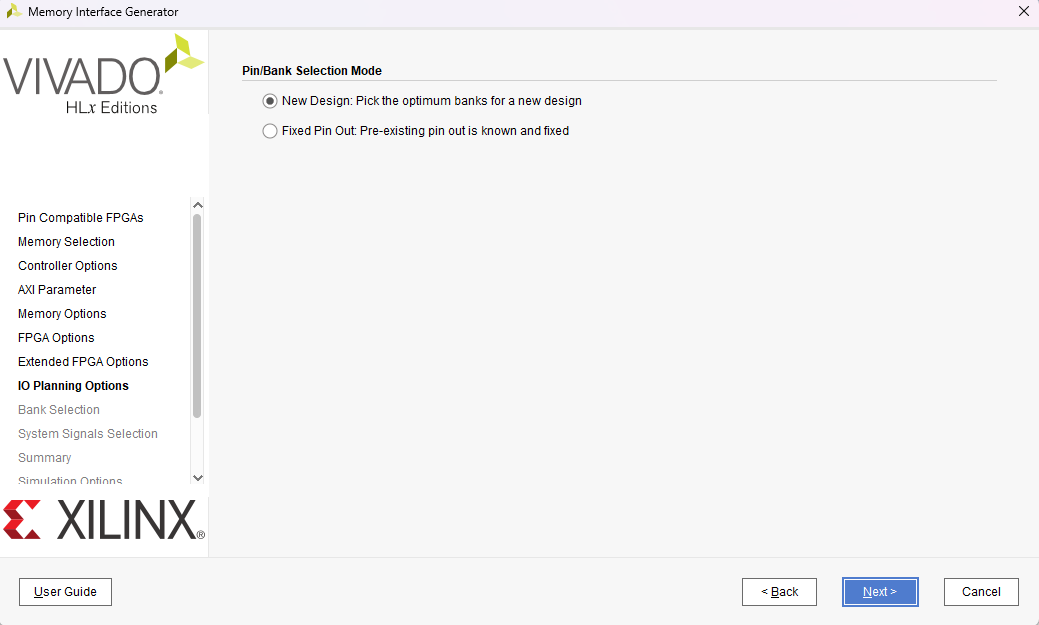

接下来开始绑定管脚,这里我们选用预先设置好的管脚,选择Fixed Pin选项,点击NEXT。

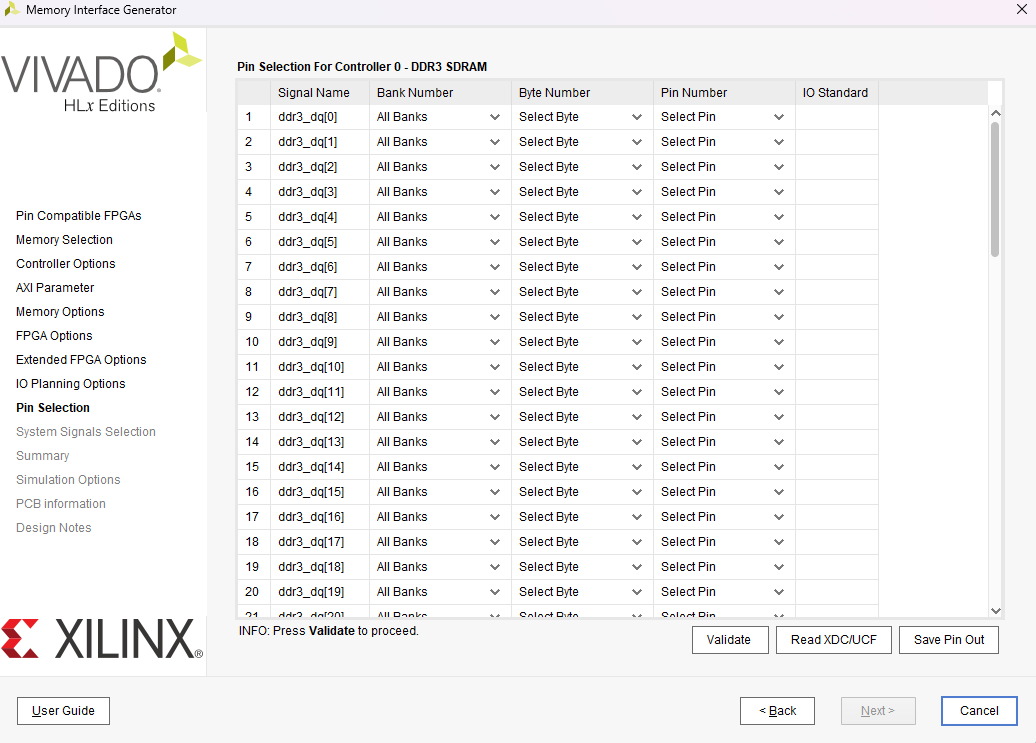

进入下图界面后,选择Read XDC/UCF选项。选择预先设置好的DDR3配置文件,然后点击Validate。弹出对话框后点击Ok。管脚配置完成,点击NEXT。

配置基本设置完成,后面都是一些查看和接受,直接点击NEXT即可。

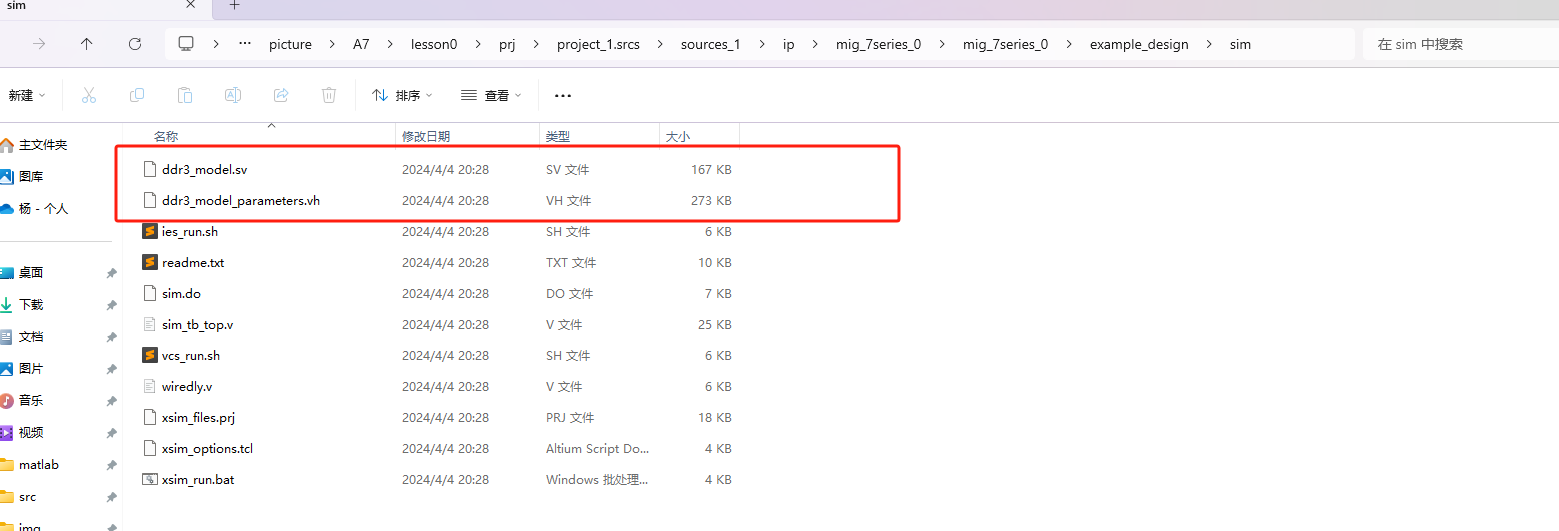

DDR3的仿真配置文件在生成IP核的同时也会生成,文件位置如下图所示:

这篇关于DDR3接口的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!