本文主要是介绍vivado下ddr3的读写和测试详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

最近博主在根据例程做ddr3的读写测试,发现根本看不到好吧,虽然之前博主做过SDRAM的读写测试,但是ddr3更加复杂,时序写起来很吃力,所以需要用到vivado下自带的ip核。具体来看下面例化过程:

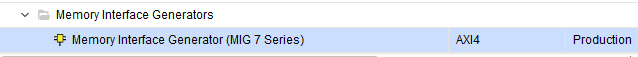

1.在ip核下搜索mig 双击打开

2.直接next 然后在当前界面修改你的ddr3ip核的名字

这里博主是因为已经例化了ip核,所以名字不能修改,然后next

3.这是要不要兼容芯片,不选,点击next

4.勾选你的存储器类型,我的是ddr3,点击next

5.

这个配置比较多,第一个时钟为ddr3实际工作的时钟,然后选择你的内存型号,数据宽度即可,点击next

6.

然后输入时钟可能需要pll倍频得到,一般是200Mhz,这里注意看下最后一行的用户地址类型,它是由bank+row+column组成的,这个在后面的读写测试会进一步提到。

7.

时钟选择不差分,然后参考时钟为用户时钟。

8.下面就是默认next,然后就是分配管脚了,这个你买的开发板一般都会提高ucf文件,直接复制就行。

然后next,生成。

以上就是ip核的简单例化过程,这个步骤网上有很多类似的,博主就不一一讲解了,把精力放在读写测试这块。

首先来看老三样:ip核用户界面下的控制命令,读和写

这是控制命令,可以让用户来发送读或者写命令,需要注意的事只有当app_rdy和app_en同为高时才有效,命令被发出。这里博主通过ila上电分析发现app_rdy为ip核自己产生的输出信号,但是它并不是一直都是高电平,所以在后续的读写测试时需要判断,至于怎么判断,我们后面代加上电分析。

上面是写命令,可以看到当add_wdf_wren和add_wdf_end同为高时数据才能有效被写进去,同时app_wdf_rdy也要为高。需要注意的一点是,写数据和写命令此时不再有关系,为什么,因为写数据其实是通过fifo缓存,当写命令有效时,由于先进先出的特性会把它所对应数据给写入,当然这个很拗口,下面会给出示例

上面的是读过程,可以看出当读命令发出后需要一个延迟读数据才会有效。

下面来看代码进行讲解:

module mem_burst

#(parameter MEM_DATA_BITS = 64,parameter ADDR_BITS = 24

)

(input rst, /*复位*/input mem_clk, /*接口时钟*/input rd_burst_req, /*读请求*/input wr_burst_req, /*写请求*/input[9:0] rd_burst_len, /*读数据长度*/input[9:0] wr_burst_len, /*写数据长度*/input[ADDR_BITS - 1:0] rd_burst_addr, /*读首地址*/input[ADDR_BITS - 1:0] wr_burst_addr, /*写首地址*/output rd_burst_data_valid, /*读出数据有效*/output wr_burst_data_req, /*写数据信号*/output[MEM_DATA_BITS - 1:0] rd_burst_data, /*读出的数据*/input[MEM_DATA_BITS - 1:0] wr_burst_data, /*写入的数据*/output rd_burst_finish, /*读完成*/output wr_burst_finish, /*写完成*/output burst_finish, /*读或写完成*////output[ADDR_BITS-1:0] app_addr,output[2:0] app_cmd,output app_en,output [MEM_DATA_BITS-1:0] app_wdf_data,output app_wdf_end,output [MEM_DATA_BITS/8-1:0] app_wdf_mask,output app_wdf_wren,input [MEM_DATA_BITS-1:0] app_rd_data,input app_rd_data_end,input app_rd_data_valid,input app_rdy,input app_wdf_rdy,input ui_clk_sync_rst, input init_calib_complete

);assign app_wdf_mask = {MEM_DATA_BITS/8{1'b0}};localparam IDLE = 3'd0;

localparam MEM_READ = 3'd1;

localparam MEM_READ_WAIT = 3'd2;

localparam MEM_WRITE = 3'd3;

localparam MEM_WRITE_WAIT = 3'd4;

localparam READ_END = 3'd5;

localparam WRITE_END = 3'd6;

localparam MEM_WRITE_FIRST_READ = 3'd7;/*parameter IDLE = 3'd0;

parameter MEM_READ = 3'd1;

parameter MEM_READ_WAIT = 3'd2;

parameter MEM_WRITE = 3'd3;

parameter MEM_WRITE_WAIT = 3'd4;

parameter READ_END = 3'd5;

parameter WRITE_END = 3'd6;

parameter MEM_WRITE_FIRST_READ = 3'd7;*/

reg[2:0] state;

reg[9:0] rd_addr_cnt;

reg[9:0] rd_data_cnt;

reg[9:0] wr_addr_cnt;

reg[9:0] wr_data_cnt;reg[2:0] app_cmd_r;

reg[ADDR_BITS-1:0] app_addr_r;

reg app_en_r;

reg app_wdf_end_r;

reg app_wdf_wren_r;

assign app_cmd = app_cmd_r;

assign app_addr = app_addr_r;

assign app_en = app_en_r;

assign app_wdf_end = app_wdf_end_r;

assign app_wdf_data = wr_burst_data;

assign app_wdf_wren = app_wdf_wren_r & app_wdf_rdy;

assign rd_burst_finish = (state == READ_END);

assign wr_burst_finish = (state == WRITE_END);

assign burst_finish = rd_burst_finish | wr_burst_finish;assign rd_burst_data = app_rd_data;

assign rd_burst_data_valid = app_rd_data_valid;assign wr_burst_data_req = (state == MEM_WRITE) & app_wdf_rdy ;always@(posedge mem_clk or posedge rst)

beginif(rst)beginapp_wdf_wren_r <= 1'b0;endelse if(app_wdf_rdy)app_wdf_wren_r <= wr_burst_data_req;

endalways@(posedge mem_clk or posedge rst)

beginif(rst)beginstate <= IDLE;app_cmd_r <= 3'b000;app_addr_r <= 0;app_en_r <= 1'b0;rd_addr_cnt <= 0;rd_data_cnt <= 0;wr_addr_cnt <= 0;wr_data_cnt <= 0;app_wdf_end_r <= 1'b0;endelse if(init_calib_complete === 1'b1)begincase(state)IDLE:beginif(rd_burst_req)beginstate <= MEM_READ;app_cmd_r <= 3'b001;app_addr_r <= {rd_burst_addr,3'd0};app_en_r <= 1'b1;endelse if(wr_burst_req)beginstate <= MEM_WRITE;app_cmd_r <= 3'b000;app_addr_r <= {wr_burst_addr,3'd0};app_en_r <= 1'b1;wr_addr_cnt <= 0;app_wdf_end_r <= 1'b1;wr_data_cnt <= 0;endendMEM_READ:beginif(app_rdy)beginapp_addr_r <= app_addr_r + 8;if(rd_addr_cnt == rd_burst_len - 1)beginstate <= MEM_READ_WAIT;rd_addr_cnt <= 0;app_en_r <= 1'b0;endelserd_addr_cnt <= rd_addr_cnt + 1;endif(app_rd_data_valid)begin//app_addr_r <= app_addr_r + 8;if(rd_data_cnt == rd_burst_len - 1)beginrd_data_cnt <= 0;state <= READ_END;endelsebeginrd_data_cnt <= rd_data_cnt + 1;endendendMEM_READ_WAIT:beginif(app_rd_data_valid)beginif(rd_data_cnt == rd_burst_len - 1)beginrd_data_cnt <= 0;state <= READ_END;endelsebeginrd_data_cnt <= rd_data_cnt + 1;endendendMEM_WRITE_FIRST_READ:beginapp_en_r <= 1'b1;state <= MEM_WRITE;wr_addr_cnt <= 0;endMEM_WRITE:beginif(app_rdy)beginapp_addr_r <= app_addr_r + 8;if(wr_addr_cnt == wr_burst_len - 1)beginapp_wdf_end_r <= 1'b0;app_en_r <= 1'b0;endelsebeginwr_addr_cnt <= wr_addr_cnt + 1;endendif(wr_burst_data_req)begin//app_addr_r <= app_addr_r + 8;if(wr_data_cnt == wr_burst_len - 1)begin state <= MEM_WRITE_WAIT;endelsebeginwr_data_cnt <= wr_data_cnt + 1;endendendREAD_END:state <= IDLE;MEM_WRITE_WAIT:beginif(app_rdy)beginapp_addr_r <= app_addr_r + 'b1000;if(wr_addr_cnt == wr_burst_len - 1)beginapp_wdf_end_r <= 1'b0;app_en_r <= 1'b0;if(app_wdf_rdy) state <= WRITE_END;endelsebeginwr_addr_cnt <= wr_addr_cnt + 1;endendelse if(~app_en_r & app_wdf_rdy)state <= WRITE_END;endWRITE_END:state <= IDLE;default:state <= IDLE;endcaseend

end

endmodule这个是黑金给的例程,一开始没看懂,搞了好几天才看懂整个细节,下面来讲解一下:首先state在IDLE状态,当wr_burst_req有效时进入MEM_WRITE状态,这时候有两个条件判断,第一个if(app_rdy)为真,说明写命令是有效的,那么随之伴随的是地址的累加,同时也会计数,如果写命令发送了128次,就结束。第二个if(wr_burst_data_req)为真,注意wr_burst_data_req为真实际就是app_wdf_rdy为真,所以写的数据是被缓存到了fifo并且当读命令有效时会依次传入,这里大家会问,为啥不让app_rdy和app_wdf_rdy同时为真才地址增加和写数据呀,这是因为app_rdy和app_wdf_rdy并不是一直都为高电平,下面是上电结果;

看到没,rdy为低时,app_wdf_rdy为高,这说明数据此时相对于地址来说多写进去一次,那么多的那个数据就被缓存了,等到下一个rdy为高就会去写入之前那个缓存的数据而不是当前时刻的数据。这也就是为什么每个条件判断语句都会去计数,一个计的是多少个写命令被发出,另一个是多少个写的数据被发送。

下面来看下读过程,首先state在IDLE状态,当rd_burst_req有效时进入MEM_READ状态,这里同样有两个if判断,第一个if(app_rdy)是用来判断读命令是否有效并且地址累加,第二个if(app_rd_data_valid)是读数据有效,根据上面的读流程,读数据有效并不会随着读命令有效就马上出现,一般会延迟多个周期,所以同样需要分开判断并且计数。来看时序:

看到没,当读请求有效时,下一个时钟周期地址就开始计数并且累计了,但是app_rd_data_valid还需延迟一会才能有效。

其实把读写原理搞懂后就很简单,博主一开始卡住的地方就是写的那块,以为写数据需要app_rdy和app_wdf_rdy同时有效才能成功写入,没有搞懂命令和数据的关系,因为ip核的写数据是先缓存在fifo中的,所以即使当前写命令无效时,写数据依旧可以成功写入。感觉是不是和SDRAM不一样啊,可能没用ip核和用了还是有区别的吧。。。

感觉ddr3的时序重要的还是这两点,其他的至于如何精确地址和数据对应,可以具体分析,会发现程序写的还是很严谨的啊。。。

这篇关于vivado下ddr3的读写和测试详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!