cxl专题

SK Hynix明年将开发基于96/128 GB DDR5的CXL 2.0内存解决方案

SK Hynix 正致力于为人工智能领域开发基于 DDR5 的 CXL 2.0 内存解决方案,尤其是针对"内存饥渴型"LLM。CXL 指的是 Compute Express Link,这是一种互联技术,可以在 CPU 和 GPU 之间实现更快的数据传输,但在人工智能领域,它实际上是 CPU 和加速器之间的数据传输。 与传统的 PCIe 接口相比,CXL 的优势在于它能让 GPU 直接访问系统内

FMS 2024:多家厂商CXL技术方案总览

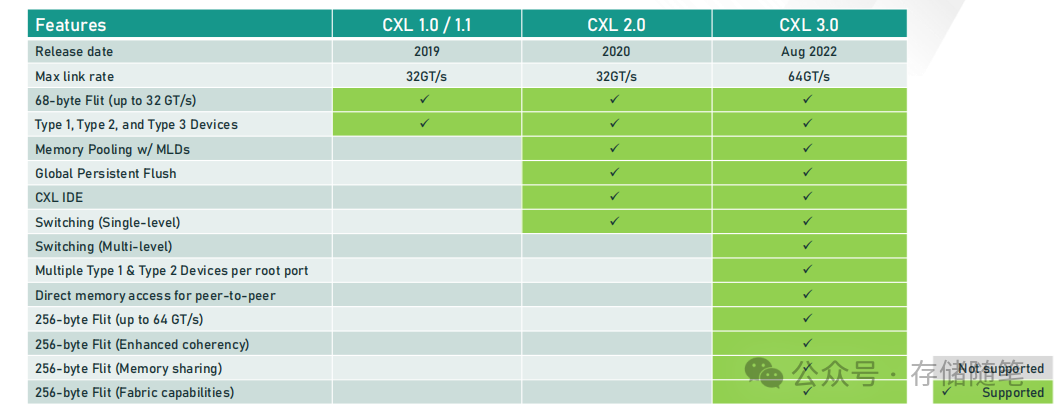

CXL(Compute Express Link)联盟自成立以来一直是FMS闪存峰会的常客。在2022年的峰会上,CXL联盟宣布了CXL 3.0版本规范,随后在2023年的超级计算大会上推出了CXL 3.1版本。起初,CXL作为一种主机到设备的互联标准,逐渐吸收了其他竞争标准,如OpenCAPI和Gen-Z。通过在普遍存在的PCIe扩展总线上构建协议,CXL规范开始覆盖各种应用场景。 C

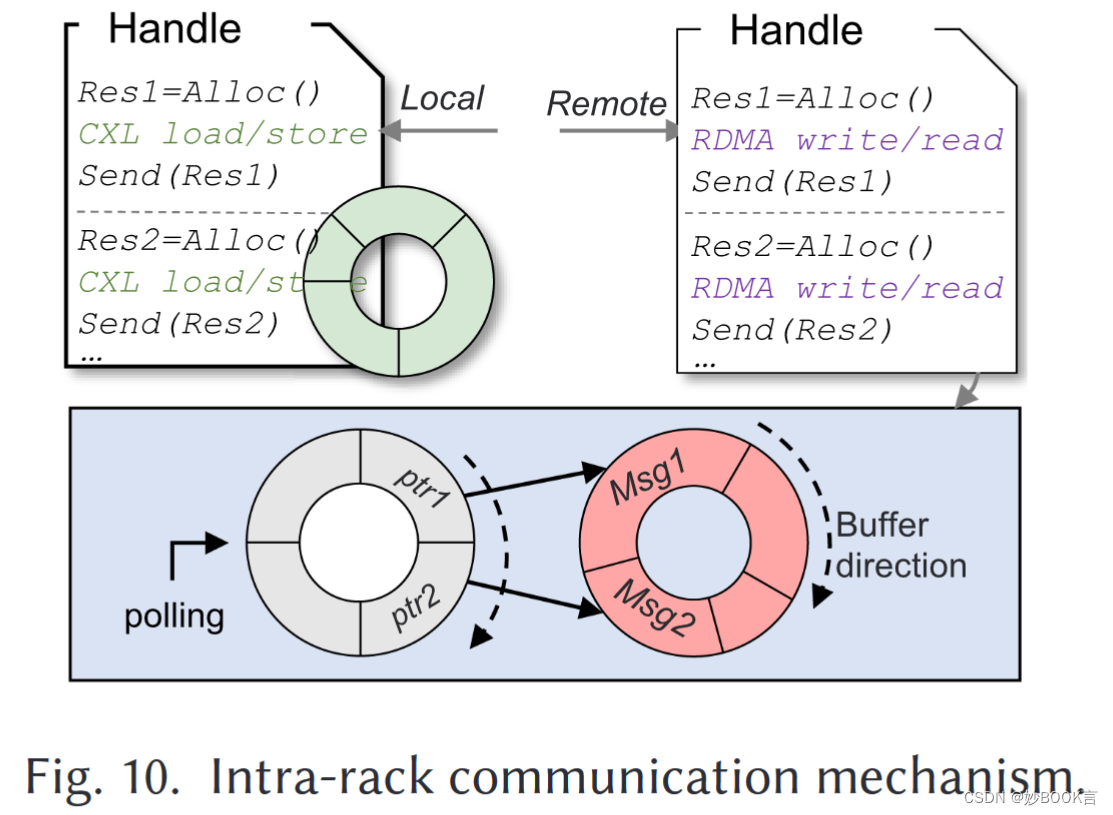

Rcmp: Reconstructing RDMA-Based Memory Disaggregation via CXL——论文阅读

TACO 2024 Paper CXL论文阅读笔记整理 背景 RDMA:RDMA是一系列协议,允许一台机器通过网络直接访问远程机器中的数据。RDMA协议通常固定在RDMA NIC(RNIC)上,具有高带宽(>10 GB/s)和微秒级延迟(~2μs),这些协议得到了InfiniBand、RoCE和OmniPath等公司的广泛支持[20, 47, 62]。RDMA基于两种类型的操作原语提供数据传输

CXL协议中 Register Locator DVSEC详解

✨ 前言: Register Locator DVSEC(Designated Vendor-Specific Extended Capability)是一种PCI Express(PCIe)配置空间的能力,专为CXL(Compute Express Link)技术中的设备设计。这包括CXL根端口、CXL下行交换端口、CXL上行交换端口以及非RCD(即非寄存器配置数据)设备。这项能力的主旨是帮助

如何利用CXL技术突破内存墙?-2

为了解决这些问题,业界正积极寻求新的技术和标准,比如Compute Express Link (CXL),它旨在通过提供标准化的高速互连来提高内存带宽、降低延迟,并简化内存扩展的软件集成,从而有效地打破内存墙的限制。 通过使用CXL(Compute Express Link)技术来突破内存墙,可以实现以下几项关键改进,比如一个CXL控制器厂商测试方案: 增加服务器内存带宽和容量50%

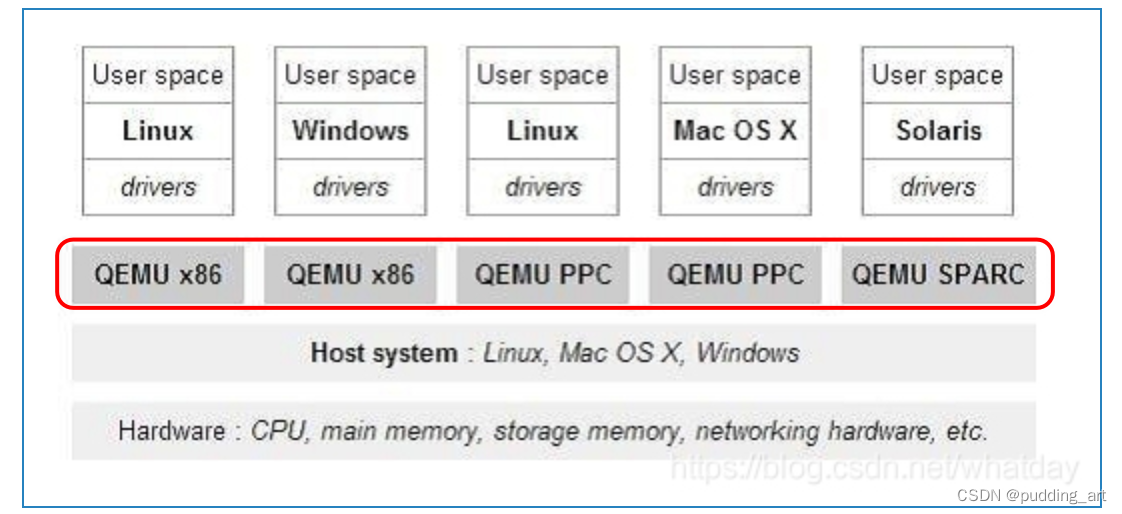

关于QEMU模拟器本身以及和CXL功能模拟相关内容的学习

前言:在写Paper的时候,发现直接引用QEMU官网关于QEMU的介绍实在是一个图省事儿的方法,但是并不可取。即使是一小段,也要去真正了解QEMU的基本原理,如何实现功能模拟,以及目前实现的与CXL相关的内容。 注:本文主要是一些概念性的内容,关于具体如何通过QEMU模拟CXL type 3 设备,已经有其他文章阐述,在此不赘述。 需要关注以下几个问题: QEMU是什么?QEMU有哪些工

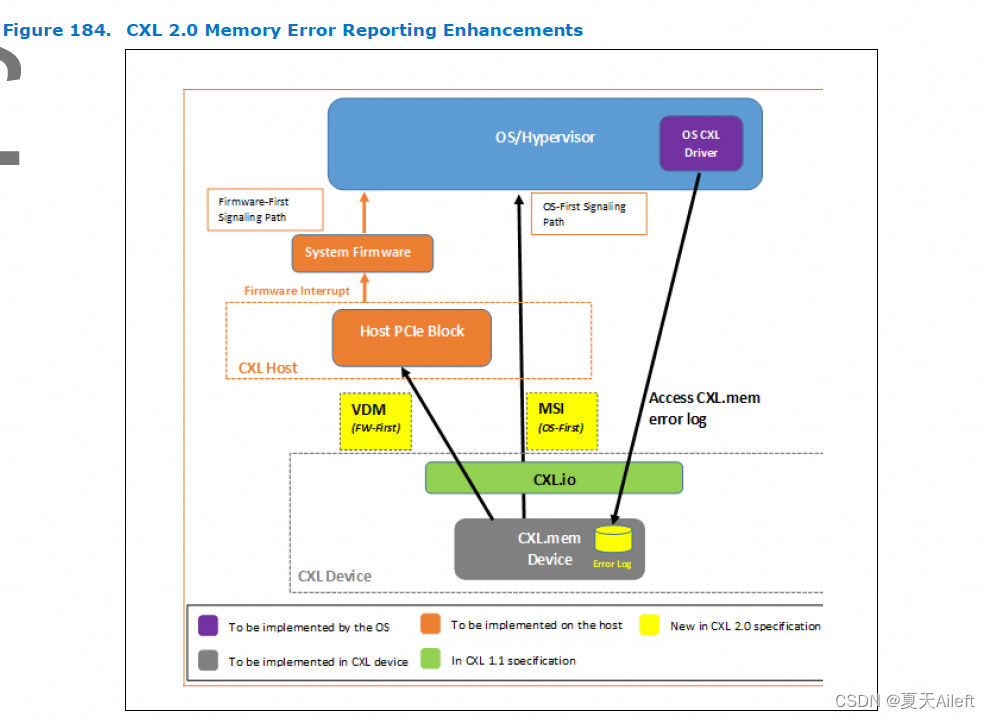

【CXL协议-RAS(12)】

前言: 在了解本章之前,咱们先来了解一下什么是RAS RAS是可靠性(Reliability)、可用性(Availability)和服务性(Serviceability)的缩写,这是衡量系统设计和架构质量的关键指标。在CXL协议中,RAS功能被设计来确保数据的准确传输,减少系统错误,提供错误检测与修正机制,以及支持高效的系统管理和维护。 CXL协议的RAS特性可以细分为以下几个方面: 1.错误

【CXL协议-ARB/MUX层(5)】

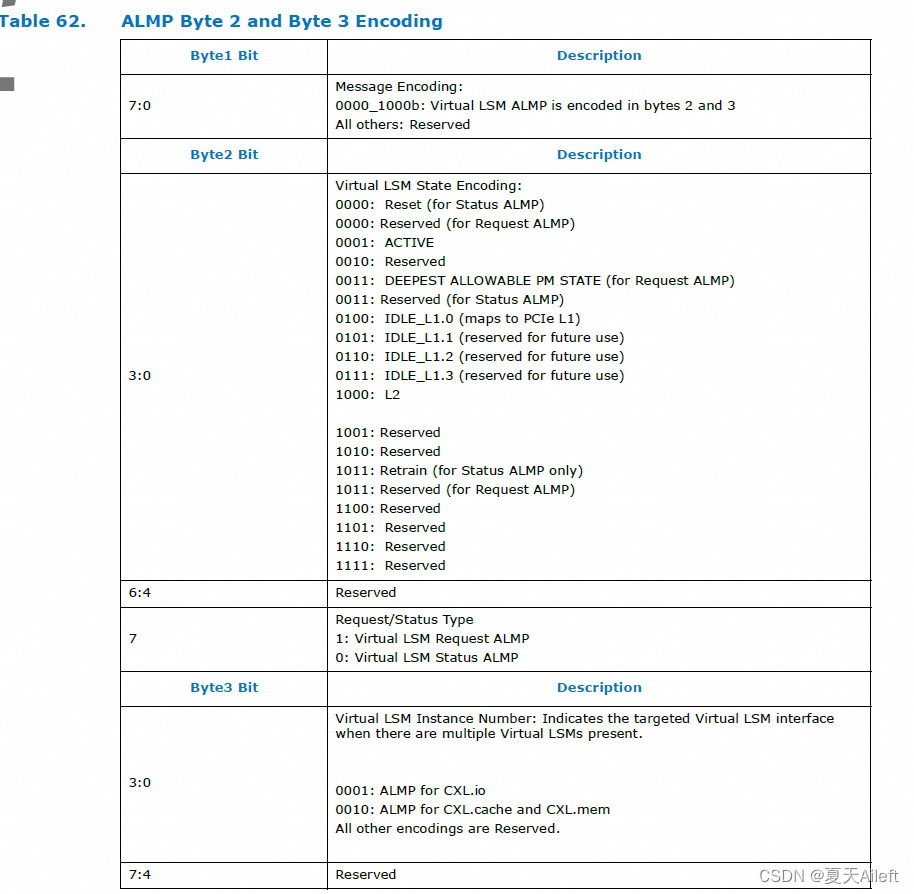

5.0 Compute Express Link ARB/MUX 前言: 在CXL协议中,ARB/MUX层(Arbitration/Multiplexer layer)是负责管理资源共享和数据通路选择的一层。CXL协议包含了几个子协议,主要有CXL.io、CXL.cache 和 CXL.memory。ARB/MUX层在这些子协议之间起到了关键的调度和选择作用,以确保数据流和控制流的正确传输。 下

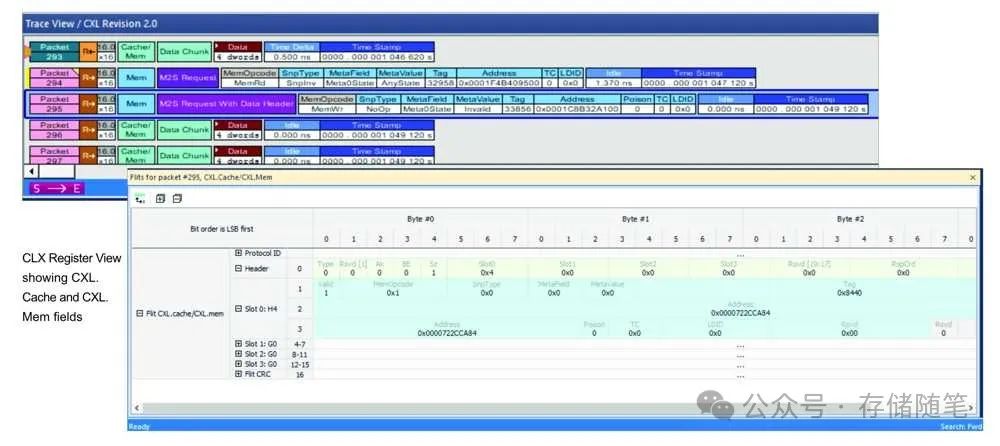

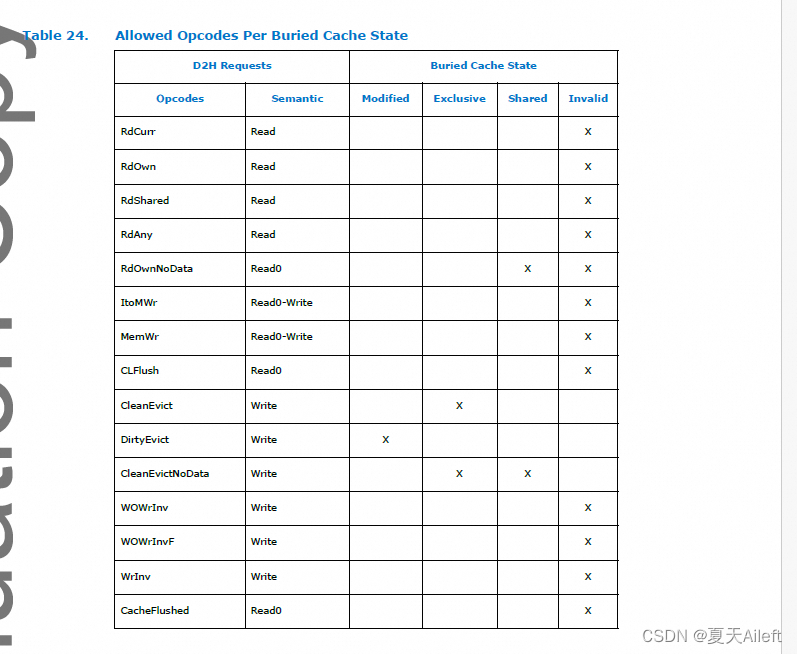

【CXL协议-事务层之CXL.cache (3)】

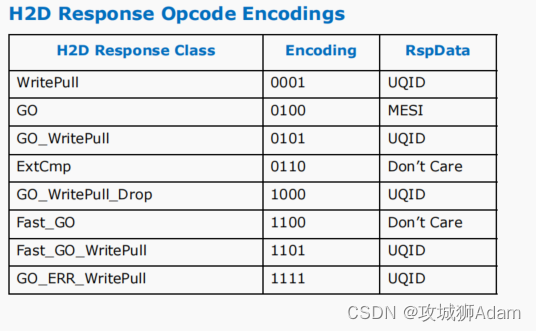

3.2 CXL.cache 3.2.1 概述 CXL.cache 协议将设备和主机之间的交互定义为许多请求,每个请求至少有一个关联的响应消息,有时还有数据传输。 该接口由每个方向的三个通道组成: 请求、响应和数据。 这些通道根据其方向命名,D2H(设备到主机)和 H2D(主机到设备)以及它们携带的事务、请求、响应和数据,如图 20 所示。独立通道允许不同类型的消息使用专用线路 并实现解耦和每线

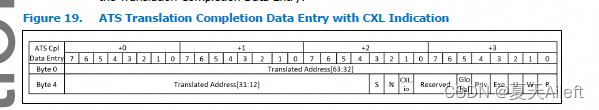

【CXL协议-事务层之CXL.io(3)】

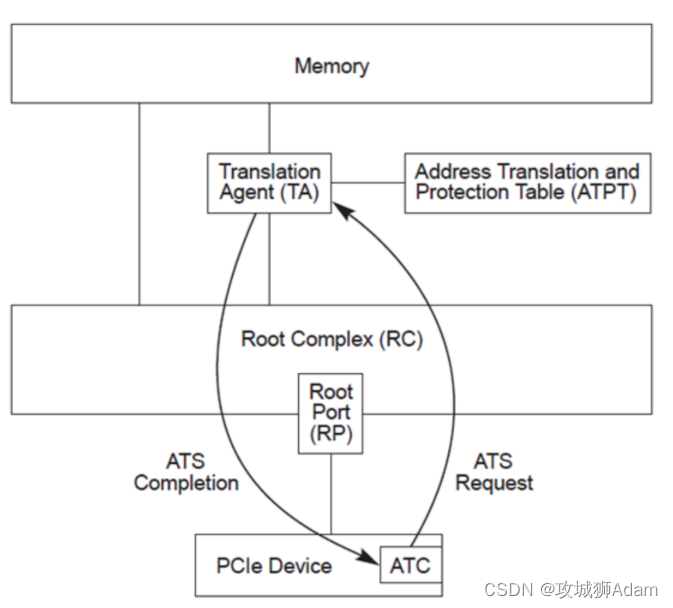

3.1 CXL.io CXL.io 为 I/O 设备提供非一致的加载/存储接口。 图 14 显示了 CXL.io 事务层在 Flex Bus 分层结构中的位置。 交易类型、交易数据包格式、基于信用的流量控制、虚拟通道管理和交易排序规则遵循PCIe定义; 请参阅 有关详细信息,请参阅 PCI Express 基本规范的“事务层规范”一章。 本章重点介绍 CXL.io 使用的值得注意的 PCIe 操

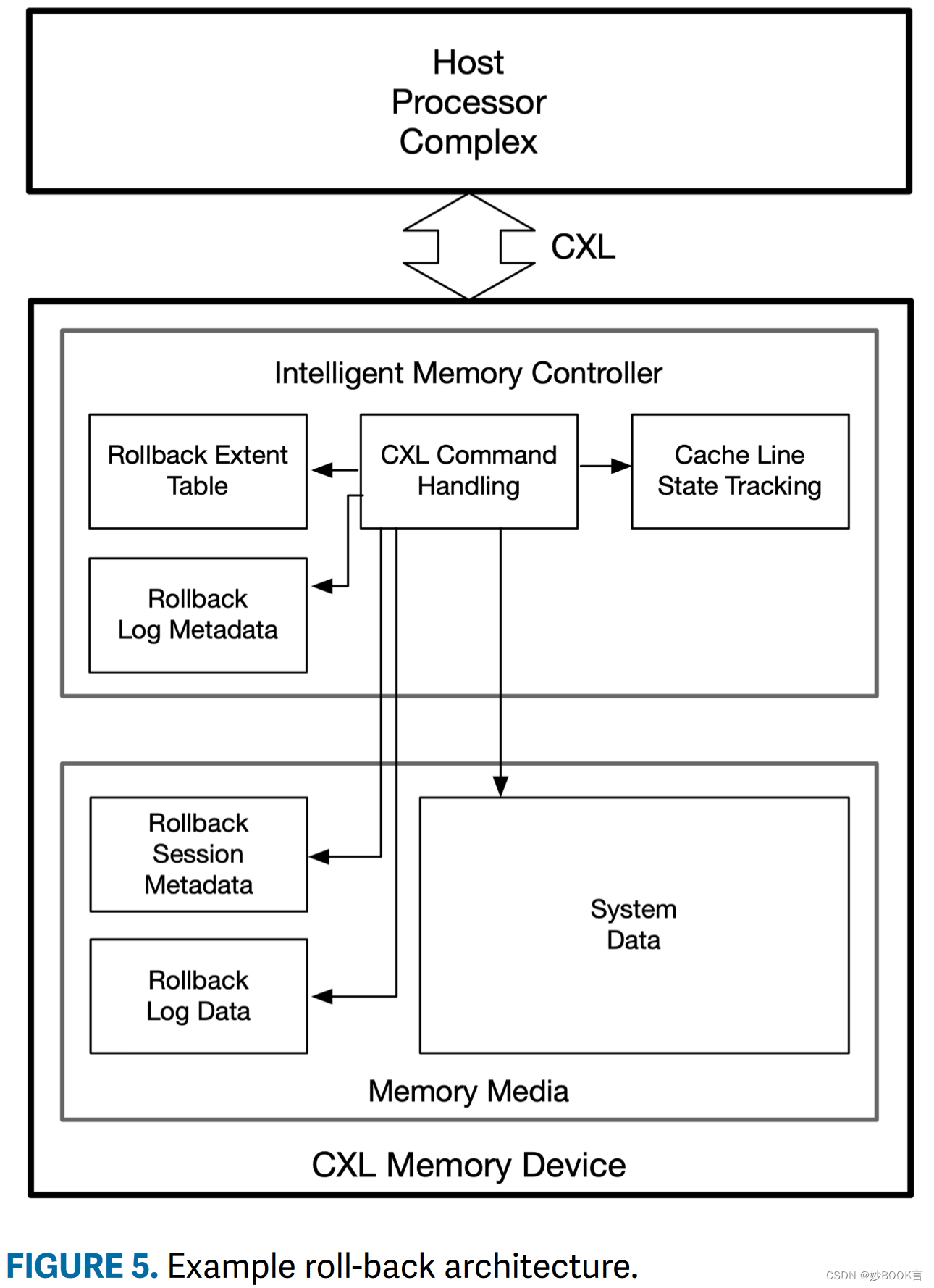

CXL-Enabled Enhanced Memory Functions——论文阅读

IEEE Micro 2023 Paper CXL论文阅读笔记整理 问题 计算快速链路(CXL)协议是系统社区的一个重要里程碑。CXL提供了标准化的缓存一致性内存协议,可用于将设备和内存连接到系统,同时保持与主机处理器的内存一致性。CXL使加速器(例如,GPU和DPU)既能直接加载/存储对主机存储器的访问,又能使它们自己的设备上存储器同样可由CPU访问。CXL允许在内存数据平面上插入技术,所以

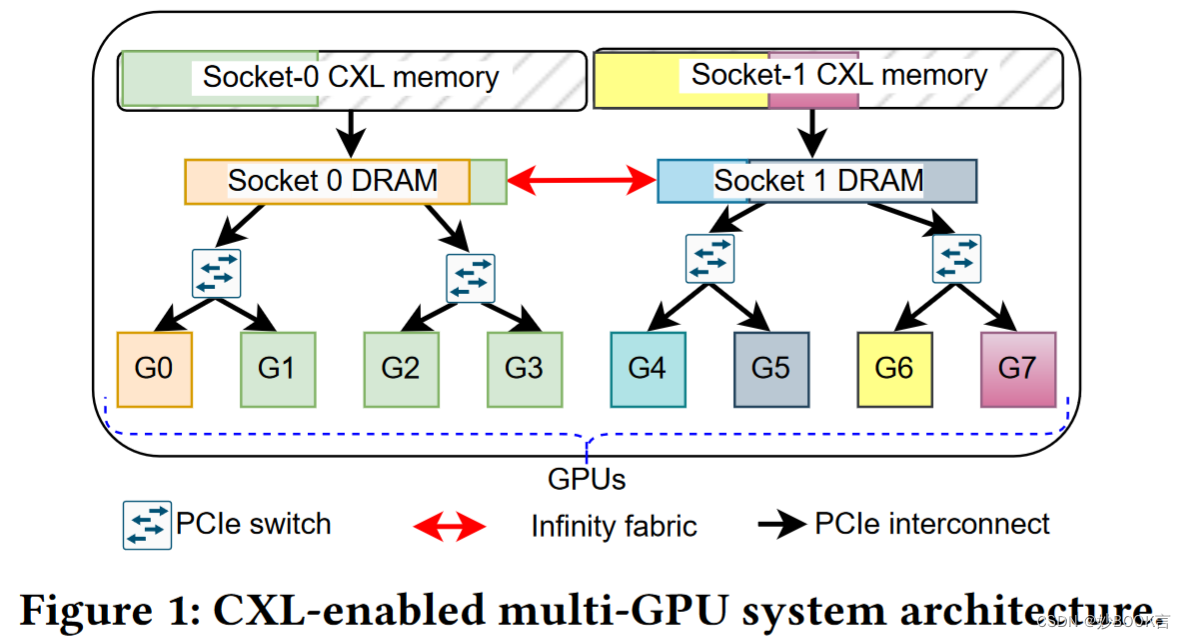

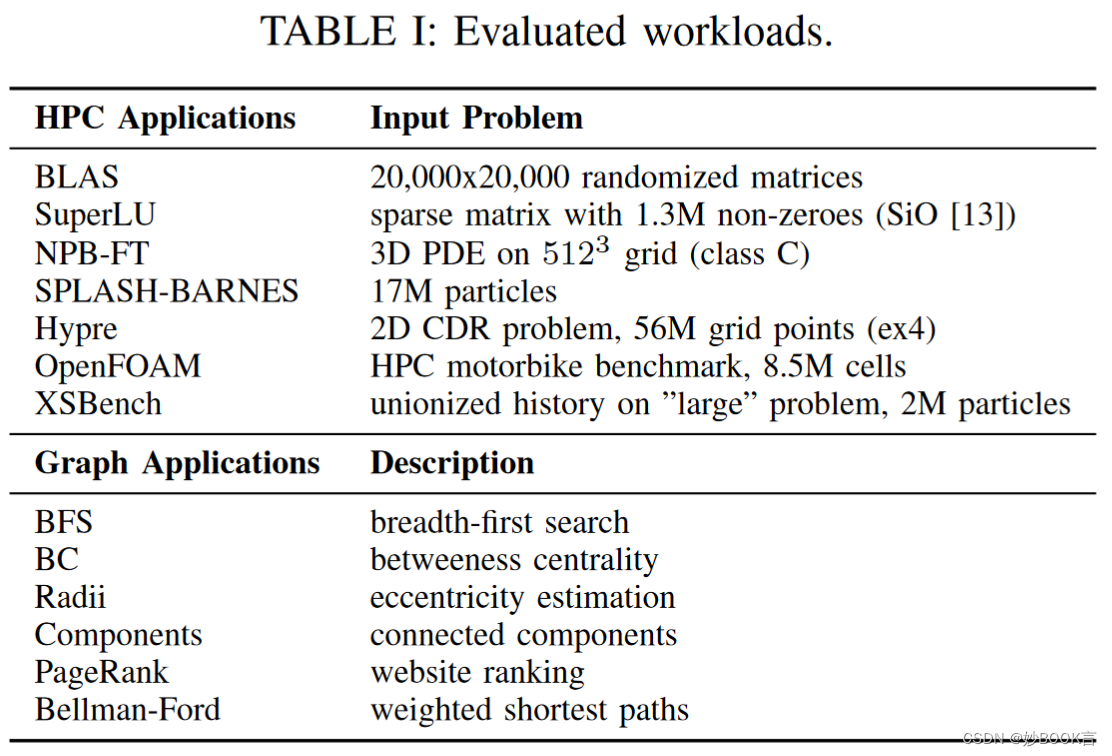

Accelerating Performance of GPU-based Workloads Using CXL——论文泛读

FlexScience 2023 Paper CXL论文阅读笔记整理 问题 跨多GPU系统运行的高性能计算(HPC)工作负载,如科学模拟和深度学习,是内存和数据密集型的,依赖于主机内存来补充其有限的板载高带宽内存(HBM)。为了促进在慢速设备到主机PCIe互连之间更快的数据传输,这些工作负载通常将内存固定在主机系统上,但对同一节点的对等GPU上运行的工作负载的主机内存造成内存容量限制。(预留部

Evaluating Emerging CXL-enabled Memory Pooling for HPC Systems——论文泛读

MCHPC@SC 2022 Paper CXL论文阅读汇总 问题 当前的高性能计算(HPC)系统提供的内存资源是静态配置的,并与计算节点紧密耦合。然而,HPC系统上的工作负载正在演变。多样化的工作负载导致对可配置内存资源的需求,以实现高性能和高利用率。 现有方法局限性 CXL是用于互连处理器、加速器和内存的开放标准。符合CXL标准的硬件提供了对应用程序代码透明的低延迟、高带宽数据访问。一些

CXL RAS功能简介

一般来说,RAS(可靠性、可用性和可服务性)是计算机硬件和系统设计中的重要概念。 在CXL(Compute Express Link)接口中,RAS功能包括以下方面: 错误检测和纠正:CXL可能支持各种错误检测和纠正机制,如ECC(Error Correction Code)内存,以检测并修正数据传输过程中的错误。 热插拔和热替换:CXL设备可能支持热插拔和热替换功能,允许在系统运行时添加

什么是CXL(Compute Express Link)技术?一文读懂CXL

CXL(Compute Express Link)技术?一文读懂CXL 一、前言二、CXL技术概览2.1、什么是CXL技术?2.2、CXL技术的三种模式:http://CXL.io、CXL.cache和CXL.memory 三、CXL技术的优势四、CXL技术的应用4.1、计算机系统中的应用4.2、数据中心中的应用4.3、人工智能领域中的应用 五、CXL技术与其他技术的对比六、实现CXL技术的

CXL是什么?它是如何工作的?

关注、星标公众号,精彩内容每日送达来源:网络素材 、 本文由半导体产业纵横(ID:ICVIEWS)编译自spiceworks 高带宽互连彻底改变了以数据为中心的计算。 CXL(Compute Express Link)可以提高数据中心内存的性能、可扩展性和灵活性。MemVerge 的 Steve Scargall 解释了 CXL 是什么、它是如何工作的,以及为什么它是各种应用程序的游戏规则改

CXL Meta Data 介绍

🔥点击查看精选 CXL 系列文章🔥 🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥 📢 声明: 🥭 作者主页:【MangoPapa的CSDN主页】。⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/131841883】。⚠️ 本文目的为 个人学习记录 及 知识分享。因

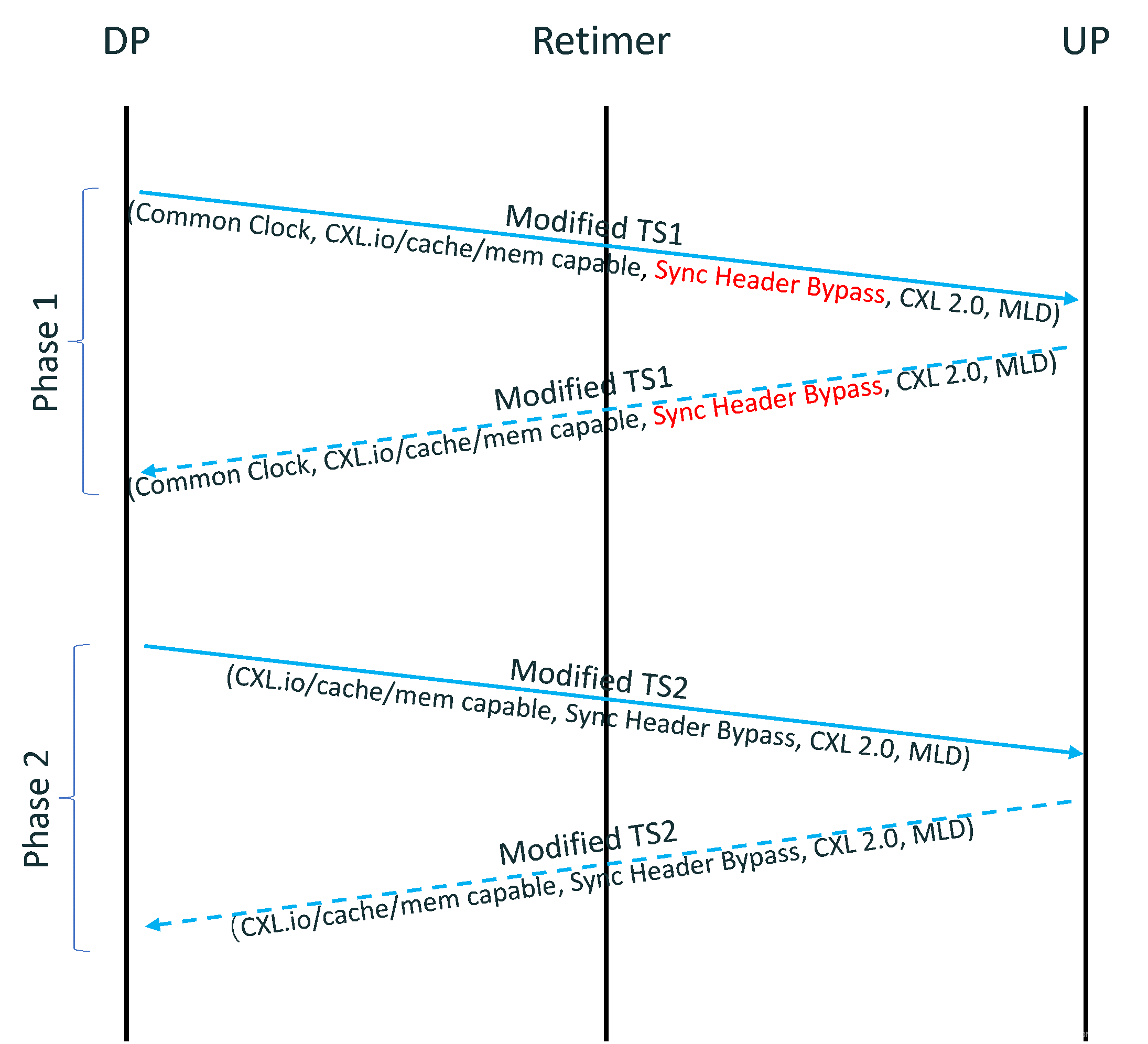

基于 APN 的 CXL 链路训练

🔥点击查看精选 CXL 系列文章🔥 🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥 📢 声明: 🥭 作者主页:【MangoPapa的CSDN主页】。⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/132129387】。⚠️ 本文目的为 个人学习记录 及 知识分享。因

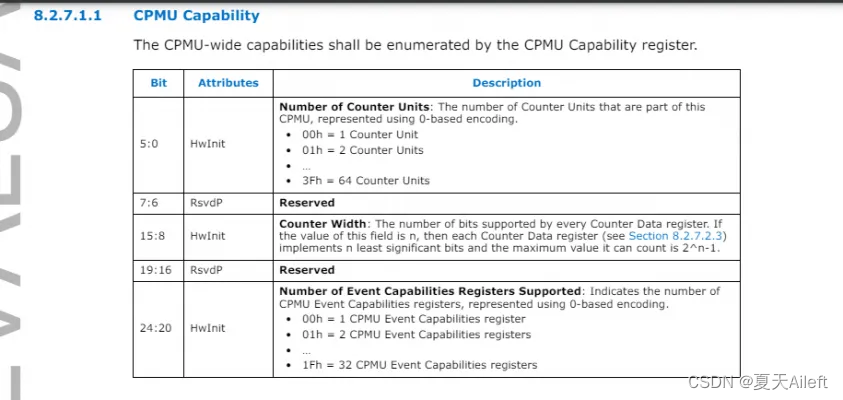

CXL QoS Telemetry 介绍

🔥点击查看精选 CXL 系列文章🔥 🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥 📢 声明: 🥭 作者主页:【MangoPapa的CSDN主页】。⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/131745195】。⚠️ 本文目的为 个人学习记录 及 知识分享。因

CXL寄存器介绍(2)- CXL DVSEC

🔥点击查看精选 CXL 系列文章🔥 🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥 📢 声明: 🥭 作者主页:【MangoPapa的CSDN主页】。⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/132553156】。⚠️ 本文目的为 个人学习记录 及 知识分享。因

CXL 存储设备标签存储区(LSA)

🔥点击查看精选 CXL 系列文章🔥 🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥 📢 声明: 🥭 作者主页:【MangoPapa的CSDN主页】。⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/132553168】。⚠️ 本文目的为 个人学习记录 及 知识分享。因