本文主要是介绍CXL协议中 Register Locator DVSEC详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

✨ 前言:

Register Locator DVSEC(Designated Vendor-Specific Extended Capability)是一种PCI Express(PCIe)配置空间的能力,专为CXL(Compute Express Link)技术中的设备设计。这包括CXL根端口、CXL下行交换端口、CXL上行交换端口以及非RCD(即非寄存器配置数据)设备。这项能力的主旨是帮助这些设备实现额外的寄存器块,以便更好地配置和管理CXL技术提供的高级功能。

🌟DVSEC的主要作用包括:

寄存器块定位:DVSEC能力向软件公开了在PCIe配置空间内CXL 2.0根端口、下游交换端口、上游交换端口和CXL 2.0设备相关的寄存器块的位置。这对于软件正确配置和管理这些端口和设备至关重要。

支持多寄存器块条目:一个DVSEC实例可以包含一个或多个寄存器块条目。这意味着DVSEC提供了一种灵活的方式来描述多个相关寄存器块的位置信息,从而支持复杂的硬件功能。

标准化配置空间访问:通过在PCIe配置空间中实现DVSEC能力,CXL硬件组件的配置和管理可以遵循统一的标准。这有助于提高系统的可扩展性和互操作性,同时简化了软件的开发。

促进CXL和PCIe技术的集成:CXL是建立在PCIe基础上的互连技术,DVSEC强化了两者之间的集成。它允许软件利用标准PCIe机制来发现和配置CXL特定的高级功能,这样可以无缝地在系统中融合使用PCIe和CXL技术。

🌟实践中的应用:

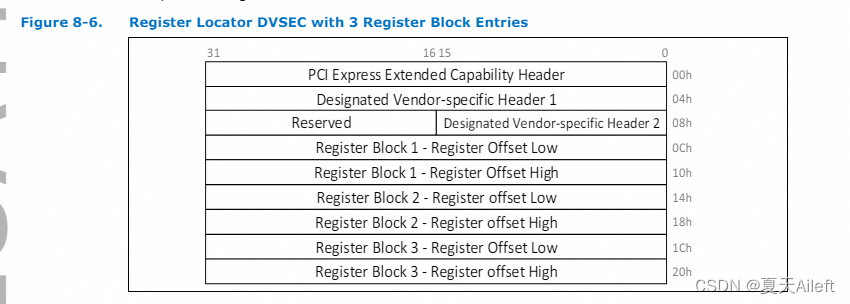

一个Register Locator DVSEC实例中包含3个寄存器块:

寄存器块1:

Designated Vendor-specific Header开始于00h。

Register Block 1 - Register Offset Low在0Ch。

Register Block 1 - Register Offset High在10h。

寄存器块2:

Reserved Designated Vendor-specific Header开始于08h。

Register Block 2 - Register Offset Low在14h。

Register Block 2 - Register Offset High在18h。

寄存器块3:

Register Block 3 - Register Offset Low在1Ch。

Register Block 3 - Register Offset High继续往下。

🌟Register Locator DVSEC

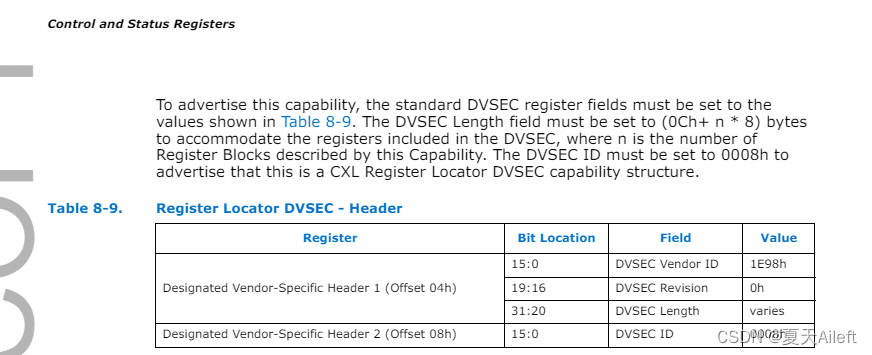

如何在pcie的cap中找到Register Locator DVSEC的偏移呢?

要在PCI Express (PCIe) 配置空间中找到 Register Locator DVSEC,您需要寻找具有DVSEC ID为0008h的PCIe设备的扩展能力(capability)。PCIe配置空间包括一系列的标准和供应商特定的能力,这些能力通过链接的列表结构连接。每个能力都有一个头部,其中包含能力的ID和指向下一个能力的指针。

通过Register Locator DVSEC 找到CXL中CPMU Registers,步骤大致如下:

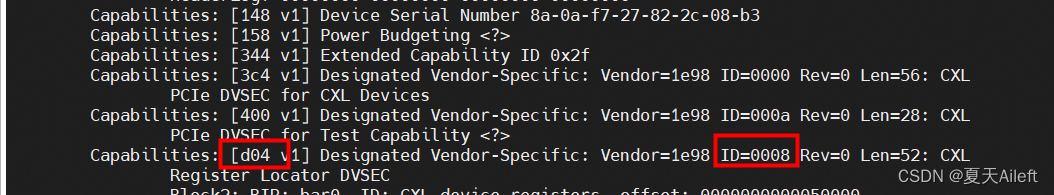

🌟1. 首先找到Register Locator DVSEC 的偏移

lspci -s 你的bdf -vvv

对应cap的base addr为d04。

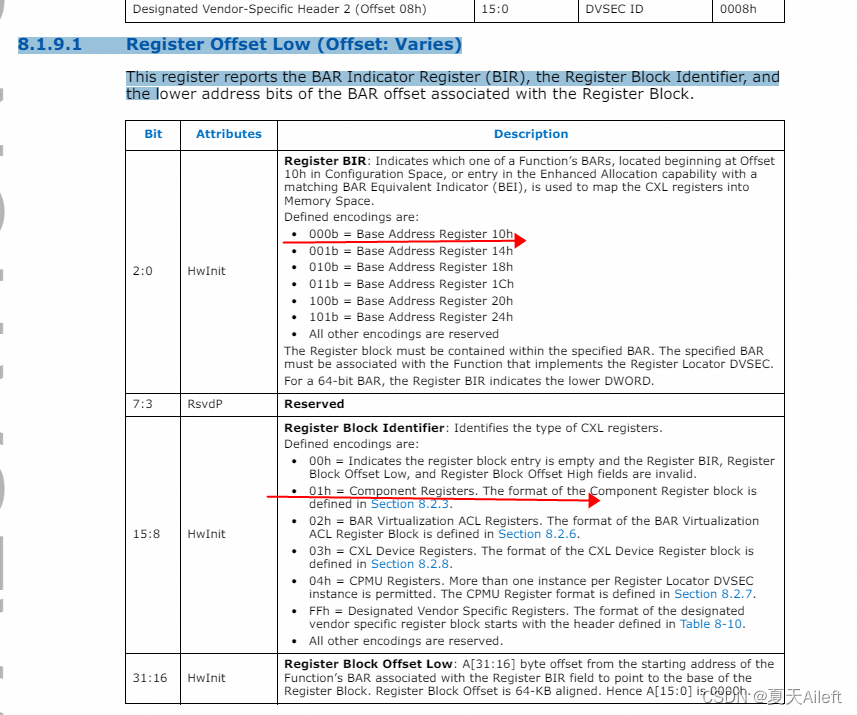

🌟2.读取Register offset Low寄存器

根据协议BAR寄存器信息(Register BIR)位于Register offset Low的 bit【2:0】,Componet registers的Register Block Identifier(01h)位于Register offset Low的 bit【15:8】,如下图:

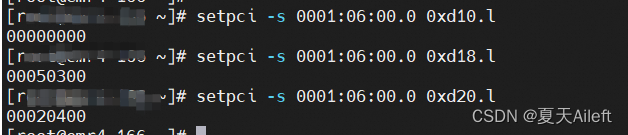

Register offset Low位于Register Locator DVSEC Cap + offset (0xc):即 0xd04 + 0xc= 0xd10.

🌟3. 定位CPMU register

读取Register offset Low的寄存器bit 2:0为00,代表是在Bar0上

如上图我们读到的CXL设备的地址中 Register Block 3 0xd04 + 0x1c=0xd20,代表的是CPMU Registers,因为读到的数据中bit2:0为00b代表是在BAR0上,bit15:8为0x4代表CPMU Registers,bit31:16为0x2,并且寄存器块偏移量为 64 KB 对齐,这里需要低位补0为0x20000,至此我们确定了CPMU register是在Register Block 3 上。

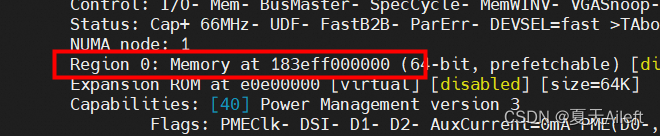

读取CXL EP设备的MMIO BAR0地址,可以通过lspci工具查看设备的MMIO的地址,Region0代表BAR0

然后通过这个地址0x183eff000000 + 0x20000

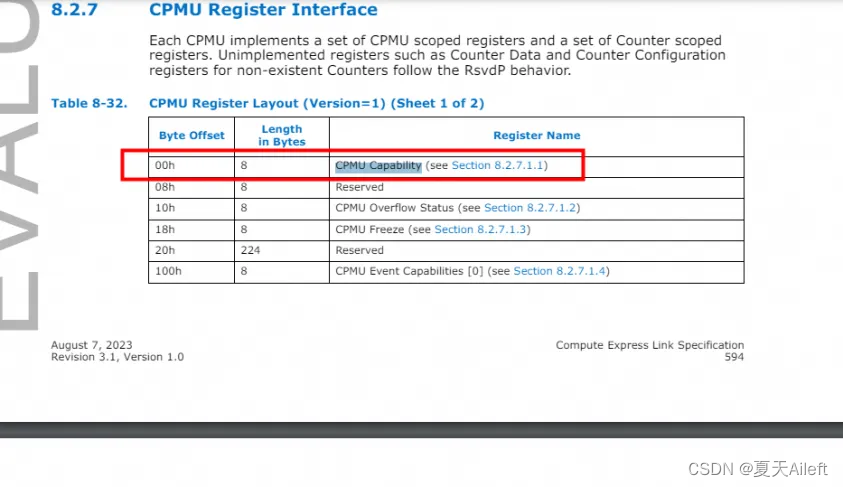

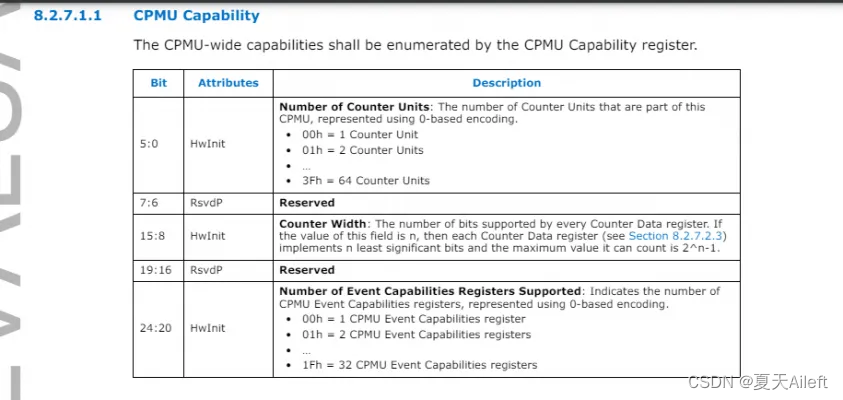

🌟4. 读取 CPMU Capability

从协议里可以看CPMU Capability 是的偏移为00h,读取的地址就是0x183eff020000,后续所有的CPMU的寄存器偏移都是通过这个基地址来加偏移,可以通过devmem工具来读取对应的寄存器

这篇关于CXL协议中 Register Locator DVSEC详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!