本文主要是介绍EtherCAT主站DEMO介绍 总线部分包括 EtherCAT 协议、Canopen 协议、1588 同步协议,全部在 FPGA上实现,纯 Verilog 实现,无软核,时间精准,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

EtherCAT 总线 demo 板介绍

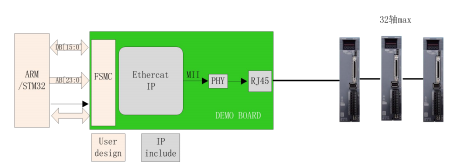

一、测试架构介绍

- 总线部分包括 EtherCAT 协议、Canopen 协议、1588 同步协议,全部在 FPGA上实现,纯 Verilog 实现,无软核,时间精准。

- FPGA 挂百兆网口串接伺服,布线简单。

-

- 支持驱动 1-32 轴,自动侦测。

- CPU 和 FPGA 的接口,根据 CPU 的不同而不同,常用的如 FSMC 接口、GPMC接口、PCI/PCIE 接口等等。

- 运动控制部分用户可以选择在 STM32、ARM、X86 等 CPU 上实现 (此部分代码 demo 板不包含)

- DEMO 板具备参数固定自动运行模式,可测试总线的通讯和驱动器侦测运行正常。

- 图中 User design 部分为用户自行设计。

- 图中 IP include 部分为 demo 或 IP 提供的。

二、具体性能参数

1、循环周期和抖动

- 循环周期支持 31.25us、62.5us、125us、250us、500us、1ms、2ms 等。

- 主站在循环周期 2ms 时抖动为 50us,循环周期越短,抖动越小,从站抖动10ns。

2、支持轴数与 FPGA 资源消耗量

- 支持 1-32 轴,消耗资源 12K 逻辑 Slice 左右,如用户有自己的 IP 或功能模块需要集成,则建议采用 30K 资源的

FPGA

这篇关于EtherCAT主站DEMO介绍 总线部分包括 EtherCAT 协议、Canopen 协议、1588 同步协议,全部在 FPGA上实现,纯 Verilog 实现,无软核,时间精准的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!