锁相环专题

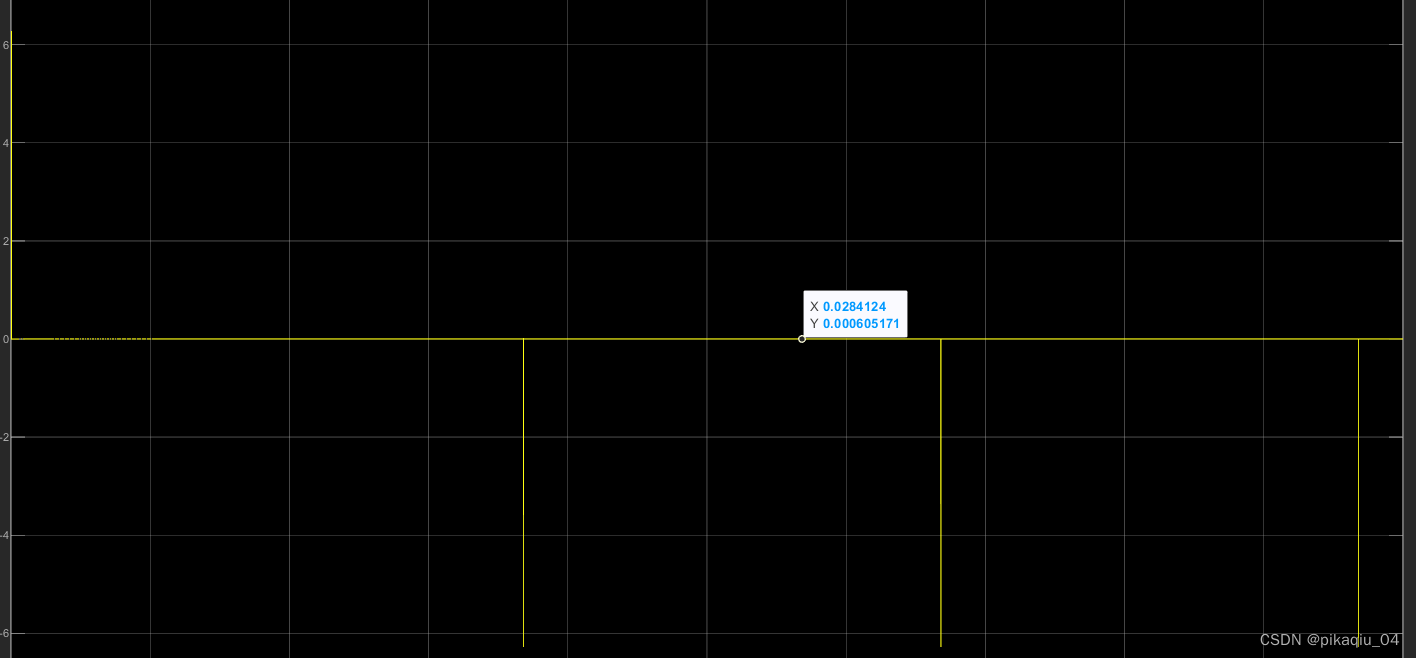

【MATLAB源码-第258期】基于matlab的16QAM调制解调COSTAS环载波同步仿真,对比前后星座图,输出锁相环响应曲线。

操作环境: MATLAB 2022a 1、算法描述 16QAM(16 Quadrature Amplitude Modulation,16阶正交幅度调制)是一种常用的数字调制方式,它通过改变载波信号的相位和幅度来传输信息。相比于QPSK,16QAM在同样的带宽下能够传输更多的比特信息,因为它使用了16个不同的符号,每个符号可以表示4个比特的数据。这种调制方式在现代通信系统中广泛应用,特别是在

锁相环(PLL)经典书籍分享(可下载)

锁相环(PLL)作为一种确保系统同步的控制机制,广泛应用于频率合成、时钟恢复、信号调制与解调等多个方面。 探索锁相环(PLL)技术的深度和广度,最有效的途径之一便是通过专业书籍的系统学习。以下是为渴望掌握PLL知识的读者精心挑选的几本必备书籍,它们将引导您从基础理论到高级应用,全面深入地理解PLL的设计与应用。 《锁相环(PLL)电路设计与应用》 作者:远坂俊昭 对于想要深入学习PLL

【MATLAB源码-第28期】基于matlab的16QAM定时同步仿真,采用gardner算法,Costa锁相环。

操作环境: MATLAB 2022a 1、算法描述 正交幅度调制(QAM,Quadrature Amplitude Modulation)是一种在两个正交载波上进行幅度调制的调制方式。这两个载波通常是相位差为90度(π/2)的正弦波,因此被称作正交载波。这种调制方式因此而得名。 同其它调制方式类似,QAM通过载波某些参数的变化传输信息。在QAM中,数据信号由相互正交的两个载波的幅度变化表示

一文搞懂晶振和锁相环

.晶振 晶振为单片机工作产生时钟频率,不同子系统需要不同频率时,用锁相环提供所需要的时钟频率。 1.晶体(crystal)与晶振(oscillator): 1.晶振=振荡器=有源晶振=oscillator 电路上一般简写为XO 晶体=谐振器=无源晶振=crystal 电路上一般简写为XTAL 2.晶体为无源的,一般两个管脚,需要起振电路(如MCU外接晶体+起振电容C1、C

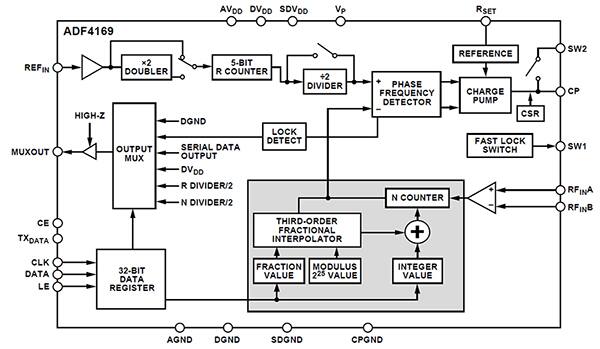

锁相环频率合成器的基本原理

本文摘自:使用 PLL 频率合成器生成时钟|DigiKey 作者:Art Pini 投稿人:DigiKey 北美编辑 2021-02-03 高速串行通信总线的数据速率在不断提高,这就要求系统时钟具有更高的频率、卓越的稳定性、更高的频率分辨率和更高的信号纯度。直接数字合成器就拥有这些特性,但只限于在 2 或 3 千兆赫兹 (GHz) 以下的频率。对于高达几十千兆赫的频率,则需要一个解决方案。

ADRV9009的供电要求和集成锁相环

ADRV9009的供电要求 芯片有如下不同的用电端,各路供电载流要求( 模拟供电端需要使用低噪声LDO来提供低噪声电源): (1) VDDA1P3 Analog 的供电网络载流要求为3A . (2) VDDD1P3_DIG的供电网络载流要求3A . (3) VDDA1P8_TX,VDDA1P8_BB的供电网络总载流要求为0.6A . (4) VDD_INTERFACE 的供电网络载流要求为

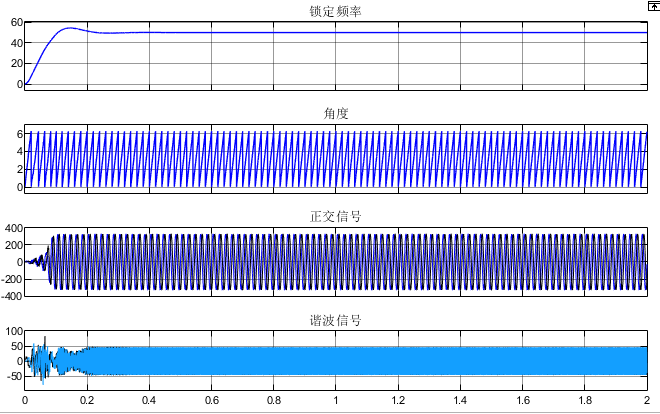

基于级联延迟信号消除的锁相环(CDSC_PLL)技术MATLAB仿真

微❤关注“电气仔推送”获得资料(专享优惠) 基于级联型延迟信号消除(CDSC)的锁相环技术(CDSC-PLL),该锁相环克服了传统dq 锁相环在电网电压畸变或不对称时存在较大稳态误差的缺点。CDSC-PLL是在传统dq锁相环的控制环节中加入了一个 CDSC环节,即dqCDSCPLL。 基于延迟信号消除的锁相环原理 通过谐波的半波对称性在dq坐标系中将谐波消除, 也即延迟信号消除(DSC)法,

基于级联延迟信号消除的锁相环(CDSC_PLL)技术MATLAB仿真

微❤关注“电气仔推送”获得资料(专享优惠) 基于级联型延迟信号消除(CDSC)的锁相环技术(CDSC-PLL),该锁相环克服了传统dq 锁相环在电网电压畸变或不对称时存在较大稳态误差的缺点。CDSC-PLL是在传统dq锁相环的控制环节中加入了一个 CDSC环节,即dqCDSCPLL。 基于延迟信号消除的锁相环原理 通过谐波的半波对称性在dq坐标系中将谐波消除, 也即延迟信号消除(DSC)法,

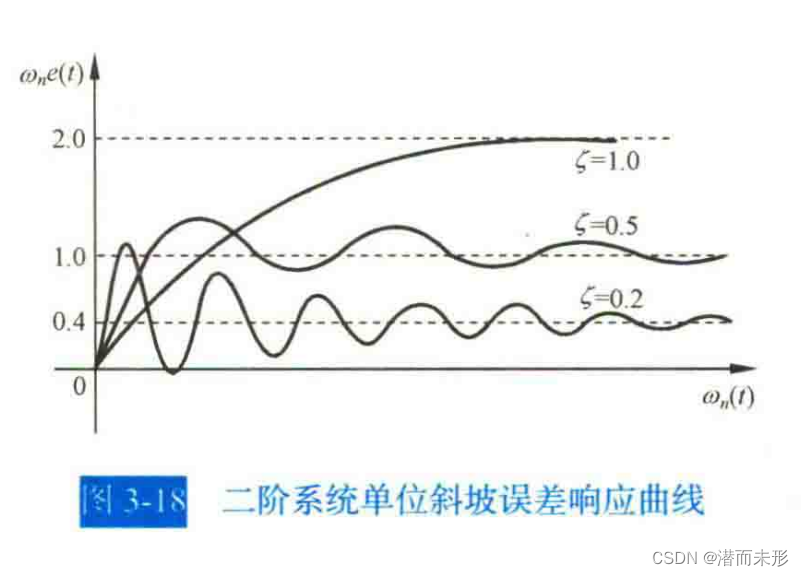

电机控制学习之路:simulink仿真之龙伯格观测器+锁相环的参数设计

前言 本例中使用的参数设计方法,主要思路为将状态观测器的系统矩阵(A+HC)的特征方程的解视作标准二阶系统传递函数的极点,然后根据不同的带宽设计观测器参数。就笔者的仿真结果来看只要带宽不设计的过于离谱,按本文的方法观测速度都能得到一个可用的结果。带宽越大时,观测器所得电角度的相位滞后越小,高频噪声带来的影响就越大。反之,观测器带宽越小,噪声越小,但是所得电角度相位滞后就越大。如果

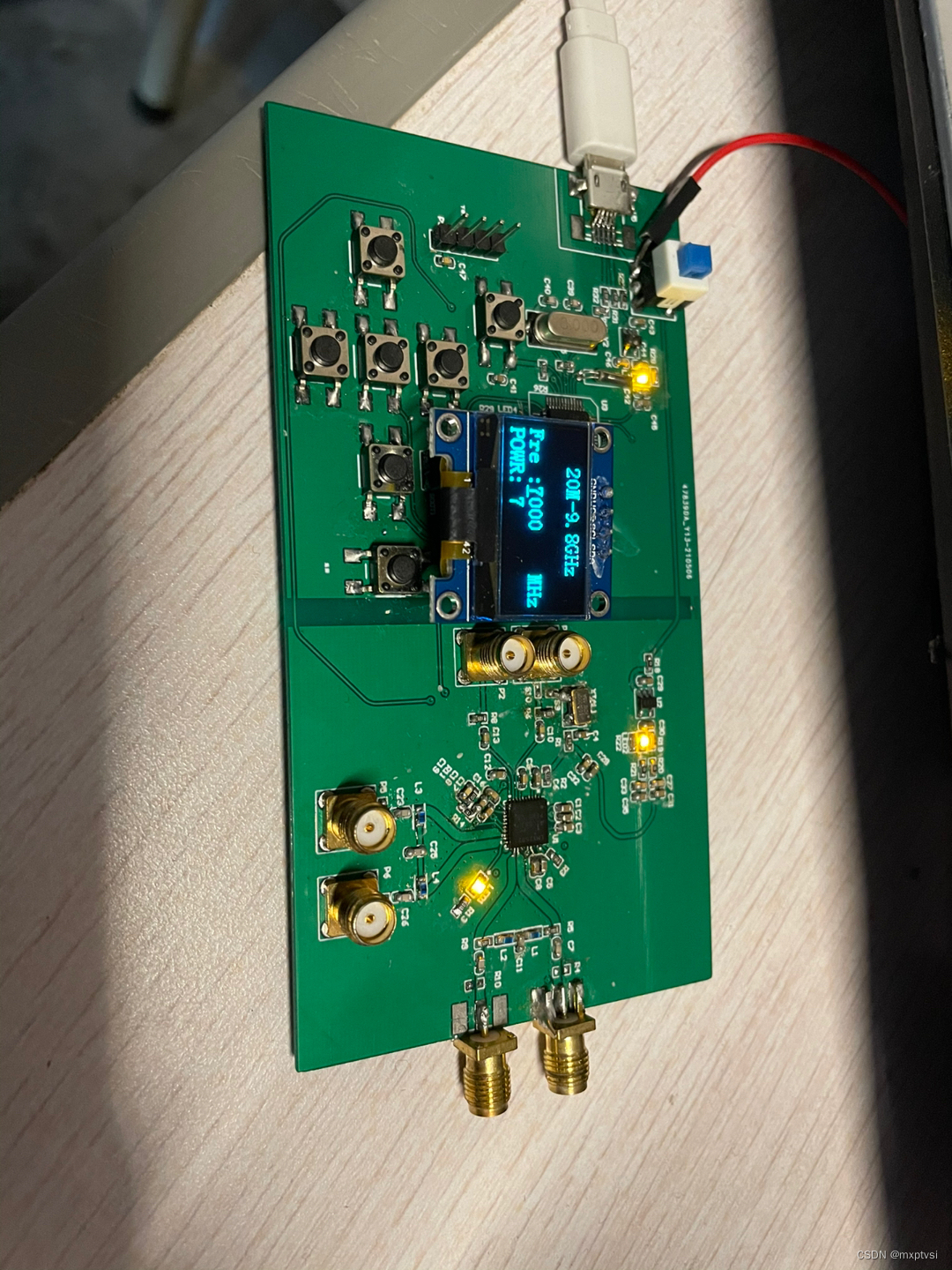

lmx2592频率源原理图和程序,20MHz——9.8GHz的低噪声锁相环频率

lmx2592频率源原理图和程序源码。 20MHz——9.8GHz的低噪声锁相环频率源,最小频率步进1MHz,输出功率可调,stm32f103c8t6控制lmx2592一体化,按键操控输出频率和输出功率,相位噪声非常不错。 USB供电 四端输出 可外接参考源 工作电流在360mA左右 这块板子是自己做的,可以作为比赛的频率源,混频器的本振。 提供电路图和源码 YID:511006581989

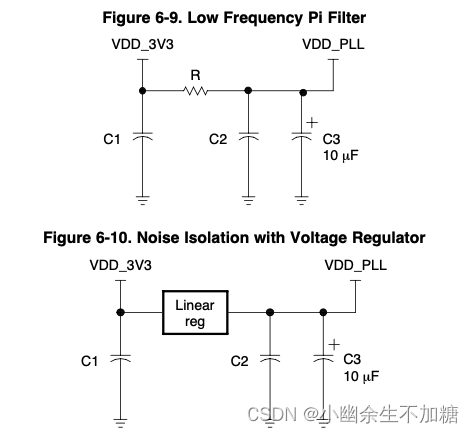

高速DSP系统设计参考指南(六)锁相环(PLL)

(六)锁相环(PLL) 1.模拟锁相环2.数字锁相环3.PLL隔离技术 系统设计人员需要隔离PLL,使其免受内部和外部噪声的影响。PLL通常用作频率合成器,将输入时钟乘以一个整数。该整数是反馈计数器M除以输入计数器N的比值,如所示Figure 6-1。 两种主要的PLL架构是模拟PLL (APLL)和数字PLL (DPLL)。了解这些差异有助于进行设计权衡,从而最大限度地降低电源和

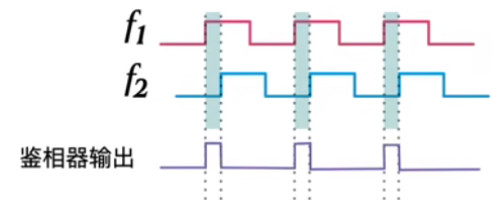

pll锁相环电路原理和参数

锁相环由PD,LPF,VCO组成 锁相环是由鉴相器,低通滤波器(环路滤波器),压控振荡器组成。 最简单的鉴相器电路情况下可以是一个异或门。这样只要有相位不同(0/1或1/0)则会产生电压,送给LPF进而调整VCO。 最简单的低通滤波器可以时一个RC电路,低频输出,高频从电容处通过而不输出。 PLL倍频分频是由DIV控制的 pll是锁相环,就是能锁定相位,使输出信号和输入信号相位相同

基于滑膜观测器锁相环(SMO-PLL)的无传感电机控制simulink仿真

基于滑膜观测器-锁相环的无传感电机控制仿真 仿真图搭建FOC对比SMO接入反馈后的对比总结补充 波形图都直接取自simulink-scope,均未做美化(doge)。 仿真图搭建 观前提示:原理部分请参考袁雷《现代永磁同步电机控制原理及MATLAB仿真》的公式推导。 整体结构: SMO-PLL: SMO: PLL: FOC对比 搭建完模型后先看看FOC

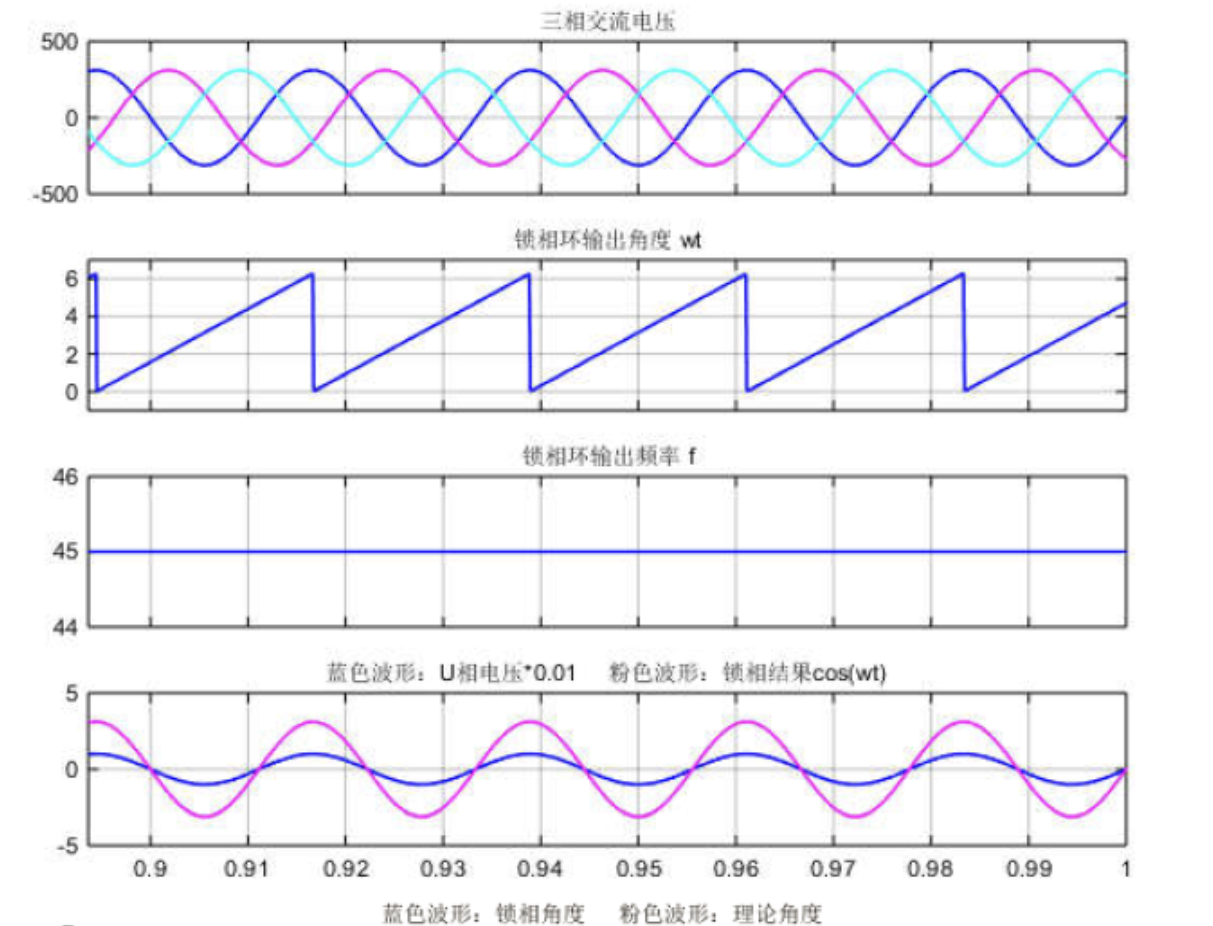

基于双二阶广义积分器的三相锁相环(DSOGI-PLL)Simulink仿真

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭:行百里者,半于九十。 📋📋📋本文目录如下:🎁🎁🎁 目录 💥1 概述 📚2 运行结果 2.1 完整模型 2.2 仿真参数设置 2.3 3AC380V 50Hz 锁相结果 2.4 三相电压不平衡锁相结果 2.5 三相电压含谐波畸变锁