本文主要是介绍一文搞懂晶振和锁相环,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

.晶振

晶振为单片机工作产生时钟频率,不同子系统需要不同频率时,用锁相环提供所需要的时钟频率。

1.晶体(crystal)与晶振(oscillator):

1.晶振=振荡器=有源晶振=oscillator 电路上一般简写为XO

晶体=谐振器=无源晶振=crystal 电路上一般简写为XTAL

2.晶体为无源的,一般两个管脚,需要起振电路(如MCU外接晶体+起振电容C1、C2)才可起振;

晶振为有源的4引脚,里面包含了晶体+起振电路,只需供电便可产生震荡信号。

3.晶体、晶振的区别就是在于有没有时钟电路;当用外部晶体时,MCU内部提供时钟电路,构成有源晶振;当用外部有源晶振时,直接将时钟输出引脚接到MCU。

2.内部时钟(就是时钟信号)与外部时钟

内:由于MCU内部有振荡电路,所以外部只用接一个晶振和两个电容即可!构成自激振荡器,发出的脉冲信号直接送入内部时钟电路。

外:将外部时钟产生电路产生的振荡脉冲接入XTAL1与XTAL2,即把时钟信号引入MCU内部。

3.外部晶体(external crystal)与外部时钟(external clock)

外部晶体:就是时钟信号产生电路在MCU内部,只是用了一个外部晶体;

外部时钟:时钟产生电路在外部。

4.外部晶振与内部晶振对比:

外:f精度高,受温度影响小,低功耗

内:f精度低,受温度影响大,成本低,在不涉及串口通信和精度要求不高时可以使用。

5.参数

标称频率(Normal Frequency)

晶振的标准频率,26MHz,32.768KHz等。

负载电容CL,

负载电容是指晶振正常工作震荡所需要的电容。为使晶体能够正常工作,需要在晶体两端外接电容,来匹配达到晶体的负载电容。

负载电容的值由如下公式计算:CL=C1*C2/(C1+C2)+CS,CL为晶振的负载电容值, CS为电路板的寄生电容,一般取3-5pf。取C1=C2,公式可简化成:CL=C1/2+CS。

一般情况下,增大负载电容值,会使震荡频率下降;减小负载电容值,会使振荡频率上升。

频率误差(Frequency Tolerance)或频率稳定度(Frequency Stability),用单位ppm来表示,即百万分之 一,是相对标称频率的变化量,此值越小表示精度越高

6.PCB注意

1. 两个匹配电容尽量靠近晶振摆放。

2. 晶振由石英晶体构成,容易受外力撞击或跌落的影响,所以在布局时,最好不要放在PCB边缘,尽量靠近 芯片摆放。

3.晶振的走线需要用GND保护好,并且远离敏感信号如RF、CLK信号以及高速信号。

2.锁相环

PLL(phase-locked loop),即锁相环。外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。是一种反馈控制电路。

锁相环PLL是由一个鉴相器(PD)、低通滤波器(LPF)和压控振荡器(VCO)组成。

通过鉴相器检测输出信号(反馈信号F0)和输入信号(参考信号)之间的相位差,并转化相位差成正比的电压信号,经过低通环路滤波器对电压信号进行滤波出来, 去除噪声和抖动,电压控制振荡器根据滤波后的电压信号调整输出信号的频率和相位, 使输出信号逐渐接近输入信号(基准信号)的相位,当输出信号与输入信号的相位达到同步时, 锁相环进入锁定状态, 系统维持稳定度相位同步。

鉴相器(PD)

鉴相器(PD)

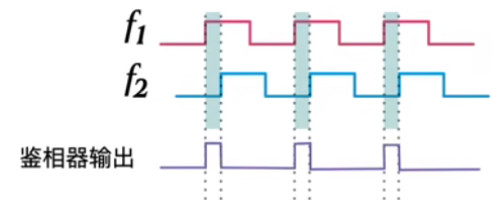

一个是晶振的输入信号,另外一个就是VCO的输出,鉴相器会把两个信号进行比较,如果这两个信号存在相位差异。比如 f2 滞后 f1 ,则鉴相器就会在存在差异的这一段进行输出。鉴相器不停的调制输出的电压,这样就会使得两个相位快速保持一致。fr>fo时,此时的相位比较器的输出PD会产生正脉波信号,使VCO的振荡器频率提高。相反地,如果fr<fo时,会产生负脉波信号。

低通滤波器(LPF)

由于鉴相器输出信号是矩形波,高低电平之间存在突变,因此这里就需要加一个滤波器,使得信号变得很平滑。滤除掉来自PLL电路中鉴相器输出电压Vd(t)中的高频成分和噪声分量

PD脉波信号经过滤波器(LoopFilter)的积分,便可以得到直流电压VR,可以控制VCO电路。

压控振荡器(VCO)Voltage Controlled Oscillator

由于控制电压VR的变化,VCO振荡频率会提高。结果使得fr=f0在f与f的相位成为一致时,PD端子会成为高阻抗状态,使PLL(锁相环)被锁栓(Lock)。

反馈分频器

那么PLL是如何实现倍频的呢?其实就是对输出fo作N分频,即fN,将分频后的频率送入鉴相器中与参考频率进行比较。当PLL进入锁定状态时,输出频率fo就实现了倍频,此时fo=N*fi。

这篇关于一文搞懂晶振和锁相环的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!