本文主要是介绍ADRV9009的供电要求和集成锁相环,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

ADRV9009的供电要求

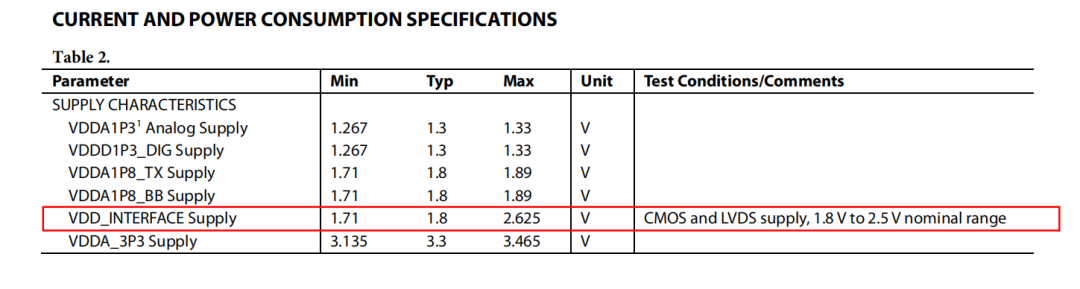

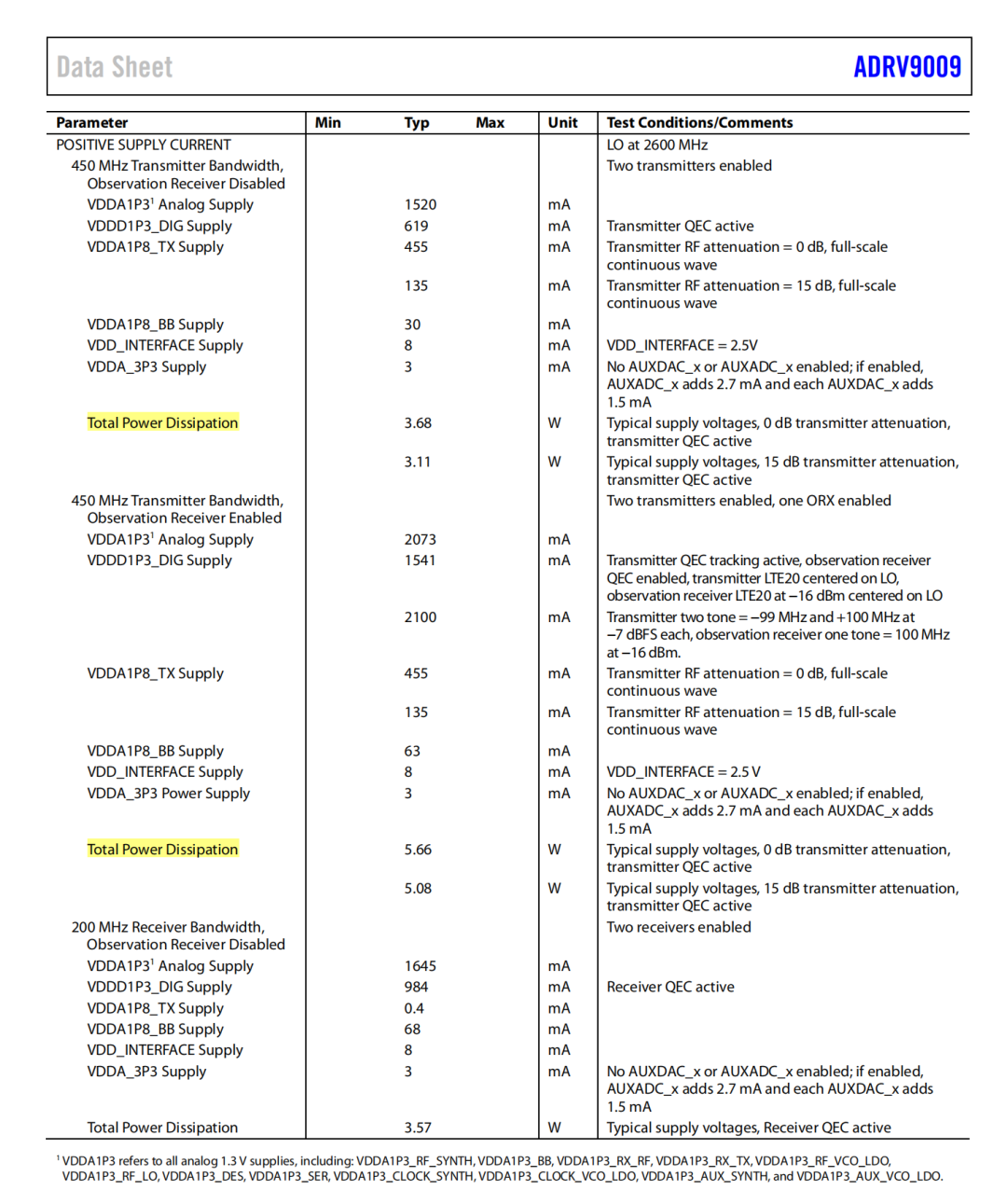

芯片有如下不同的用电端,各路供电载流要求( 模拟供电端需要使用低噪声LDO来提供低噪声电源):

(1) VDDA1P3 Analog 的供电网络载流要求为3A .

(2) VDDD1P3_DIG的供电网络载流要求3A .

(3) VDDA1P8_TX,VDDA1P8_BB的供电网络总载流要求为0.6A .

(4) VDD_INTERFACE 的供电网络载流要求为 20 mA。

(5) VDDA_3P3 的供电网络载流要求为 20 mA。

[注] VDDA1P3 供电网络指所有的1.3V模拟供电网络,包括:

-

VDDA1P3_BB,

VDDA1P3_RX_RF,

VDDA1P3_RX_TX,

VDDA1P3_RF_LO,

VDDA1P3_RF_SYNTH,

VDDA1P3_AUX_VCO_LDO,

VDDA1P3_RF_VCO_LDO,

VDDA1P3_CLOCK_VCO_LDO,

VDDA1P3_CLOCK_SYNTH,

VDDA1P3_AUX_SYNTH,

VDDA1P3_DES,

VDDA1P3_SER

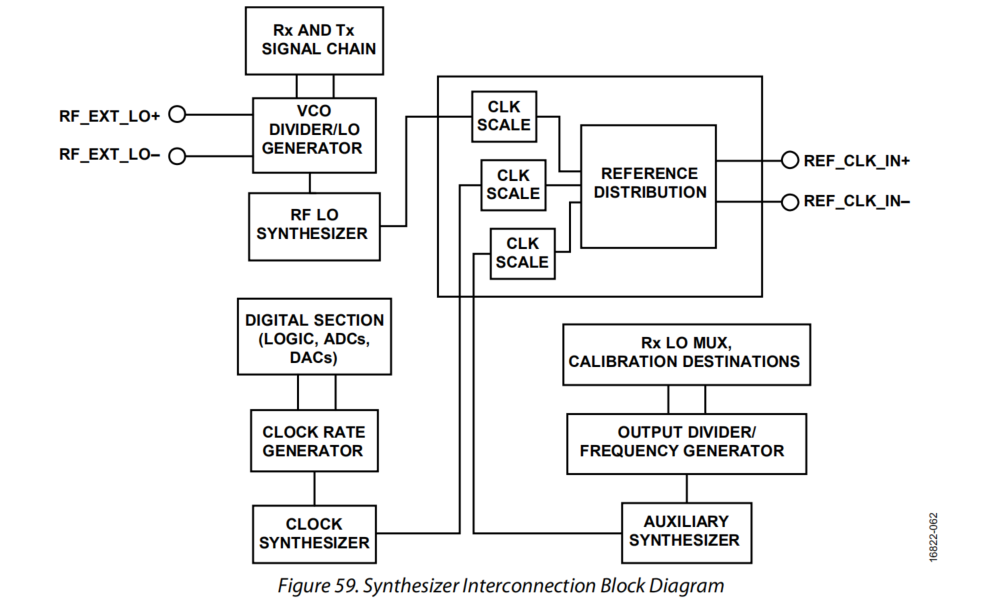

ADRV9009包含三个射频锁相环合成器:射频本振合成器、辅助合成器和时钟合成器。

下图说明了这些合成器及其在设备内的互连性。每个PLL合成器都采用分数N结构,带有完全集成的压控振荡器(VCO)和环路滤波器。无需外部元件即可覆盖设备的整个频率范围。

此配置允许使用任何方便的参考频率在任何采样率的任何信道上进行操作。每个锁相环的基频为6ghz到12ghz。本振频率是通过锁相环压控振荡器的频率分频产生的。

PLL的参考频率根据应用于芯片REF_CLK_IN±引脚的参考时钟进行缩放。

‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧ END ‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧

长按识别图中二维码关注

欢迎关注微信公众号【数字积木】,更精彩的内容等着你!

这篇关于ADRV9009的供电要求和集成锁相环的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!