逻辑设计专题

数据库系统之逻辑设计

数据库的逻辑设计是将概念设计阶段产生的实体关系图(ER图)转化为具体的数据库表结构的过程。这一阶段的目标是创建一个高效、易于管理和扩展的数据库模式。下面我将通过一个简单的例子来详细介绍数据库逻辑设计的过程。 ### 示例:图书管理系统 假设我们需要为一家小型图书馆设计一个图书管理系统。该系统需要记录书籍的基本信息、借阅情况以及读者的信息。 #### 步骤 1: 概念设计回顾 首先,回顾一下

【芯片设计- RTL 数字逻辑设计入门 9.4 -- Power Gating 在SoC 芯片电源完整性中的详细介绍】

文章目录 电源完整性简介电源完整性重要性电源完整性主要问题 电源完整性问题优化 什么是Power Gating?Power Gating的优势与挑战浪涌电流的产生与影响设计中的折中与优化 电源完整性简介 电源完整性(Power Integrity, PI)是指在系统级设计中,确保电源分配网络(Power Distribution Network, PDN)中的电压和电流保持稳

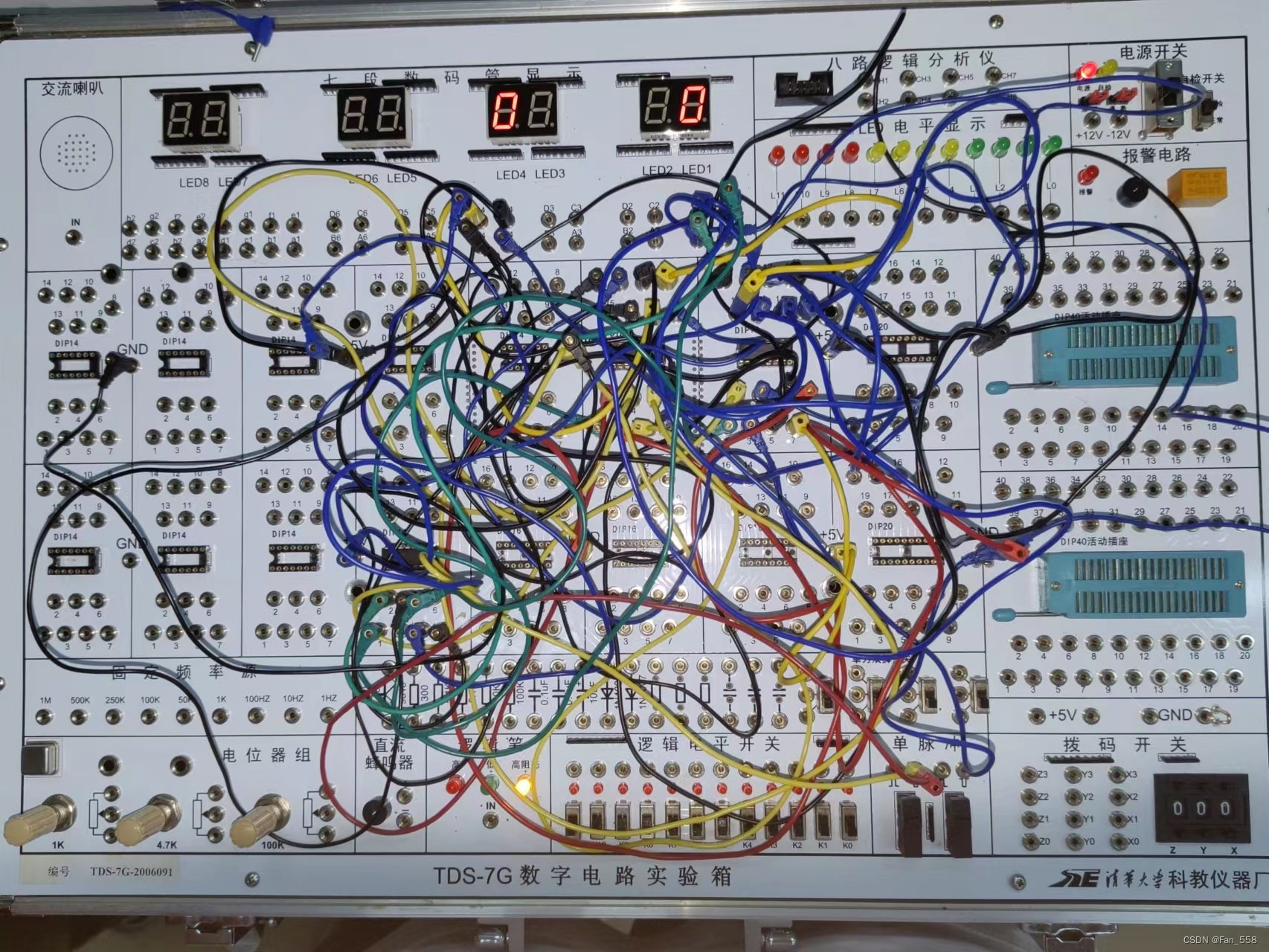

数字电路与逻辑设计实验-MSI译码器逻辑功能测试

一.实验目的 1.掌握中规模(MSI)集成译码器的逻辑功能和使用方法; 2.验证3—8线译码器和七段显示译码器的逻辑功能; 3.掌握数码管与译码器配合使用的方法。 二.实验原理 译码器的作用是进行代码间的“翻译”,将具有特定含义的二进制码进行辨别,并转换成控制信号。 译码器分通用译码器和显示译码器两大类。前者又分为变量译码器和代码变换译码器。 l.变量译码器(又称二进制译码器)

5.5 业务流程和业务逻辑设计

一、引言 1.1 项目背景 经过上述的论述,我们讨论一下业务流程和业务逻辑设计,通过合理的业务流程设计和业务逻辑设计,可以提高用户的购物体验,降低用户的操作成本,并确保用户的购物行为符合平台的规则和要求。同时,良好的业务流程和业务逻辑设计也能提高平台的运营效率,减少错误和纠纷的发生。因此,业务流程和业务逻辑设计在该项目中具有重要的意义。 1.2 目的和范围 业务流程设计的目的是为了确保

【C++风云录】数字逻辑设计优化:电子设计自动化与集成电路

集成电路设计:打开知识的大门 前言 本文将详细介绍关于数字芯片设计,电子设计格式解析,集成电路设计工具,硬件描述语言分析,电路验证以及电路优化六个主题的深入研究与实践。每一部分都包含了主题的概述,功能特性,实现原理以及使用示例。 欢迎订阅专栏:C++风云录 文章目录 集成电路设计:打开知识的大门前言1. OpenROAD1.1 介绍1.2 功能特性1.2.1 自动设计流程1.

明德扬逻辑设计基本功修炼课考试体会_我的FPGA成长篇

本文为明德扬原创文章,转载请注明出处!作者:明德扬学员:考试酷账号:11167760 大家好,我是基本功修炼班的学员。从2023年8月开始,我参加了考试酷,并且已经获得了全套项目课程奖励,其中包括(代码提升/调试技巧/DDR3/温度检测/图像处理/千兆以太网/FIFO架构/时序约束/JESD204B/光纤项目)当时,还有一周获取了一套下载器奖励。今天,我很荣幸地接受小易老师的邀请,来分享一下我参

2.1 开发概述和FPGA逻辑设计

\qquad 在HD-GR接收机中,微处理器是软核类型的(NIOS II),在一片Altera FPGA (U1)中分配。NIOS II软核及其软件与基带硬件逻辑一道共享这片FPGA资源。因此,HD-GR接收机中的很大一部分可以在一个公共平台上进行创建和编程。Altera为FPGA硬件逻辑设计和NIOS II软件编程这两个紧密联系的领域提供了一个基于PC的开发环境: Altera Quartu

逻辑设计问题 -- 构建一个组件

文章目录 构建一个组件抽象和组件组件的接口设计封装程度辅助实现类小结 构建一个组件 抽象和组件 抽象是完成一个共同目的的一组对象和相关行为的抽象规范 一个类是一个ADT(抽象数据类型)的具体规范,一个组件是一个抽象的具体规范 组件的接口设计 设计良好的组件接口在质量上包括几个方面。最低要求是,接口必须足以使预期的客户能有效利用设计该组件来支持的抽象。考虑一个

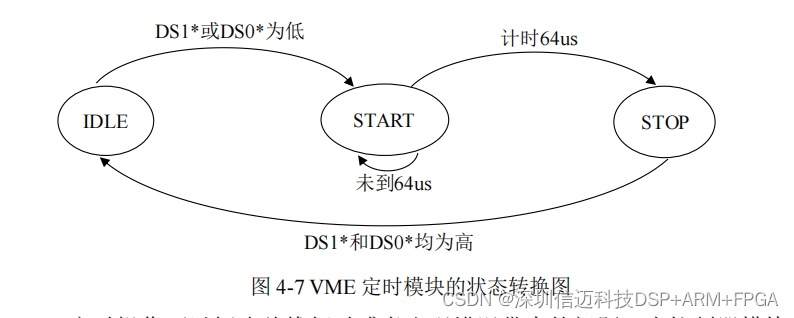

基于 RK3399+fpga 的 VME 总线控制器设计(二)硬件和FPGA逻辑设计

3.2 FPGA 最小系统设计 FPGA 最小系统是指可以使 FPGA 正常工作的最基本的系统,主要包括电源电 路、配置电路、时钟和复位电路。本次设计使用的 FPGA 为紫光同创的 PG2L100H, 接下来具体介绍 FPGA 最小系统各个部分的电路设计。 ( 1 )电源电路设计 FPGA 所需要的电源电压有 3.3V 、

【芯片设计- RTL 数字逻辑设计入门 4 -- verilog 组合逻辑和时序逻辑】

文章目录 组合逻辑时序逻辑可综合设计模块结构缩写命令 组合逻辑 这种条件信号变化结果立即变化的 always 语句被称为“组合逻辑” 。 always @(posedge clk)beginif(sel==0)c <= a + b;elsec <= a + d;end 时序逻辑 这种信号边沿触发, 即信号上升沿或者下降沿才变化的 always, 被称为“时序逻辑” ,

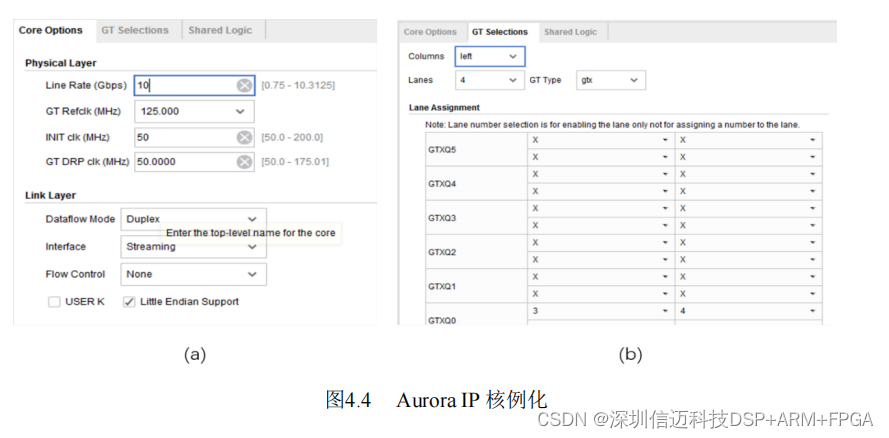

基于ZYNQ的PCIE高速数据采集卡的设计(四)软件设计,Aurora 协议逻辑设计

系统软件设计 4.1 引言 本章基于第二章的分析结论,进行系统软件设计。软件设计包括逻辑设计、嵌入 式软件设计和上位机软件设计。在逻辑设计中,对 ADC 模块、 Aurora 模块、 DDR3 SDRAM 模块和 PCIE 模块进行分析和设计,在 Vivado 软件提供的 IP 核的基础上进 行各模块的逻辑代码的编写,并解决

【芯片设计- RTL 数字逻辑设计入门 14 -- 使用子模块实现三输入数的大小比较】

文章目录 三输入数的大小比较问题分析verilog codeTestBench Code综合图仿真波形图 三输入数的大小比较 在数字芯片设计中,通常把完成特定功能且相对独立的代码编写成子模块,在需要的时候再在主模块中例化使用,以提高代码的可复用性和设计的层次性,方便后续的修改。 请编写一个子模块,将输入两个8bit位宽的变量data_a,data_b,并输出data_a,

【芯片设计- RTL 数字逻辑设计入门 番外篇 9 -- SOC 中PL端与PS端详细介绍】

文章目录 Programmable Logic and Processing SystemPL(Programmable Logic)特点PS和PL之间的协同设计和开发工具 Programmable Logic and Processing System 在系统级芯片(SoC)的上下文中,“PL” 通常指的是可编程逻辑(Programmable Logic)部分,特别是在

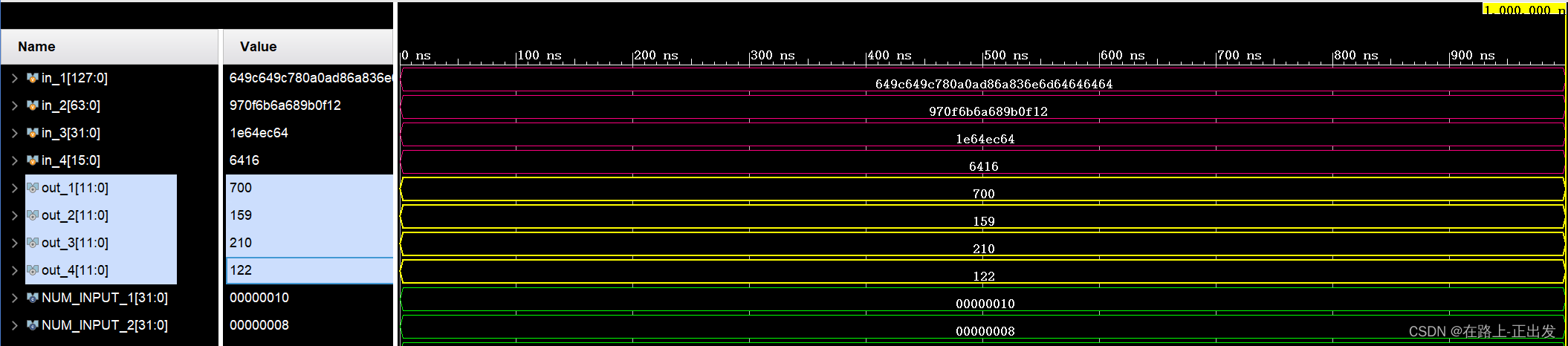

【芯片设计- RTL 数字逻辑设计入门 11 -- 移位运算与乘法】

请阅读【嵌入式开发学习必备专栏 】 文章目录 移位运算与乘法Verilog CodeTestbench CodeVCS 波形仿真 问题小结 移位运算与乘法 已知d为一个8位数,请在每个时钟周期分别输出该数乘1/3/7/8,并输出一个信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效) 可以看到输入D 的波形在为6的地方比较特殊,从波形上可以看到它只持续了一个

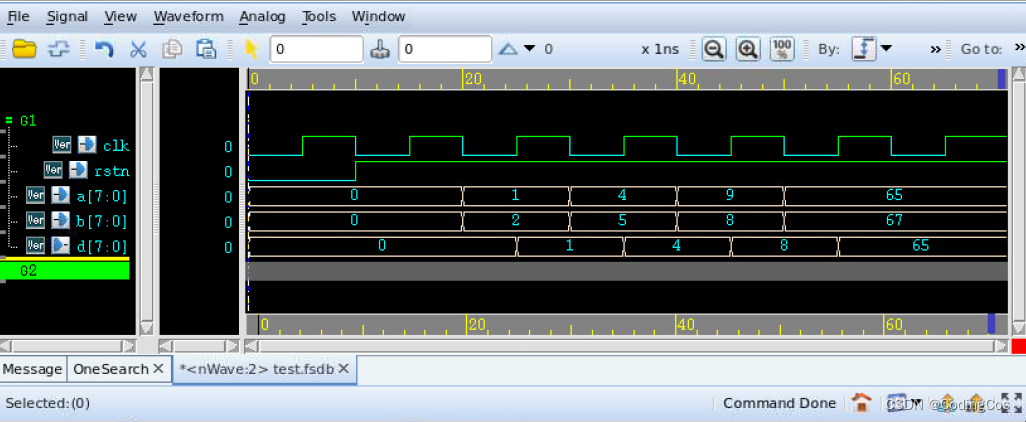

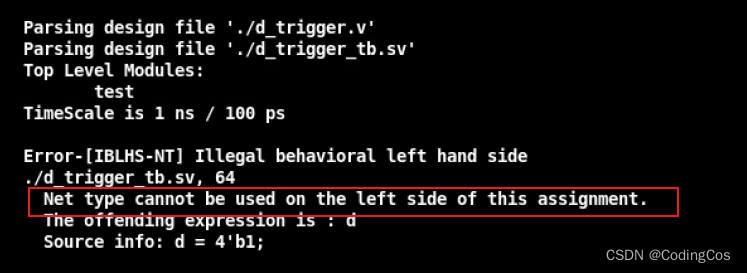

【芯片设计- RTL 数字逻辑设计入门 6 -- 带同步复位的D触发器 RTL实现及testbench 验证】

文章目录 带同步复位的D触发器Verilog 代码testbench 代码编译及仿真问题小结 带同步复位的D触发器 同步复位 :复位只能发生在在clk信号的上升沿,若clk信号出现问题,则无法进行复位。 Verilog 代码 // timescale ins/1nsmodule flopr (input rstn,input clk,input[3:0] d,

海康威视 2024届 数字逻辑设计 实习笔试分析

说明 记录一下 5月11日晚,做的海康威视的一场笔试。分享给需要的IC人。 岗位:数字逻辑设计工程师(浙江 杭州) 转载需要本人同意! 我的见解不一定都是准确的,欢迎评论区交流指正~~ 单选题 1、(3分)在Verilog中,下列语句哪个不是分支语句? A、case B、if-else C、casez D、repeat 一眼见,D 2、(3分)对于 r

Redis异步写失败后补数逻辑设计

背景 最近各种机房事故频发,所以很多公司都对Redis存储等进行异步多活,我们公司采用的方式是通过客户端双写的方式来实现异地Redis机房的备份,但是当异地机房出现临时网络故障时,就涉及到了如何进行补数的操作,本文就是来记录下如何补数 Redis补数设计 首先可以补数的前提肯定需要记录写异地机房失败的redis命令,所以当客户端在写异地机房失败时,我们需要先把失败的redis命令写到kafk

《微服务架构设计模式》读书笔记 | 第5章 微服务架构中的业务逻辑设计

第5章 微服务架构中的业务逻辑设计 前言1. 业务逻辑组织模式1.1 一个典型的服务架构1.2 使用事务脚本模式设计业务逻辑1.3 使用领域模型模式设计业务逻辑1.4 关于领域驱动设计 2. 使用聚合模式设计领域模型2.1 聚合拥有明确的边界2.2 聚合规则2.3 聚合的颗粒度2.4 使用聚合设计业务2.5 Order Service基于聚合设计的业务逻辑 3. 发布领域事件3.1 领域事件

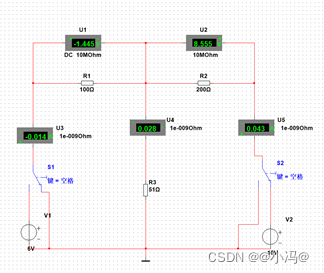

数字电路与逻辑设计实验:叠加定理

叠加定理 一、实验目的二、实验内容及步骤三、实验结果与分析四、讨论,心得 一、实验目的 1、 熟悉仿真软件Multisim 2011的基本用法; 2、 通过实验加深理解和验证电路叠加定理;; 3、 学会直流电压和直流电流的测量方法; 4、 学会分析计算误差的方法。 二、实验内容及步骤 1、 放置电路元件及测量仪器 2、根据图1.1中给定参数计算理论值,填入表1.1中。 3、

【数字电路与逻辑设计实验】——Multisim仿真实验-xx进制的计数器

前言 题目:关于xx进制的计数器(74LS161 / 74LS160设计实现学号尾号后两位+20后对应值的计数器) 本文不会详细的教你如何仿真实现计数器,更多的是分享如何完成这个实验的资源 关于视频讲解点这里,视频是由一位b站上的老师讲解的,很是详细,会从原理到仿真实验手把手教你 Multisim下载 软件 解压密码 admincxz,里面有保姆级教程跟着一步步下载就可以了

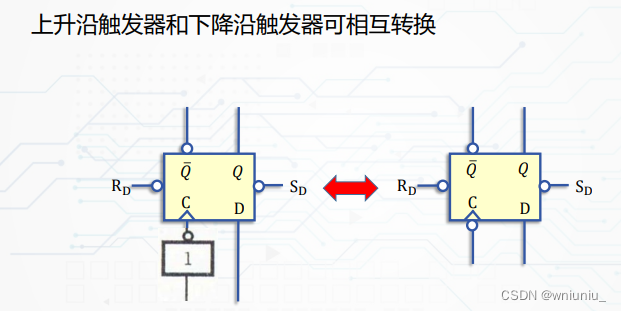

数字电路与逻辑设计 触发器

与非门构成的RS触发器 在这个中禁止RS = 00 要记住s对应Q 或非门构成的RS触发器 注意这里的RS换了位置 且不允许RS = 11 同步触发器 钟控RS触发器 钟控D触发器 cp 为 0 的时候不变 钟控JK触发器 00不变11改,JK不同随J摆 钟控T触发器 什么是空翻? 主从RS触

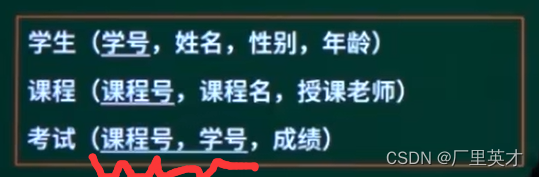

软件设计师学习笔记12-数据库的基本概念+数据库的设计过程+概念设计+逻辑设计

1.数据库的基本概念 1.1数据库的体系结构 1.1.1常见数据库 ①集中式数据库 数据是集中的;数据管理是集中的 ②C/S结构 客户端负责数据表服务;服务器负责数据库服务;系统分前后端;ODBC、JDBC ③分布式数据库 物理上分布、逻辑上集中;物理上分布、逻辑上分布;透明性 ④并行数据库 分为共享内存式和无共享式 1.1.2分布式数据库的特点 ①数据独立性。除了数据的逻

C++逻辑设计——函数设计之函数接口说明

在C++中指定函数接口时,一些必须要解决的问题有: (1) 运算符函数还是非运算符函数? (2) 自由运算符还是成员运算符? (3) 虚函数还是非虚函数? (4) 纯虚成员函数还是非纯虚成员函数? (5) 静态成员函数还是非静态成员函数? (6) 常量成员函数还是非常量成员函数? (7) public、protected 还是 private 成员函数? (8) 通过值、引用还是指