本文主要是介绍【芯片设计- RTL 数字逻辑设计入门 14 -- 使用子模块实现三输入数的大小比较】,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 三输入数的大小比较

- 问题分析

- verilog code

- TestBench Code

- 综合图

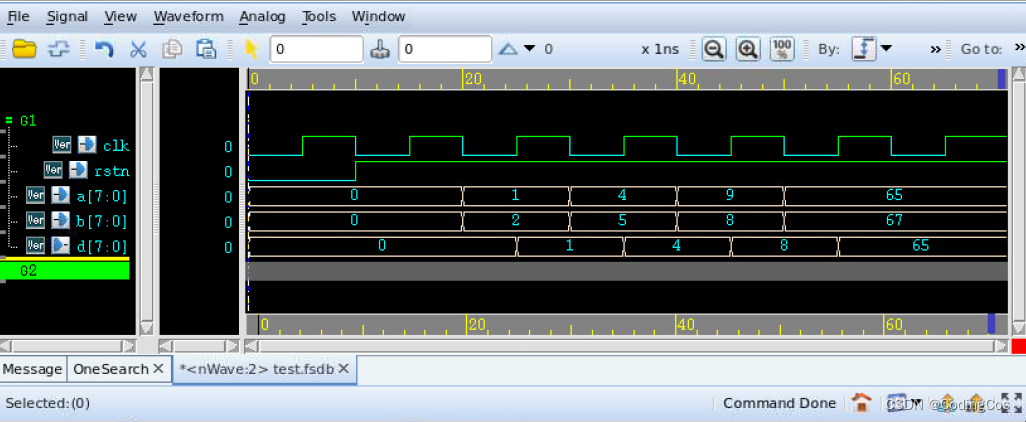

- 仿真波形图

三输入数的大小比较

在数字芯片设计中,通常把完成特定功能且相对独立的代码编写成子模块,在需要的时候再在主模块中例化使用,以提高代码的可复用性和设计的层次性,方便后续的修改。

请编写一个子模块,将输入两个8bit位宽的变量data_a,data_b,并输出data_a,data_b之中较小的数。并在主模块中例化,实现输出三个8bit输入信号的最小值的功能。

子模块的信号接口图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

- clk:系统时钟

- rst_n:异步复位信号,低电平有效

- a,b,c:8bit位宽的无符号数

输出描述:

- d:8bit位宽的无符号数,表示a,b,c中的最小值

问题分析

需要调用3个模块:

- 第一个模块:比较 T 时刻的 a 和 b,T+1 时刻出来 tmp1;

- 第二个模块:比较 T 时刻的 a 和 c,T+1 时刻出来 tmp2;

- 第三个模块:比较 T+1 时刻的 tmp1 和 tmp2,T+2 时刻出来 d;

如果只用2个子模块,那么 T 时刻比较 a 和 b 得到 tmp1,再比较 tmp1 和 c 的时候是 T+1 时刻的 c 和 T+1 时刻的 tmp1,而 tmp1 代表的是 T 时刻 a 和 b 的较小值,所以这时候比较的 T 时刻的 a、b 和 T+1 时刻的 c,显然不符合要求。

所以不能只例化两次子模块,因为主模块例化的子模块在综合时是复制一样的电路,在执行时是并行执行的。如果只例化两次,第二次例化的值并不是第一个子模块输出的最小值

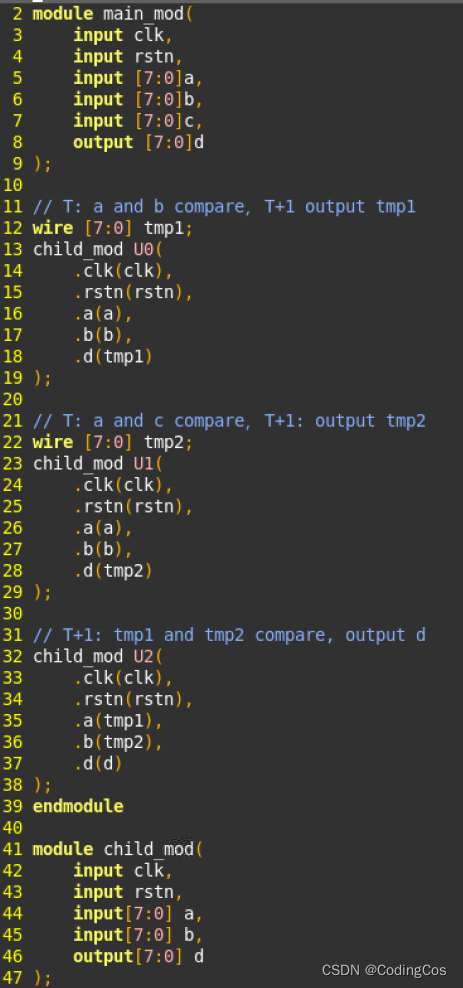

verilog code

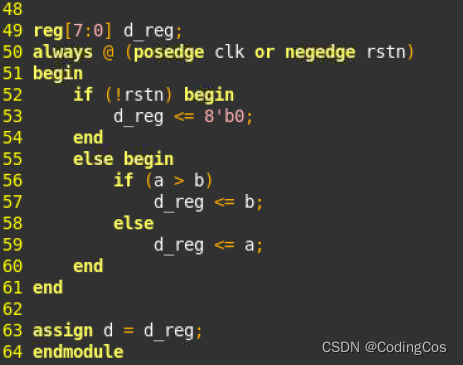

TestBench Code

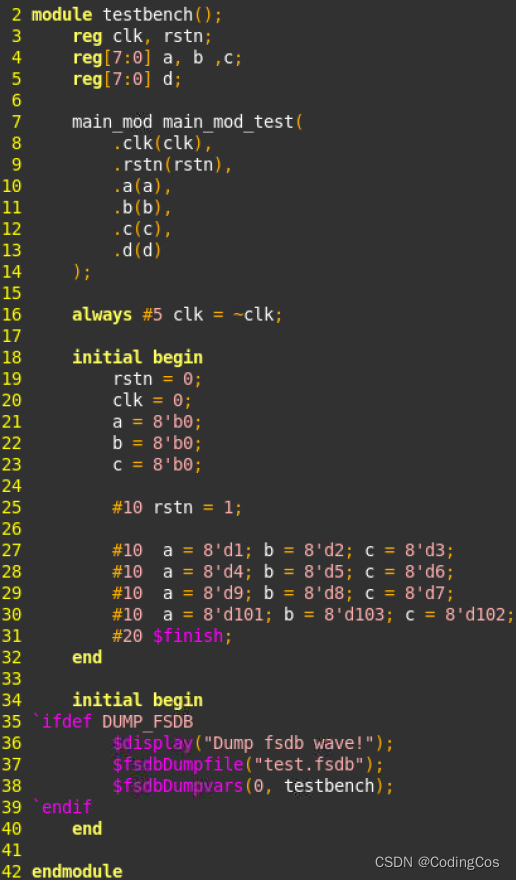

综合图

仿真波形图

这篇关于【芯片设计- RTL 数字逻辑设计入门 14 -- 使用子模块实现三输入数的大小比较】的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!