rtl专题

HLS报错之:Export RTL报错 “ERROR: [IMPL 213-28] Failed to generate IP.“

原因:官方bug 解决办法:下载补丁(补丁适用于2014年至2021年的多个Vivado版本),并添加到对应路径下即可。 注意:windows下该方法试用。 补丁连接 我这里下载到xilinx的目录下并解压: 点进去找到该文件: 复制到scripts路径下即可 现在export RTL就正常了

RTL-SDR SpectrumPy频谱显示

GITHUB大佬开源的基于RTL-SDR的python频谱显示程序链接,下载下来后,安装必要的库,编译运行,运行报错。 修改了以下两个地方: 修改点1: 修改前: self.spinBoxFrequency.setValue(self.center_freq) 修改后: self.spinBoxFrequency.setValue(int(self.center_freq)) 修改点2

【芯片设计- RTL 数字逻辑设计入门 9.4 -- Power Gating 在SoC 芯片电源完整性中的详细介绍】

文章目录 电源完整性简介电源完整性重要性电源完整性主要问题 电源完整性问题优化 什么是Power Gating?Power Gating的优势与挑战浪涌电流的产生与影响设计中的折中与优化 电源完整性简介 电源完整性(Power Integrity, PI)是指在系统级设计中,确保电源分配网络(Power Distribution Network, PDN)中的电压和电流保持稳

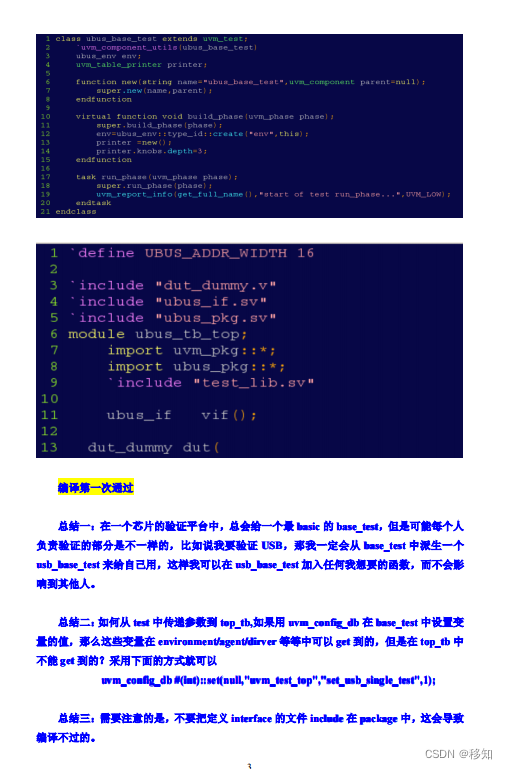

利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

在集成电路设计的复杂世界中,验证环节是确保设计满足预期功能和性能要求的关键步骤。随着系统级芯片(SOC)和特定应用集成电路(ASIC)的规模和复杂性不断增加,传统的验证方法已经难以满足高效、准确的验证需求。因此,采用先进的验证方法学和工具变得尤为重要。 SystemVerilog(SV)和通用验证方法学(UVM)作为当前硬件验证领域的两大支柱,提供了一套完整的框架和工具,用于构建可扩展、可重用的

Verilog-Behavior Level 和 RTL Level 和 GATE Level的区别

硬件设计中对硬件的描述可以具有不同的抽象级别,以Verilog为例: Behavior Level。描述的是硬件的行为,当我们在看到如下关键字时就是行为级别的代码:#,wait,while,force,release等,行为级别的代码通常比较直观,但可能不可综合。RTL Level。RTL即Register Transfer Level寄存器传输级别,使用always和assign语句块组成的代

Vitis HLS 学习笔记--添加 RTL 黑盒函数

目录 1. 简介 2. 用法详解 2.1 需要的文件 2.1.1 RTL 函数签名 2.1.2 黑盒 JSON 描述文件 2.1.3 RTL IP 文件 2.2 操作步骤 3. 总结 1. 简介 Vitis HLS 工具可以将现有的 Verilog RTL IP(即硬件描述语言编写的模块)集成到 C/C++ HLS 项目中。通过这种方式,Vitis HLS 能够将 RT

Android RelativeLayout Rtl布局下的bug:paddingStart会同时作用于左右内边距

问题现象 如上图,只是设置了paddingStart,在RTL布局下,左右都产生了10dp的间距。其他布局如LinearLayout,FrameLayout则没有这个问题。 private void positionAtEdge(View child, LayoutParams params, int myWidth) {if (isLayoutRtl()) {// myWidth是

Yosys-RTL开源综合工具

参考: http://www.clifford.at/yosys/ http://www.clifford.at/yosys/files/yosys-austrochip2013.pdf https://chips4makers.io/blog/open-source-mixed-rtl-synthesis.html http://www.clifford.at/yosys/files

RTL Layout由来

一。RTL Layout由来平常我们了解的布局习惯都是:从左到右,从上到下。但在很多国家的习惯是:从右到左,从上到下。诸如阿拉伯语、希伯来语等国家就是这种习惯。那对于从右到左的习惯,Android中怎么使用LinearLayout,不好用吧,难道只能用RelativeLayout来实现。这当然不适合Android的初衷和发展。所以,从Android 4.2开始,Android SDK支持一种从右到

HLS相比RTL的优劣

HLS: xilinx公司推出的Vitis HLS开发, HLS工具是将HLS代码翻译成RTL,然后由Vivado编译生成bitstream RTL: xilinx公司推出的Vivado开发 优势 开发周期短,非常适合前期功能、性能的验证,可以极大的节省时间成本和人力成本;新手入门门槛低,HLS代码由C++和pragma组成,相比Verilog和VHDL对软件工程师更友好(当然具有硬件思维的工

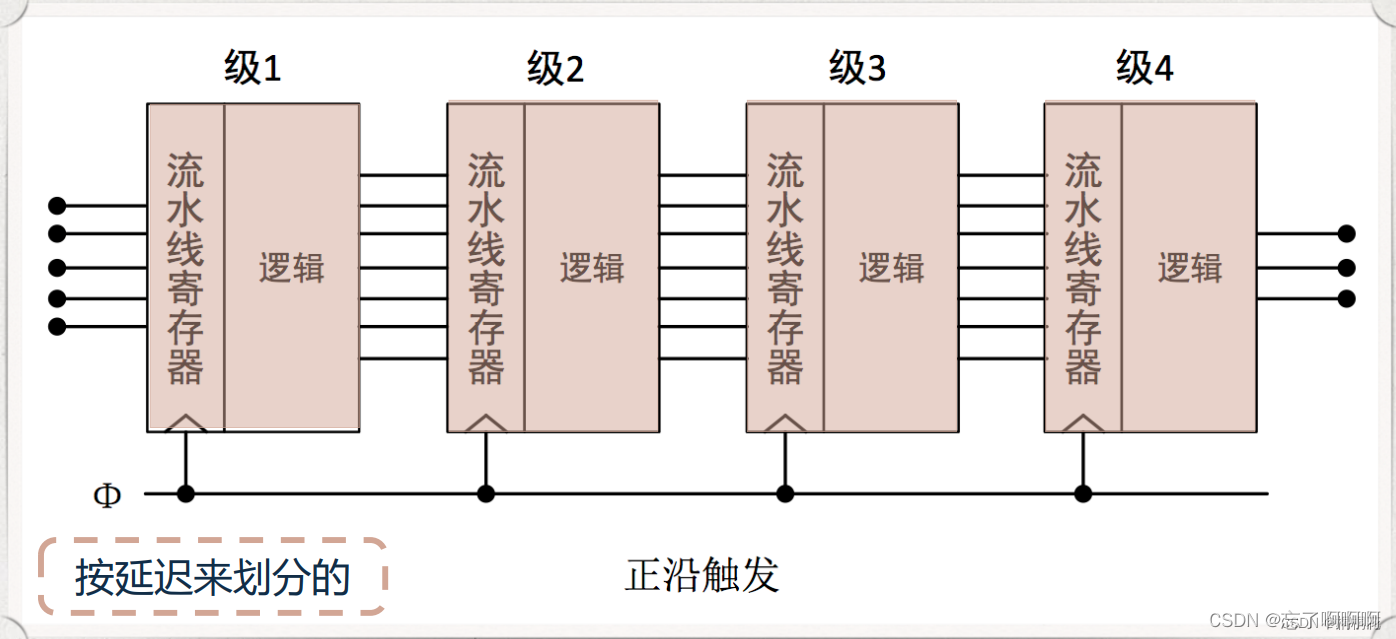

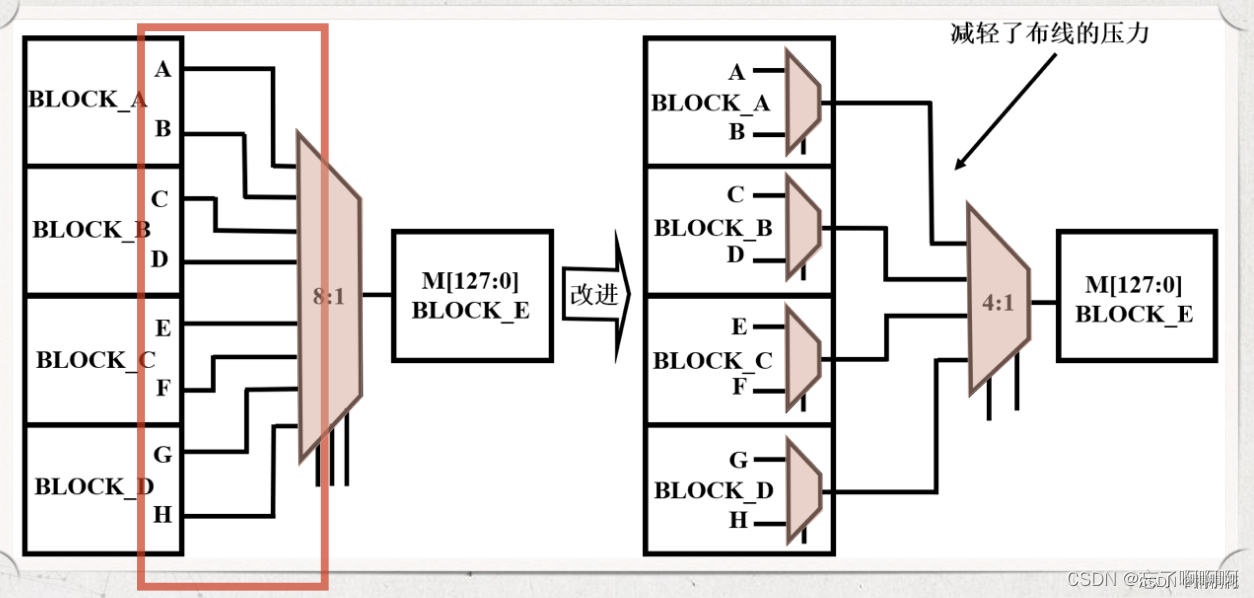

RTL书写与延迟、面积、功耗、布线

RTL书写与延迟、面积、功耗、布线 延迟 设计方法 将延迟较大的信号放在最后一个选择器上,从而隐藏其较大的延迟。对电路的修改不应该影响其原有的逻辑。 if语句输入信号延迟 提取输出提取条件 //修改前module mult_if(input a,b,c,d,input [3:0] sel,output reg z);always@(*)beginz = 1'b0;if(

RISC-V处理器:1.取指令 RTL 代码分析

RISC-V处理器:1.取指令 RTL 代码分析 1. 取指特点 指令在存储空间中所处的地址,称为它的指令PC(Program Counter)取指是指处理器将指令,按照其指令PC,从存储器中读取出来的过程处理器从存储器中取出指令的目标是:快速和连续不断指令分为普通指令,非分支跳转指令和分支跳转指令对于非分支跳转指令,即便是对于地址不对齐的32位指令,也要求能够连续不断的从一个周期内读取出来对

verdi加载vhdl和verilog混合RTL设计的方法

采用三步法完成混合语言RTL设计的加载。 step1. 用vhdlcom将所有的VHDL RTL代码编译成库 1.1 将所有的vhdl文件放到vhdl.f文件中,如: vhdl.f --------- my_design.vhd my_lib.vhd tb_my_design.vhd 1.2 编译成库

【芯片设计- RTL 数字逻辑设计入门 4 -- verilog 组合逻辑和时序逻辑】

文章目录 组合逻辑时序逻辑可综合设计模块结构缩写命令 组合逻辑 这种条件信号变化结果立即变化的 always 语句被称为“组合逻辑” 。 always @(posedge clk)beginif(sel==0)c <= a + b;elsec <= a + d;end 时序逻辑 这种信号边沿触发, 即信号上升沿或者下降沿才变化的 always, 被称为“时序逻辑” ,

ios app 阿拉伯语 RTL 的NSWritingDirectionAttributeName

//NSWritingDirectionAttributeName 设置文字书写方向,取值为以下组合 // iOS9.0以前 //@[@(NSWritingDirectionLeftToRight | NSTextWritingDirectionEmbedding)] //@[@(NSWritingDirectionLeftToRight | NSTextWritingDirectionO

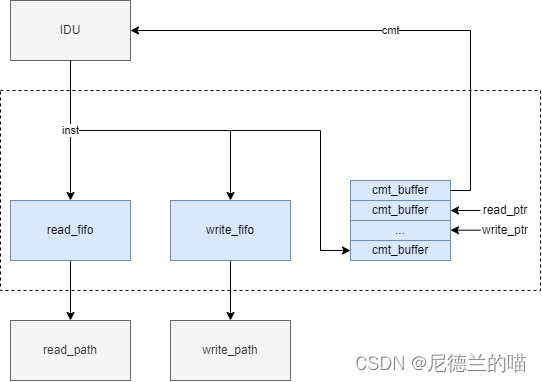

【IC前端虚拟项目】inst_buffer子模块DS与RTL编码

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 需要说明一下的是,在我所提供的文档体系里,并没有模块的DS文档哈,因为实际项目里我也不怎么写DS毕竟不是每个公司都和HISI一样对文档要求这么严格的。不过作为一个培训的虚拟项目,还是建议在时间充裕的情况下动手写一写模块的DS,毕竟是有助于代码开发的。 inst_buffer模块是专门用来处理指令接收和指令提交的,

【OnlyOffice】 桌面应用编辑器,版本8.0已发布,PDF表单、RTL支持、Moodle集成、本地界面主题

ONLYOFFICE桌面编辑器v8.0是一款功能强大、易于使用的办公软件,适用于个人用户、企业团队和教育机构,帮助他们高效地处理文档工作并实现协作。无论是在Windows、macOS还是Linux平台上,ONLYOFFICE都能提供无缝的编辑和共享体验。 目录 ONLYOFFICE软件介绍下载地址高兼容云服务丰富模板 PDF编辑双向文本单变量求解图表向导 ONLYOFFI

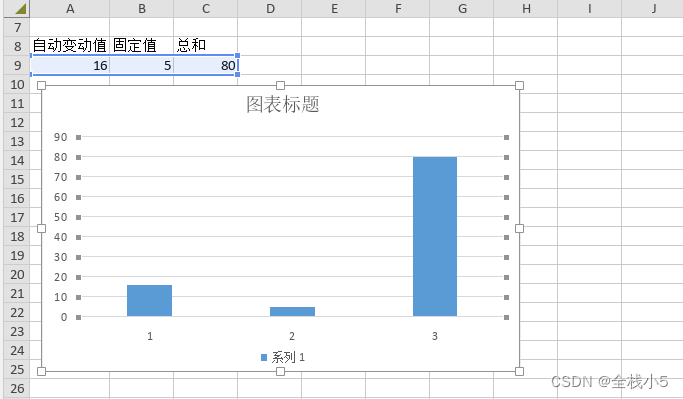

ONLYOFFICE 桌面应用程序 v8.0 发布:全新 RTL 界面、本地主题、Moodle 集成等你期待的功能来了!

目录 📘 前言 📟 一、什么是 ONLYOFFICE 桌面编辑器? 📟 二、ONLYOFFICE 8.0版本新增了那些特别的实用模块? 2.1. 可填写的 PDF 表单 2.2. 双向文本 2.3. 电子表格中的新增功能 单变量求解: 图表向导: 编辑 序列: 2.4. 与 Moodle 集成 2.5. 用密码保护 PDF 文件 2.6. 从

【芯片设计- RTL 数字逻辑设计入门 14 -- 使用子模块实现三输入数的大小比较】

文章目录 三输入数的大小比较问题分析verilog codeTestBench Code综合图仿真波形图 三输入数的大小比较 在数字芯片设计中,通常把完成特定功能且相对独立的代码编写成子模块,在需要的时候再在主模块中例化使用,以提高代码的可复用性和设计的层次性,方便后续的修改。 请编写一个子模块,将输入两个8bit位宽的变量data_a,data_b,并输出data_a,

【芯片设计- RTL 数字逻辑设计入门 番外篇 9 -- SOC 中PL端与PS端详细介绍】

文章目录 Programmable Logic and Processing SystemPL(Programmable Logic)特点PS和PL之间的协同设计和开发工具 Programmable Logic and Processing System 在系统级芯片(SoC)的上下文中,“PL” 通常指的是可编程逻辑(Programmable Logic)部分,特别是在

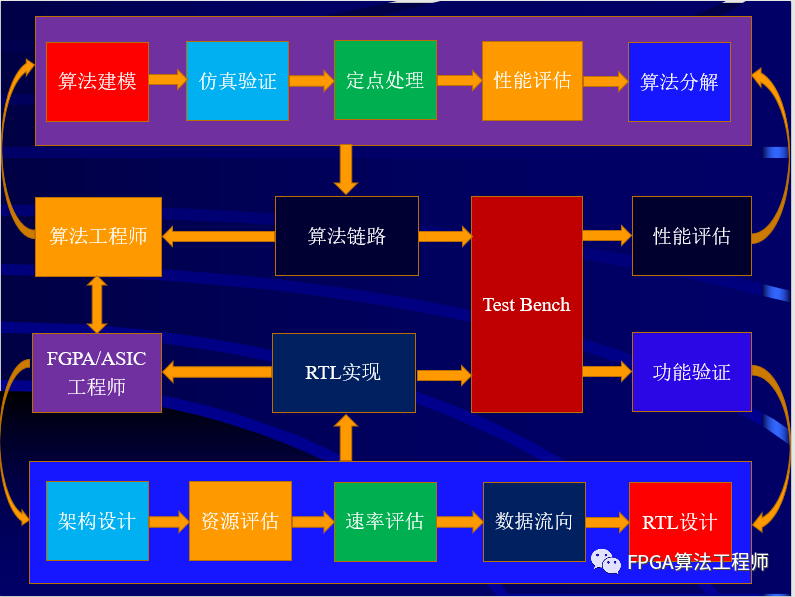

从算法到RTL实现,FPGA工程师该怎么做?

针对近日技术交流群里讨论的算法与RTL实现问题,写篇文章,做一次总结。 微信公众号《FPGA算法工程师》技术交流群里,交流气氛十分热烈,大家针对学习和工作中遇到的难点进行交流和讨论,可谓受益匪浅。 新手遇到的是新问题,对于有相关经验的工程师而言,可能都遇到过。 作为算法、FPGA和IC等集中交流的平台,群贤毕至,集思广益,解决大家对相关知识和技术上的困惑,让问题变得更简单。 群友们提到一个

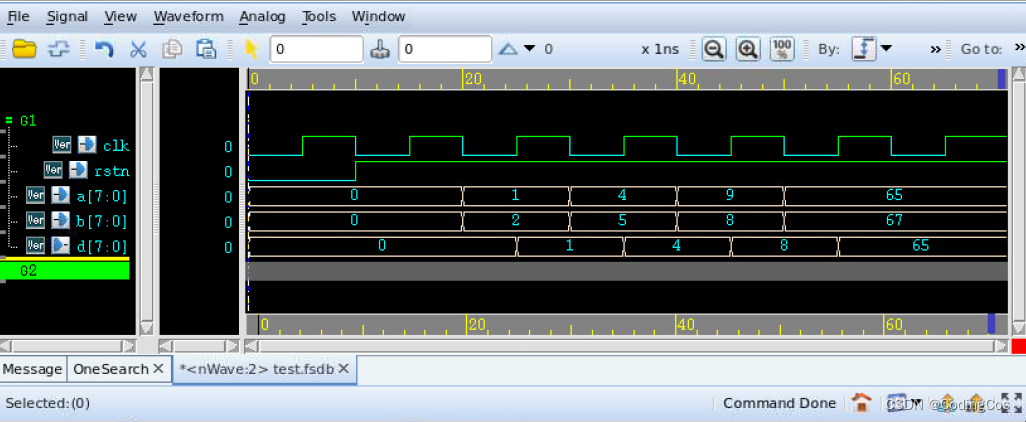

【芯片设计- RTL 数字逻辑设计入门 11 -- 移位运算与乘法】

请阅读【嵌入式开发学习必备专栏 】 文章目录 移位运算与乘法Verilog CodeTestbench CodeVCS 波形仿真 问题小结 移位运算与乘法 已知d为一个8位数,请在每个时钟周期分别输出该数乘1/3/7/8,并输出一个信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效) 可以看到输入D 的波形在为6的地方比较特殊,从波形上可以看到它只持续了一个

ONLYOFFICE桌面编辑器8.0新特性:PDF表单、RTL支持、Moodle集成、本地界面主题等

ONLYOFFICE是由领先的IT公司—Ascensio System SIA经验丰富的IT专家开发的项目。这是一款强大的在线编辑器,能够为提供高效的文本文档、电子表格、演示文稿、表单和 PDF 编辑工具。 继 ONLYOFFICE 文档 v8.0发布后,适用于 Linux、Windows 和 macOS 的免费ONLYOFFICE 桌面应用程序也进行了更新,带来 RTL 界面、本地界面主题

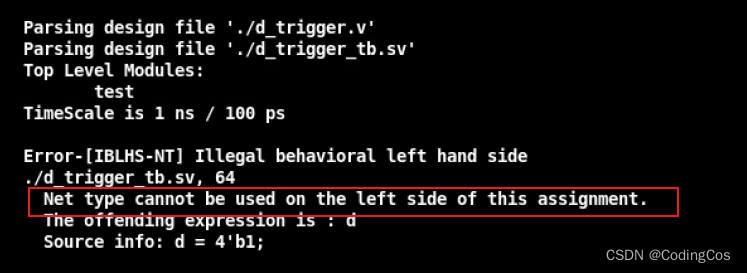

【芯片设计- RTL 数字逻辑设计入门 6 -- 带同步复位的D触发器 RTL实现及testbench 验证】

文章目录 带同步复位的D触发器Verilog 代码testbench 代码编译及仿真问题小结 带同步复位的D触发器 同步复位 :复位只能发生在在clk信号的上升沿,若clk信号出现问题,则无法进行复位。 Verilog 代码 // timescale ins/1nsmodule flopr (input rstn,input clk,input[3:0] d,

![HLS报错之:Export RTL报错 “ERROR: [IMPL 213-28] Failed to generate IP.“](https://i-blog.csdnimg.cn/direct/bb2ba2deb94f415081196fa462de6837.png)