本文主要是介绍基于 RK3399+fpga 的 VME 总线控制器设计(二)硬件和FPGA逻辑设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

3.2 FPGA 最小系统设计

FPGA 最小系统是指可以使 FPGA 正常工作的最基本的系统,主要包括电源电

路、配置电路、时钟和复位电路。本次设计使用的 FPGA 为紫光同创的 PG2L100H,

接下来具体介绍 FPGA 最小系统各个部分的电路设计。

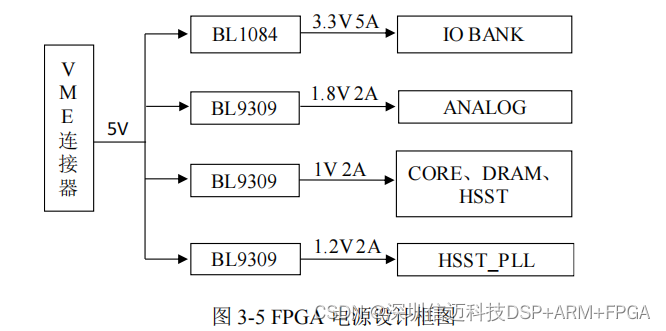

( 1 )电源电路设计

FPGA 所需要的电源电压有 3.3V 、 1.8V 、 1.2V 和 1V 。其中,内核逻辑电源和

专用 RAM 模块( DRAM )电源为 1V , FPGA 辅助电源为 1.8V , IO BANK 电源使

用 3.3V , HSST 高速串行接口的模拟电源需要 1V 和 1.2V 。 FPGA 电源设计框图如

下图 3-5 所示。

使用上海贝岭的电源芯片 BL1084 和 BL9309 对输入的 5V 电源进行转换。

BL1084 为 LDO 电源,可输出固定的 3.3V 电源,输出电流最大可达到 5A 。 BL9309

输出电压可调节,使用电阻分压得到 1V 、 1.2V 和 1.8V 电源,输出电流最大为 2A 。

(

2 )配置电路设计

PG2L100H 支持多种配置模式,本次设计使用 JTAG 模式和 Master SPI 模式。

JTAG 接口可以将程序下载到 FPGA 内部的 SRAM 里,也可以将程序固化到外部

Flash 。

在 Master SPI 模式下,程序保存在外部的 SPI Flash 里, FPGA 上电时会主动

从 Flash 读取位流。

本次设计使用兆易创新的 SPI Flash 作为 FPGA 的外部配置器件, Flash 型号为

GD25Q32CSIGR ,容量为 32Mb ,符合设计需求。

(3)时钟和复位电路设计

FPGA 是基于时钟工作的,时钟电路和复位电路必不可少。本次设计使用深圳

扬兴科技的 50MHz 的有源晶振作为 FPGA 的系统时钟输入,将此时钟接到 FPGA

的全局时钟管脚上。 50MHz 的时钟在 FPGA 内部经过锁相环分频得到 16MHz 的

时钟,将此时钟输出给 VME 总线连接器。此外,

FPGA 的 PCIE 接口还需要 100MHz

的差分参考时钟,由 RK3399 处理器输出给 FPGA 。 FPGA 时钟设计框图如下图 3-

6 所示。

FPGA 的上电复位来自 RK808-D 输出的复位信号,由于 RK808-D 输出的复位

信号电平为 1.8V ,而 FPGA 的 IO 电平为 3.3V ,所以需要进行电平转换,使用江

苏润石的电平转换芯片进行转换。此外, FPGA 还有一个复位按键可以进行手动复

位。

3.4 VME 接口电路设计

作为一个嵌入式控制器板卡,要实现与其他功能板卡的通信还需要借助于计

算机总线来完成。本课题设计的控制器需要最终需要工作在 VME 测试系统中,所

以需要设计 VME 接口电路。

由于 RK3399 处理器内部没有 VME 相关的控制器,所以需要自行完成 PCIE

与 VME 总线的接口逻辑设计。由于 VME 总线接口是由 FPGA 逻辑实现,所以将

RK3399 上的 PCIE 接口连到 FPGA 上, RK3399 通过 PCIE 总线对 FPGA 内部寄存

器读写实现对 VME 总线的控制。 VME 接口设计如图 3-11 。

VME 总线接口通过 FPGA 逻辑与驱动电路的配合来实现,在 FPGA 内部设计

PCIE 接口与 VME 接口的转换。由于 FPGA 的 IO 电压为 3.3V ,而 VME 总线信号

电平为 5V ,需要通过驱动电路进行电平转换。使用江苏润石的 245 双向驱动器来

完成 VME 连接器和 FPGA 之间的电平转换。

FPGA 逻辑设计即使用 VerilogHDL 或者 VHDL 语言,设计出系统所需要的数

字逻辑电路。本课题的 FPGA 逻辑设计主要完成 PCIE 总线与 VME 总线的接口转

换,本章主要从 PCIE 接口逻辑和 VME 接口逻辑两个部分进行详细介绍。

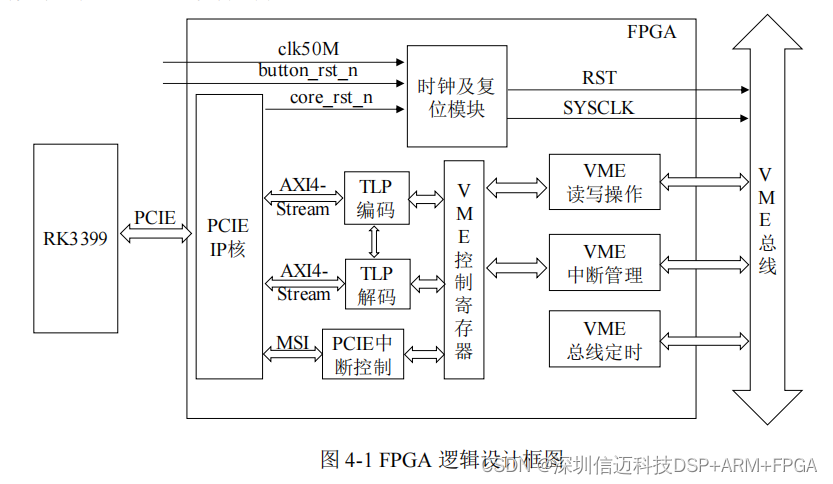

4.1 FPGA 逻辑设计方案

FPGA 逻辑主要实现 PCIE 总线到 VME 总线的接口转换,逻辑设计框图如图

4-1 所示,主要包括 PCIE 接口逻辑和 VME 接口逻辑两大部分。在 FPGA 内部设

计了对 VME 进行控制的相关寄存器,通过 PCIE 总线对这些寄存器进行读写,从

而实现对 VME 总线的控制。

4.2 PCIE 接口逻辑设计

PCIE 接口逻辑主要由深圳信迈实现 RK3399 处理器和 FPGA 之间的通信, RK3399 作为

PCIE 的 Root Complex ( RC ), FPGA 作为 PCIE 的 Endpoint 。通过地址映射的方式

将 CPU 地址映射到 PCIE 设备的 BAR0 和 BAR1 存储空间,通过 BAR1 来访问

VME 总线地址,通过 BAR0 进行控制寄存器的读写。

在紫光同创 FPGA 平台上,利用 PCIE IP 核设计 PCIE 接口逻辑。 PCIE IP 是

按照 PCIE2.1 协议实现的,支持配置链路宽度为 X1 、 X2 、 X4 ,支持配置链路速度

为 2.5GT/s 、 5GT/s 。 PCIE IP 主要实现 PCIE 协议的事务层、数据链路层和物理层

的功能,并向用户提供 AXI4-Stream 接口,以实现应用层和事务层之间的数据传

递。

PCIE 接口逻辑包括 PCIE IP 、 TLP 解码模块、 TLP 编码模块、 PCIE 中断控制

模块、时钟及复位、地址映射和控制寄存器设计。其中, TLP 是 PCIE 的事务层包,

包括头标( Header )和数据( Data )两部分。 TLP 解码和编码都是通过 AXI4-Stream

总线接口来进行设计的, AXI4-Stream 是一种并行总线,没有地址信号线,通过 valid

和 ready 握手信号进行数据传输。 PCIE IP 提供 AXI4-Stream Master 接口和 AXI4-

Stream Slave 接口,用户可以据此设计 TLP 解码和编码逻辑。

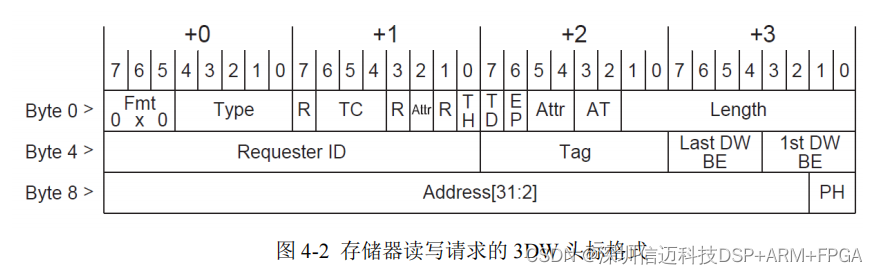

4.2.1 TLP 解码模块设计

TLP 解码模块接收来自 PCIE IP 的 TLP 事务层包,并进行解析,获得地址和

数据等信息。 TLP 的 Header 长度为 3DW 或 4DW 。存储器读写请求事务的 3DW

头标格式如图 4-2 ,标有 R 的部分未使用,应当设置为 0 [42]。

其中, Fmt 和 Type 规定了事务的相关信息。 TC 表示传输等级, PCIE 规定了

8 种 TC ,分别为 TC0~TC7 ,默认为 TC0 。 Attr 字段有 3 位,第 2 位表示是否支持

ID-based Ordering ,第 1 位表示是否支持宽松排序( Relaxed Ordering ),第 0 位表

示是否需要进行 Cache 一致性处理。本设计中 Attr[2:0] 为 000 ,表明 TLP 的序为缺

省序,即强序模型,且通过总线监听自动完成 cache 一致性。使用强序模型时,处

理相同类型的 TLP 时,必须等当前的传输完成再传输下一个;不同种类的 TLP 事

务包可以乱序通过。

长度 Length 为 TLP 包的数据长度,单位为 DW 。 1st DW BE 对应数据的第一

个双字的四个字节, Last DW BE 对应数据的最后一个双字的四个字节,为 0 时说

明对应的字节无效,为 1 有效。

Tag 的长度决定了 PCIE 发送端能够暂存同类型 TLP 的个数, Tag 一般只使用

低 5 位,即可以暂存 32 个 TLP ,如果使能了 Extended Tag 位, Tag 使用 8 位,发

送端可以暂存 256 个 TLP 。由于存储器写请求不返回完成包,所以不使用 Tag 标

签, Tag 字段置为 0 。 Address[31:2] 为 32 位寻址方式的存储器读写地址, 32 位地址

的低两位保留(

00b ),强制起始地址为 DW 对齐。

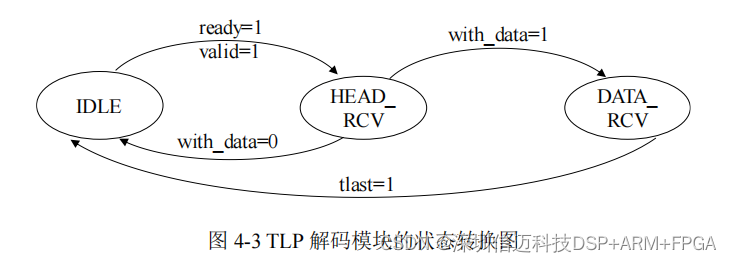

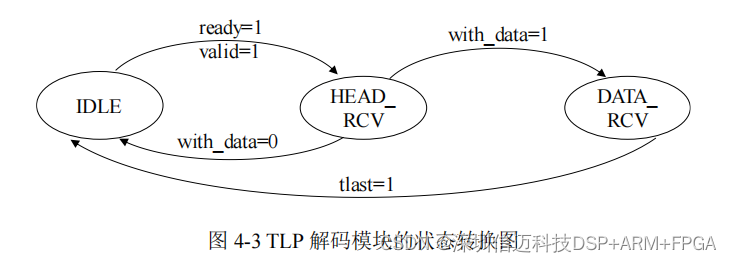

TLP 解码使用 AXI4-Stream Master 接口,主要通过设计状态机来实现,如图

4-3 为 TLP 解码的状态转换图。

TLP 解码状态机包括 IDLE 、 HEAD_RCV 、 DATA_RCV 三个状态。其中,初

始状态为 IDLE ,系统复位后进入此状态, IDLE 状态下将地址和数据等寄存器清

零。当 ready 和 valid 均为 1 时,说明开始传输数据且数据有效,跳转至 HEAD_RCV

状态。在 HEAD_RCV 状态下,开始接收 TLP 的 Header 信息,并将 TLP 事务类型

和地址解析出来。当 with_data 为 1 时,说明 TLP 事务类型为存储器写事务,包含

有数据,故跳转至 DATA_RCV 状态;当 with_data 为 0 时,说明 TLP 事务类型为

存储器读事务,不包含数据,故跳转至 IDLE 状态。在 DATA_RCV 状态下,接收

TLP 的 Data ,当 tlast 为 1 时,说明数据传输结束,跳转至 IDLE 状态,准备接收

下一个 TLP 事务层包。

此外, AXI4-Stream Master 接口还有一个 tuser 信号,该信号有 8 位,其中 [6:4]

这 3 位用来指示 TLP 包要对哪个 BAR 进行操作。

4.2.2 TLP 编码模块设计

TLP 编码模块主要是将来自 VME 总线的数据和地址打包成 TLP 事务层包,

发送给 PCIE IP, 通过 AXI4-Stream Slave 接口实现 TLP 编码。下图 4-4 为 TLP 编

码的状态转换图。

TLP 编码状态机包括 IDLE 、 HEAD_TX 、 DATA_TX 三个状态。其中,初始状

态为 IDLE ,系统复位后进入此状态,当 tready 为 0 时说明 RC 端未准备好,状态

依然保持为 IDLE 。当 tready 为 1 且 data_valid 为 1 时,跳转至 HEAD_TX 状态。

在 HEAD_TX 状态下,将 TLP 各个字段的信息进行组合,因完成包的头标长度固

定为 3DW ,所以组合成长度为 3DW 的头标,发送给 PCIE IP ,并将 tready 信号置

为高电平,表明数据有效。当 tready 为 1 时,跳转至 DATA_TX 状态,在此状态下

发送完成包的数据, tready 信号依旧置为高电平。发送完数据后,跳转至 IDLE 状

态,将 tready 信号置为低电平。

4.2.3 PCIE 中断控制设计

PCIE 总线支持两种类型的中断,一种是消息信号中断( MSI ),另一种是虚拟

INTx 信号中断。 MSI 中断是 PCIE 设备通过存储器写事务,将消息数据寄存器中

的内容写入其消息地址寄存器所规定的存储器地址,从而向处理器提交中断请求。

虚拟 INTx 中断是使用中断消息来模仿 PCI 兼容的中断信号,传达 INTx# 信号的跳

变情况。

MSI 中断的效率比较高,它不需要软件去确认是哪个设备产生了中断,即不用

识别中断源。所以本次设计使用 MSI 中断,在 PCIE IP 设置界面里使能 MSI 中断。

在接收来自 VME 的中断后,拉高 MSI 中断请求信号, PCIE IP 会将中断请求提交

至 CPU 的 PCIE 控制器, CPU 接收到中断后可以进行相应的操作。在 CPU 收到

MSI 中断请求后,将 MSI 中断请求信号拉低,防止 CPU 接收到重复的中断。

在使用 MSI 中断的时候,需要注意存储器同步问题,即 CPU 在接收到 MSI 中

断请求后立即去执行中断处理程序,这个时候可能会打断当前的读写操作。为避免

这种问题,可以在设计时确保应用数据的存储器写事务和 MSI 存储器写事务的 TC

号一样,这样就不会打断当前的存储器写事务了。

4.2.4 地址映射和控制寄存器设计

通过地址映射的方式将 CPU 地址映射到 PCIE 设备的 BAR0 和 BAR1 存储空

间,通过 BAR0 进行控制寄存器的读写,通过 BAR1 来访问 VME 总线地址。由于

VME 总线的地址线为 24 ,所以将 BAR1 的空间大小设置为 16MB ,并根据控制寄

存器的实际使用情况将 BAR0 的空间大小设置为 256B ,以上内容均在 PCIE IP 核

中进行设置。

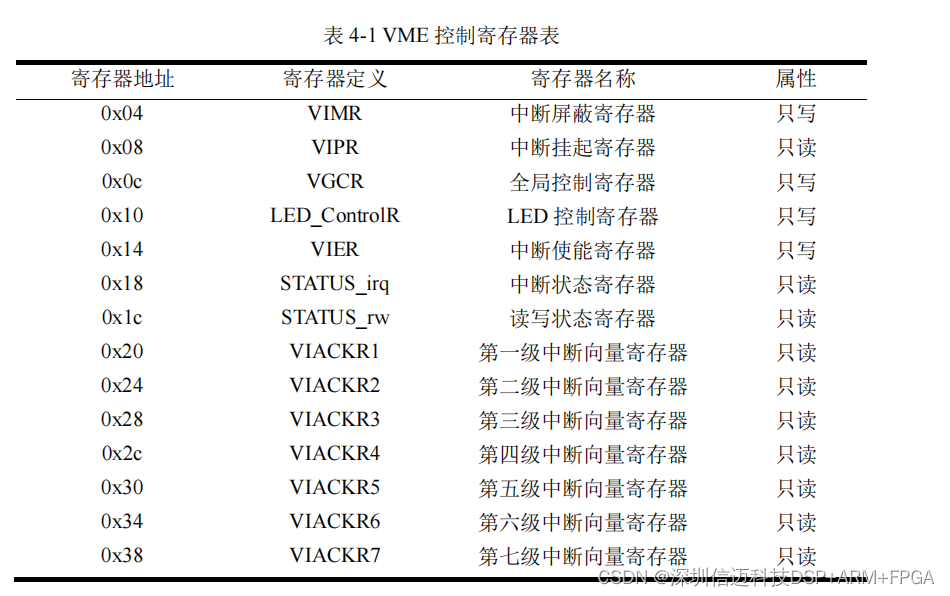

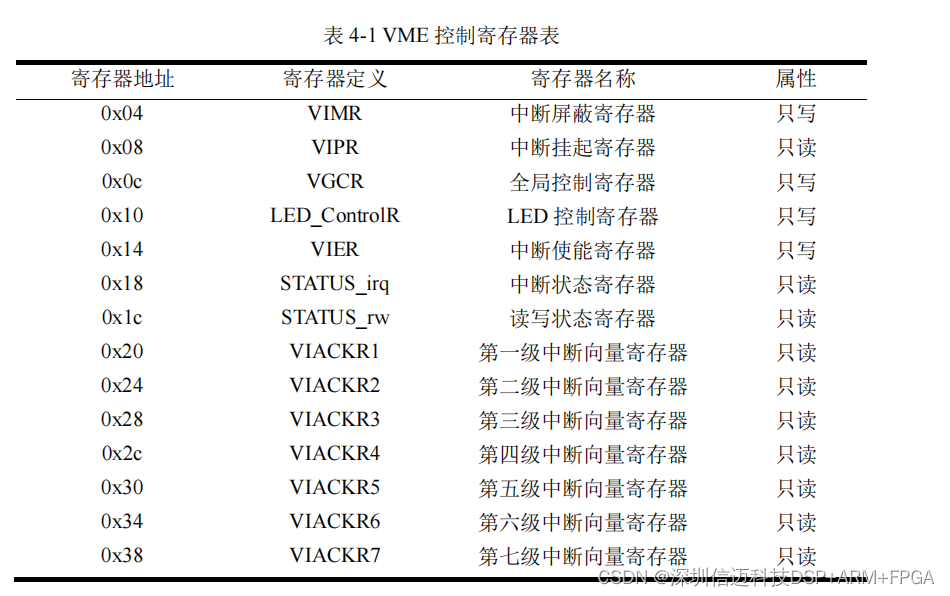

为了实现对 VME 总线的控制,需要定义一些控制寄存器,并将这些控制寄存

器的地址映射到 PCIE 设备的 BAR0 空间。本课题定义的 VME 控制寄存器如下表

4-1 所示,由于 PCIE 存储空间的读写地址为双字对齐,所以本次设计的控制寄存

器的地址为 4 的倍数。

这些寄存器 Register 大致可分为两类,一类是中断控制相关的寄存器,一类是

读写控制相关的寄存器。中断控制相关的寄存器包括中断屏蔽、中断挂起、中断使

能、中断向量和中断状态寄存器。中断屏蔽 Register 用来对某一级或某几级中断进

行屏蔽,使用户只接收到自己所需要的中断。中断挂起 Register 用来指示哪一级中

断产生了。中断使能 Register 用来对 VME 中断进行使能或禁能。中断向量 Register

用来读取中断向量,从而使用户可以进行相应的中断处理。中断屏蔽和中断挂起寄

存器均定义了 8 位,第 0 位不使用。

读写控制相关的寄存器包括全局控制寄存器、读写状态寄存器和 LED 控制寄

存器。全局控制寄存器用来对地址模式和数据读写方式进行控制,地址模式包括 16

位地址和 24 位地址两种,数据读写方式有 16 位数据读写、 8 位偶地址读写、 8 位

奇地址读写三种。读写状态寄存器用来指示 VME 总线读写是否正常完成,该寄存

器值为 1 表示写正常完成, 2 表示读正常完成, 4 表示数据读写方式错误, 8 表示

超时错误。 LED 控制寄存器用来对前面板的 LED 灯进行控制,当系统上电后点亮

LED 灯。

VME 控制寄存器模块是 PCIE 接口与 VME 接口之间的桥梁,通过此模块实

现 PCIE 总线与 VME 总线的接口转换。本模块将来自 TLP 解码模块的 PCIE 地址

映射到 BAR0 、 BAR1 空间,实现对 BAR0 空间里的 VME 控制寄存器的读取和写

入,对 BAR1 空间里的 VME 总线数据写入和读取。并且将 VME 控制寄存器的具

体内容和 VME 总线的数据和地址传递至 VME 读写操作模块和 VME 中断管理模

块。此外需要注意的是,当 VME 接口的 VME 总线读写操作未完成时,需要进行

等待,直到 VME 总线读写完成之后,再进行下一次的读写操作。

4.3 VME 接口逻辑设计

VME 总线为异步并行总线,主要由数据传输总线( DTB )、数据传输的仲裁总

线、优先级中断总线和公用总线四部分构成。 DTB 的主要作用是在模块间传递数

据、地址和控制信号;仲裁总线负责控制和分配 DTB ,保证某一时间只有一个模

块控制 DTB ;优先级中断总线使得 VME 设备和中断管理器之间可以进行中断请

求和中断响应,中断请求可以 7 个中断优先级。

DTB 分为寻址线、数据线和控制线三大类。 VME 背板可配置为 16 或 32 条数

据线, 16 条数据线的背板一次可同时访问 2 个字节的数据, 32 条数据线的背板一

次可同时访问 4 个字节的数据。 DTB 控制线包括 AS* 、 DS0* 、 DS1* 、 DTACK* 、

WRITE* 和 BERR* 。 AS* 由高变低说明地址选通,可以使用。 DS0*/ DS1* 的第一个

下降沿在写周期表明主模块已将有效数据放到数据总线上了,在读周期用来告诉

从模块可以将数据总线上的数据撤掉。 WRITE* 为电平有效信号,为低电平时表明

数据是从主模块向从模块传输,为高电平时表明数据是从从模块向主模块传输。

BERR* 由从模块或总线定时器驱动,为低时表明数据传输出现错误。

本课题中的 VME 接口逻辑设计主要包括 VME 读写操作模块、 VME 中断管

理模块、 VME 定时模块、时钟驱动和复位逻辑等。时钟驱动和复位逻辑主要是产

生 VME 总线的系统时钟 16MHz 和复位信号。系统时钟可以由锁相环分频得到,

复位信号通过按键复位来产生。接下来具体介绍 VME 读写操作模块、中断管理模

块和定时模块的设计。

4.3.1 VME 读写操作模块

本课题设计 VME 读写操作模块来控制 VME 总线数据传输,实现 VME 总线

读写操作,并且数据读写支持三种访问方式。基本的设计原则是通过握手信号实现

数据异步传输, VME 控制器使用 AS* 、 DS0* 、 DS1* 向从模块发出控制信息,而

VME 功能模块使用 DTACK* 来进行应答。

VME 读写操作模块采用状态机来实现,状态转换图如图 4-5 所示。初始状态

为 IDLE ,当收到读或者写请求且总线未被占用时,跳转至 AS(地址选通)状态,

若总线被占用则一直处于 IDLE 状态。在 AS 状态下,延时 40ns 后,驱动 AS 信号

为低并驱动 WRT 信号,跳转至 DS (数据选通)状态。在 DS 状态下延时 40ns ,

然后根据数据读写方式来驱动 DS 信号,并跳转至 DTACK (数据传输应答)状态。

在 DTACK 状态下,若 DTACK 信号为低,说明数据传输成功,拉高 AS 和 DS 信

号,跳转至 WR_CLR (写清除)状态;若 BERR 信号为低,说明总线出现超时错

误,此时同样需要拉高 AS 和 DS 信号,跳转至 WR_CLR 状态。在 WR_CLR 状态

下,延时 20ns 后清除 WRITE 信号和读写标志信号,并跳转至 END (结束)状态。

在 END 状态下,延时 40ns 跳转至 IDLE 状态。

4.3.2 VME 中断管理模块

中断模块用来对 IRQ1 到 IRQ7 中断进行接收和处理,当 VME 中断模块接收

到 VME 中断后,进行中断应答操作并将中断信息传递至 PCIE 中断控制模块,由

PCIE 中断控制模块向 RK3399 提出 MSI 中断申请, RK3399 通过读取中断挂起和

中断向量寄存器来确定中断产生了哪一级及中断类型。具体实现过程如下:

( 1 ) VME 中断管理模块接收到 VME 设备的中断请求 IRQ 后,将中断级别信

息写入到相应的中断挂起 Register ,并将中断传递至 PCIE 中断模块。

(2) PCIE 中断控制模块接收到来自 VME 中断模块的中断后,向 RK3399

发起 MSI 中断请求。

(3) RK3399 接收到 PCIE 设备的 MSI 中断请求后,进入中断处理函数,禁

止使能中断,读取中断挂起寄存器,查看 1 — 7 哪一级发生了中断,并读取中断向

量进行相应的中断处理。

(4) VME 寄存器控制模块得知 RK3399 读中断向量后,向 VME 中断控制模

块传递 IACK_en 信号,表明可以进行应答操作。

(5) VME 中断管理模块开始中断应答,驱动 IACK* 为低电平。读取来自 VME

功能模块的中断向量并传递至 VME 寄存器控制模块。

(6)应用程序里的中断处理完成之后, RK3399 写中断使能,告诉 PCIE 设备

中断已经得到处理,可以接收下一次中断。

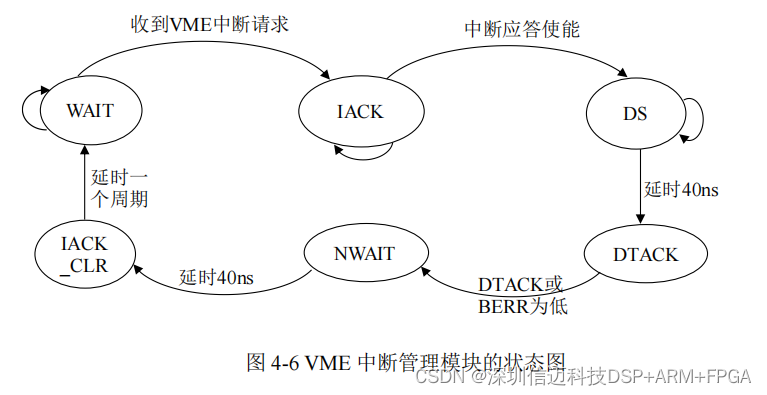

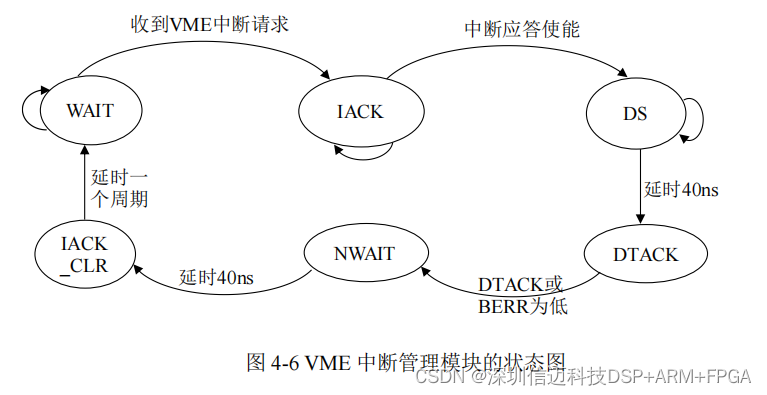

VME 中断模块的状态转换图见图 4-6 。初始状态为 WAIT 状态,当接收到 VME

中断请求后,向 PCIE 中断模块传递中断,并跳转至 IACK (中断应答)状态,否

则一直处于 WAIT 状态。在 IACK 状态下,若收到中断应答使能信号,说明处理器

已接收到中断请求,中断管理模块进行中断应答,并跳转至 DS 状态,否则一直处

于 IACK 状态。在 DS 状态下,延时 40ns 后驱动 DS 和 AS 信号有效并跳转至

DTACK 状态。在 DTACK 状态下,当 DTACK 或 BERR 信号为低电平时,驱动

IACK 、 AS 和 DS 信号无效,并跳转至 NWAIT 状态。在 NWAIT 状态下,延时 40ns

跳转至 IACK_CLR 状态, IACK_CLR 状态表示中断完成,延时一个周期跳转至初

始状态。

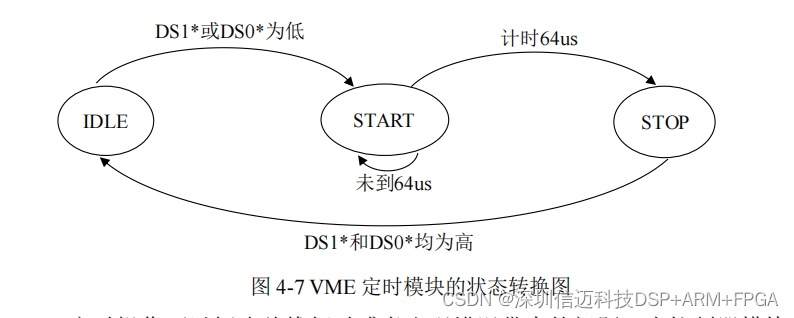

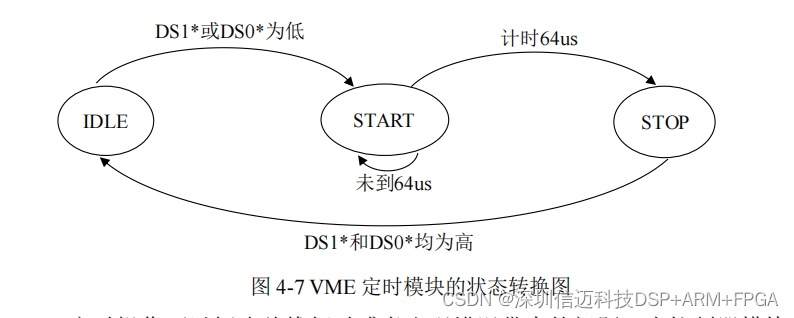

4.3.3 VME 定时模块

VME 总线定时模块的功能是对 VME 总线定时 64us ,当 VME 总线出错超过

64us 时,驱动总线错误线 BERR* 为低,输出超时错误。 VME 定时有两种方式,一

是不论 DTACK* 和 BERR* 的电平为高或者低,当 DS1* 和 DS0* 这两个信号中的任

意一个维持为低的时间超过 64 微秒,就将 BERR* 信号拉低。二是当 DS1* 和 DS0*

这两个信号中的任意一个维持为低的时间超过 64 微秒,且 DTACK* 和 BERR* 均

为高时,拉低 BERR* 信号。

本次 VME 定时模块设计使用第二种方法,设计状态机来进行 64us 的定时操

作。状态机包括三个状态,分别为起始状态( IDLE )、计时开始状态( START)和

停止状态( STOP )。 VME 定时操作的状态转换图见下图 4-7 。

系统复位后进入 IDLE 状态,当 DS1* 和 DS0* 其中一个为低或者均为低电平

时,由初始状态跳转至定时开始状态,开始计时。当 DTACK* 由高变为低时或者时

间达到 64us ,由计时状态跳转至停止状态,若跳转条件为达到 64us ,将 BERR* 驱

动为低电平;不满足跳转条件的话停留在计时状态。当 DS1* 和 DS0* 均为高,由停

止状态跳转到初始状态并将 BERR*拉高。

VME 定时操作可以解决总线超时或者出现错误带来的问题,当控制器模块对

没有定义的地址进行操作或者其他 VME 功能模块出现错误时,可以进行报错并结

束此次操作,提高总线工作的效率。

信迈提供RK3399+FPGA的解决方案。

这篇关于基于 RK3399+fpga 的 VME 总线控制器设计(二)硬件和FPGA逻辑设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!