存器专题

D触发器(D Flip-Flop)与D锁存器(D Latch)

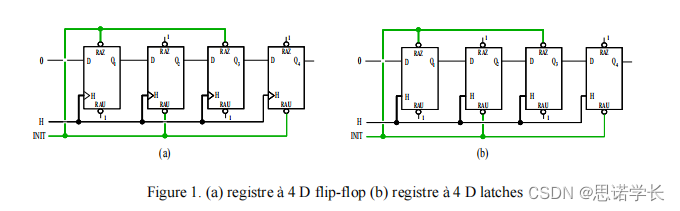

1 基础概念 我们先来简单回顾一下D触发器(D flip-flop)和D锁存器(D latch)的概念,以及它们在数字电路中的作用。 1.1 D触发器(D Flip-Flop) D触发器是一种数字存储器件,它在时钟信号的特定边沿(上升沿或下降沿)上捕获并存储输入信号的状态。因此,它被称为边沿触发设备。 在给定的时钟边沿到来时,如果D输入为高(1)

锁存器的工作原理及其在FPGA设计中的注意事项

锁存器(Latch)是数字电子中常用的一种基本元件,用于在特定的时间点或条件下“锁存”或保存输入的数据值。锁存器对脉冲电平敏感,它只在输入脉冲的高电平(或低电平)期间对输入信号敏感并改变状态。在数字电路中可以记录二进制数字信号“ 0”和 1”。 锁存器的主要作用: 缓存数据。解决高速控制器与慢速外设之间的不同步问题。解决驱动问题。解决一个I/O口既能输出也能输入的问题。 锁存器的工作原理:

数字信号处理:关于锁存器Latch的发现

关于锁存器的发明,有下面一段伪历史,所谓伪历史,就是我不想去考证发明人是否有这样一条思路,但是这肯定算是一个思路。 伪历史是这样开始的,人们先发明了反相器,就如下图所示。 接着,人们开始考虑去搞一个循环 现在需要详细看看这个循环了,这个循环是这样的,两个反相器串联起来,再把第二个反相器的输出接到第一个反相器的输入。 假设: 在A处,上帝创造了一个信号X,X可以是1,也可以是0

第四篇 锁存器、触发器、寄存器

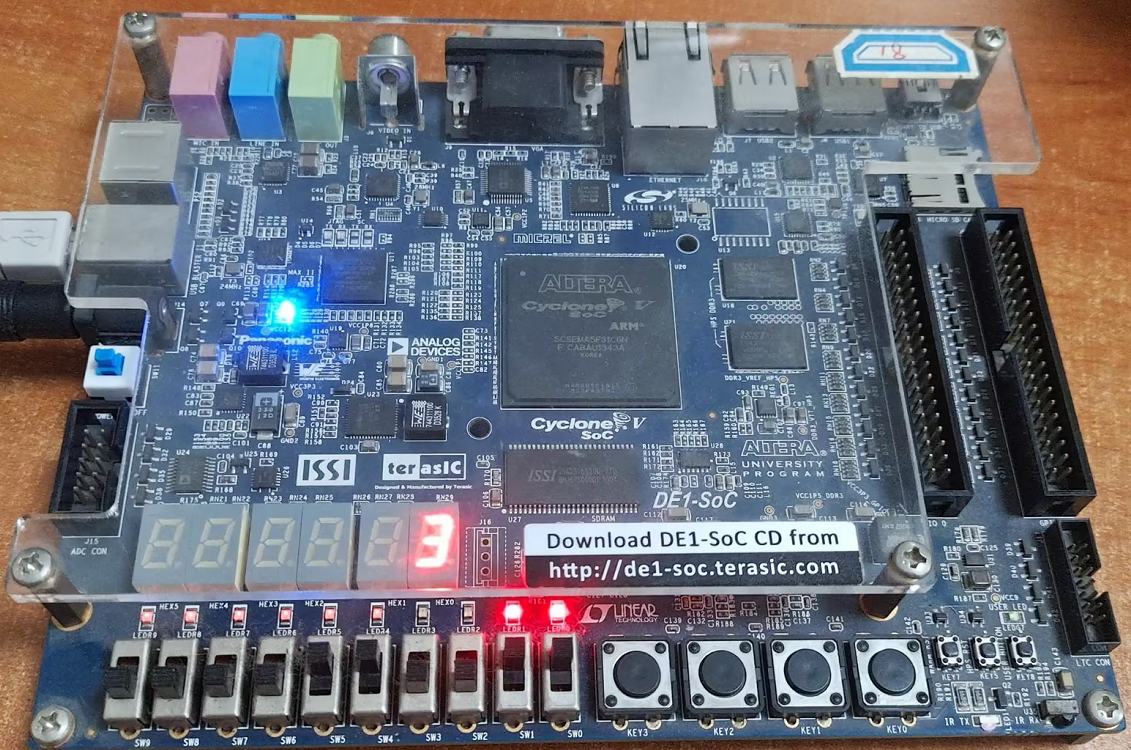

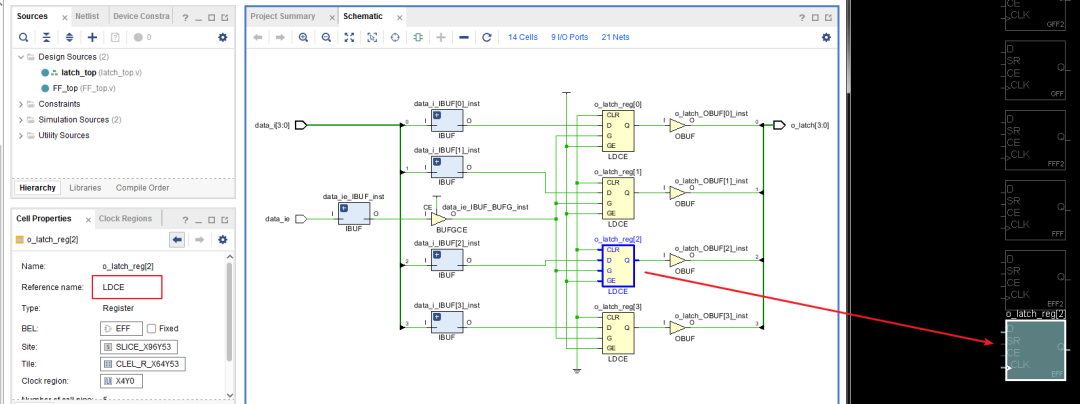

实验四 锁存器、触发器、寄存器 4.1 实验目的 理解时序逻辑电路的概念和基本原理; 掌握锁存器、触发器和寄存器的原理和架构及代码实现; 熟悉数字电路的设计、仿真流程,最后在DE1-SOC开发板上验证设计 。 4.2 原理介绍 4.2.1 时序逻辑电路 前三个实验中,我们学习了基本的逻辑门、多路数据选择器、译码器,这些电路都是组合逻辑电路,也就是任一时刻产生的输出信号仅仅取决于该

FPGA基础:触发器和锁存器

目录 锁存器(Latch)D触发器(Flip-Flop)最基本时序电路时序块(Sequential blocks):同步与异步触发器概念触发器分类触发器的Verilog实现1. 上升沿触发的触发器2. 带异步复位、上升沿触发的触发器3. 带异步复位和置位、上升沿触发的触发器4.带异步复位和同步使能、上升沿触发的触发器5.带同步复位、上升沿触发的触发器 锁存器(Latch) mo

数字IC/FPGA——锁存器/触发器/寄存器

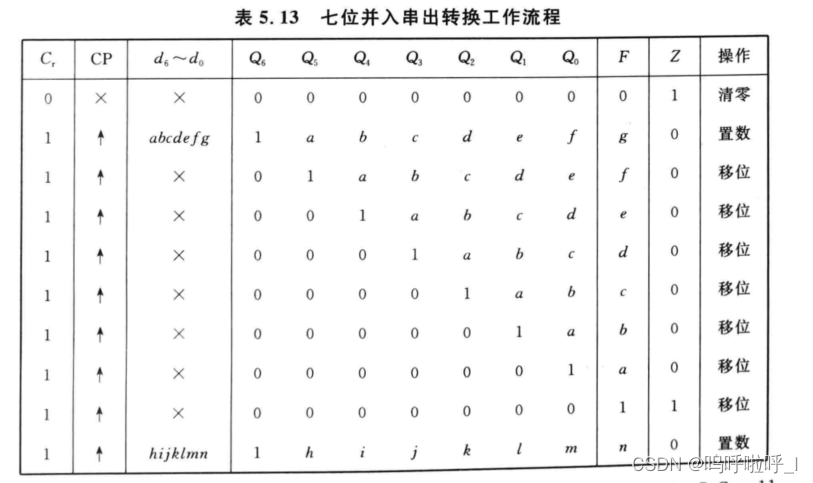

本文主要介绍以下几点: 什么是触发器和锁存器门电路和触发器的区别什么是电平钟控触发器电平钟控触发器触发器和锁存器的区别触发器的分类方式:逻辑功能、触发方式、电路结构、存储数据原理、构成触发器的基本器件寄存器利用移位寄存器实现串并转换或并串转换 目录 一、触发器的基本概念二、触发器的分类及原理1.RS触发器(1)与非门RS触发器(2)或非门RS触发器 2.电平触发钟控触发器(1)钟控RS触

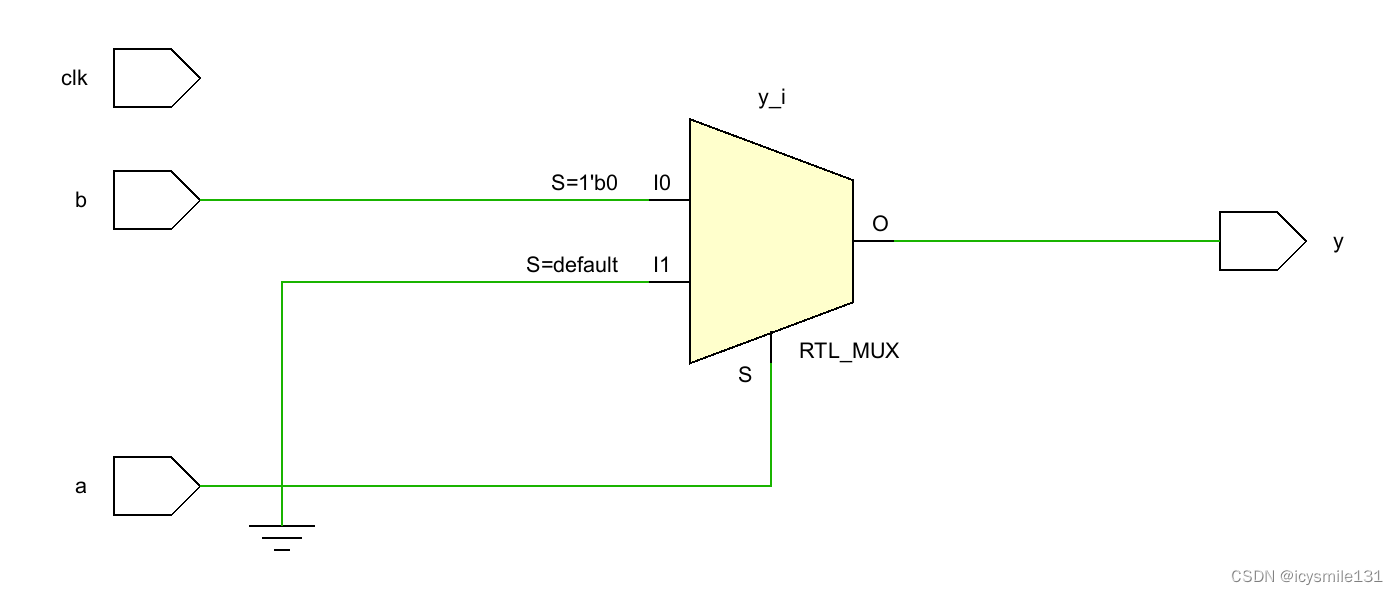

带锁存器的时序逻辑综合

带锁存器的时序逻辑综合 锁存器的无意综合锁存器的有意综合 🔈声明: 🔑未经作者允许,禁止转载 🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈 锁存器生成的方式有两种:有意的和无意的。无意综合出的锁存器只会浪费面积,所以知道什么时候该综合出锁存器就很有必要。 一个无反馈的组合原语网表可综合成无锁存的组合逻辑描述组合逻

锁存器、触发器、寄存器和缓冲器的区别

一、锁存器 锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。 锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。锁存器也称为透明锁

寄存器,触发器,锁存器之间…

原文地址:寄存器,触发器,锁存器之间的区别与联系 作者:SUN_403 寄存器一般是边沿触发的触发器,电路里叫register,而触发器就是各种逻辑门构成的包含电平触发和边沿触发的两种,而锁存器则是电平触发的。所以一般说来,我们只叫寄存器和锁存器两种,在时序电路中寄存器的作用就是只在时钟的边沿有效传输data(setup time和hold time满足),而锁存器则在有效电平器件

数学电路与电子工程1(MEE)—— 锁存器和触发器

1 逻辑综合 1.1 DCB/DEC转换器 下图是一个74HC42集成电路的逻辑图,它是一个二进制编码的十进制(BCD to Decimal)转换器,也称为DCB/DEC转换器。这种类型的IC通常用于将4位二进制数(BCD)转换为十进制输出。 在这个IC中,有四个输入,它们代表一个4位的二进制数。这四个输入可以转换为从0到9的十进制数字,这是由于BCD编码

FPGA的设计中为什么避免使用锁存器

前言 在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数文章都对锁存器有个误解,我们后面会详细说明。 这篇文章,我们包含如下内容: 锁存器、触发器和寄存器的原理和区别,为什么锁存器不好?什么样的代码会产生锁存器?为什么锁存器依然存在于FPGA中?

74HC573锁存器简单应用

74HC573锁存器简单应用http://www.21ic.com/jichuzhishi/datasheet/74HC573/Latch/186096.html #include #define uint unsigned int #define uchar unsigned char uchar code table[]={0xc0,0xf9,0xa4,0x

数字逻辑电路基础-时序逻辑电路之锁存器

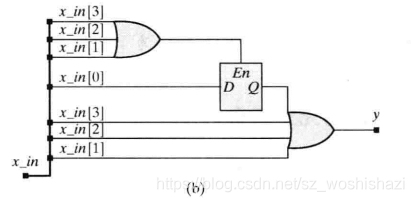

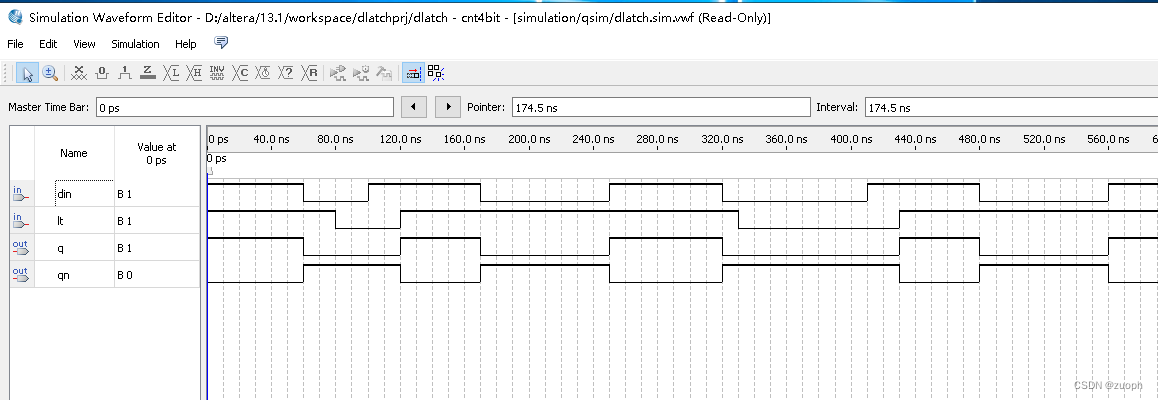

文章目录 一、锁存器简介二、verilog源码三、综合及仿真结果 一、锁存器简介 本文介绍数字逻辑电路中一种常用的基础时序逻辑电路-锁存,顾名思义,它的功能就是将输入在控制信号有效时透明传输到输出端,当控制信号无效时,输出值保持不变。它具有记忆和存储功能。这是它区别组合逻辑的基本点。 下图是锁存器的门级结构图。它由两个与非门、一个反相器及后级的RS锁存器构成。 锁存器

数字逻辑电路基础-时序逻辑电路之锁存器

文章目录 一、锁存器简介二、verilog源码三、综合及仿真结果 一、锁存器简介 本文介绍数字逻辑电路中一种常用的基础时序逻辑电路-锁存,顾名思义,它的功能就是将输入在控制信号有效时透明传输到输出端,当控制信号无效时,输出值保持不变。它具有记忆和存储功能。这是它区别组合逻辑的基本点。 下图是锁存器的门级结构图。它由两个与非门、一个反相器及后级的RS锁存器构成。 锁存器

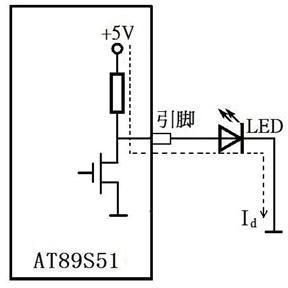

你知道真正的“读引脚”和“读锁存器”指令的区别吗

你知道真正的“读引脚”和“读锁存器”指令的区别吗 ///插播一条:我自己在今年年初录制了一套还比较系统的入门单片机教程,想要的同学找我拿就行了免費的,私信我就可以哦~点我头像黑色字体加我地球呺也能领取哦。最近比较闲,带做毕设,带学生参加省级或以上比赛/// 某些指令说明 -“读引脚”和“读锁存器”指令的区别 .关于并行I/O口的“读引脚”和“读锁存器”指令的区别 例如,当P1口的

state: d (disk sleep)_D触发器/锁存器 ? MC红石电路模块大百科

这些电路元件都非常基础,使用时无需声明原作者出处。(实际上,这些元件都可能被不同人在不同地方分别独自重复发明过许多次) 如果你发现了新的方案并且在这里面找不到,可以私信发给我进行补充。 D触发器/锁存器简介: D触发器介绍可参考:https://baike.baidu.com/item/D%E8%A7%A6%E5%8F%91%E5%99%A8 D触发器是在控制端的信号边沿(上升沿、下降沿或双边

锁存器和触发器、线与逻辑

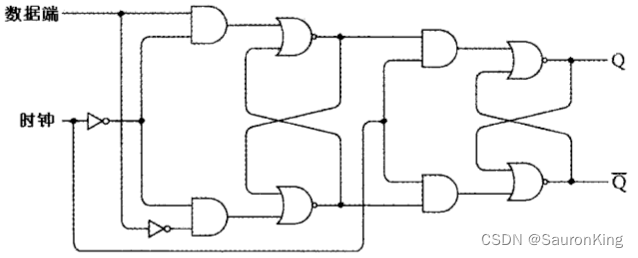

目录 锁存器与触发器线与逻辑 锁存器与触发器 锁存器:电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。 触发器:有交叉耦合的的门构成的双稳态的存储元件称为触发器。分为上升沿触发和下降沿触发。可以认为是两个不同电平敏感的锁存器串联而成。前一个锁存器决定了触发器的建立时间,后一个锁存器决定了保持时间,如下图所示。 锁存器的危害: 对毛刺

数字电路中触发器/锁存器的简单理解,与电路结构

1,为什么有触发器? 数字逻辑电路系统包含组合逻辑和时序逻辑。组合逻辑用来实现与状态无关的门电路,比如算法的实现函数,无反馈,无记忆;时序逻辑则主要用来同步电路的各个状态,有反馈,有记忆,如触发器,寄存器。 组合逻辑计算出来的值由时序逻辑保存下来,经过同步时钟(Clock)来控制逻辑值的传递。 比如实现一个如下的累加功能电路设计,如果不用触发器,则无法存储s的中

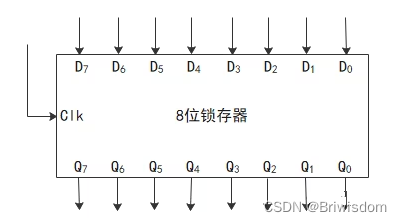

寄存器、锁存器的区别

触发器:能够存储一位信号的基本单元电路称为“触发器”; 锁存器:锁存器(或称作锁存器器)是数字电路中异步时序逻辑电路系统中用来储存资讯的一种电子电路。一个锁存器可以储存一比特的资讯,通常会有多个一起出现,有些会有特别的名称,像是 “4位锁存器”(可以储存四个比特)或“8位锁存器”(可以储存八个比特)等等。 一位D触发器只能传送或存储一位数据,而在实际工作中往往希望一次传送或存储多位数据。为此可

AMEYA360分析:纳芯微推出超低功耗TMR开关/锁存器 NSM105x系列

纳芯微推出基于隧道磁阻 (TMR) 的超低功耗磁开关/锁存器NSM105x系列,为数字位置检测提供高精度的解决方案,可被广泛应用于工业与消费领域的位置检测。 NSM105x产品系列包含了3个产品型号,即NSM1051(单极开关)、NSM1052(全极开关)、NSM1053(锁存器)。通过为用户提供不同的可选开关点、工作磁极、输出相位、采样频率、输出接口、封装形式等关键特性,NSM