本文主要是介绍VHDL——锁存器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

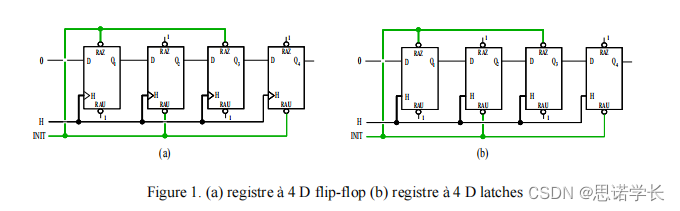

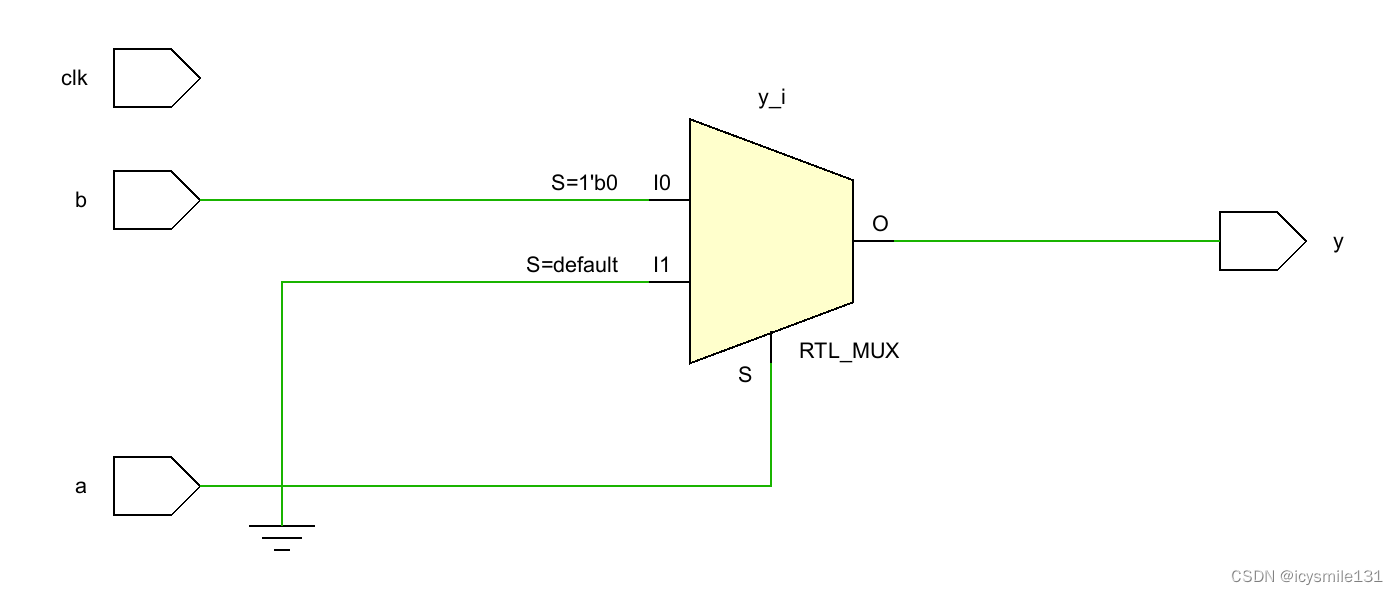

1.端口图

2.VHDL语言

library ieee;

use ieee.std_logic_1164.all;entity latch1 is

port( d : in std_logic ;q : out std_logic;ena : in std_logic);

end latch1;architecture example of latch1 is

signal sig_save : std_logic := '0' ;

beginprocess(d,ena)beginif ena = '1' then sig_save <= d ;end if ;q <= sig_save ;end process;

end example;

这篇关于VHDL——锁存器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!