本文主要是介绍D触发器(D Flip-Flop)与D锁存器(D Latch),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1 基础概念

我们先来简单回顾一下D触发器(D flip-flop)和D锁存器(D latch)的概念,以及它们在数字电路中的作用。

1.1 D触发器(D Flip-Flop)

D触发器是一种数字存储器件,它在时钟信号的特定边沿(上升沿或下降沿)上捕获并存储输入信号的状态。因此,它被称为边沿触发设备。

在给定的时钟边沿到来时,如果D输入为高(1),则触发器的输出Q变为高(1);如果D输入为低(0),则输出Q变为低(0)。此后,无论D输入如何变化,只要没有新的时钟信号边沿到来,Q的状态都不会改变。

1.2 D锁存器(D Latch)

与D触发器不同,D锁存器是一种电平触发设备。它根据控制输入(通常是使能信号)的电平变化来更新其输出。当使能信号为高电平时,D锁存器会捕获输入D的状态并将其反映到输出Q上。当使能信号变为低电平时,锁存器会保持其输出状态,直到使能信号再次变为高电平。

2. 具体描述

2.1 图片描述

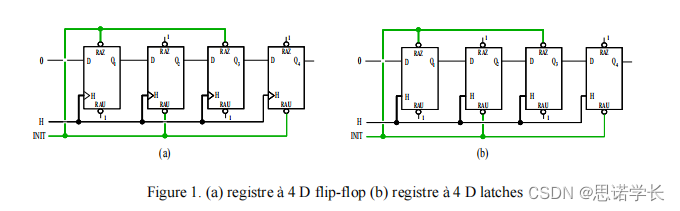

下图是两种类型的寄存器:一个是由4个D触发器构成的寄存器,另一个是由4个D锁存器构成的寄存器。在这个上下文中,寄存器是用来存储4位二进制数的设备。

忽略上升时间(tr),下降时间(tf),设置时间(tsu)和保持时间(th),只考虑传播延迟。传播延迟是信号从输入端到输出端所需的时间。题目给出了D触发器和D锁存器的传播延迟时间为10纳秒(ns)。

2.2 关键点

在这个图片中,我们需要理解的关键点是:

传播延迟(tp):信号从输入端到输出端的延迟时间。上文提到的D触发器和D锁存器的传播延迟都是10ns。

D触发器与D锁存器的区别:D触发器在时钟信号的特定边沿上同步操作,而D锁存器则在控制信号为特定电平时进行操作。

对于任何涉及这些寄存器的数字设计问题,理解它们的工作原理和它们之间的区别是非常重要的。这有助于我们正确地设计和分析数字电路,确保电路能够按照预期工作,特别是在需要精确控制信号时序的应用中。

2.3 深入分析

2.3.1 INT(初始化)信号

在这两种类型的寄存器中,INT(初始化)信号被用来控制寄存器的初始化或重置功能。在电子数字系统中,初始化通常是重置寄存器内容为零或某个预定义的值的过程。

2.3.1.1 对于图1(a)中的D触发器寄存器

INT信号通常用于异步清除或预设寄存器中的内容。当INT为低电平时,与INT连接的所有D触发器的输出Q将被置为低电平,不论时钟信号H的状态如何。这意味着不管时钟如何变化,只要INT是低电平,寄存器的输出都会被强制改变。

2.3.1.2 对于图1(b)中的D锁存器寄存器

INT信号在这里也用于清除寄存器的内容。与D触发器不同,D锁存器可以在没有时钟信号的情况下对数据进行“锁存”。当控制信号H为高电平时,锁存器将D端的输入锁存到Q端的输出。但是,如果INT为低电平,则不论控制信号H的状态,寄存器的输出Q都会被强制改变。

在两种情况下,INT信号允许系统在不考虑当前操作周期的情况下快速将寄存器内容重置,这在需要快速清除错误状态或在系统启动时初始化寄存器时非常有用。

这篇关于D触发器(D Flip-Flop)与D锁存器(D Latch)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!