flop专题

手算神经网络MAC和FLOP

在本文中,我们将深入探讨神经网络背景下的 MAC(乘法累加运算)和 FLOP(浮点运算)概念。通过学习如何使用笔和纸手动计算这些内容,你将对各种网络结构的计算复杂性和效率有基本的了解。 这是 colab 笔记本中一个功能齐全的示例。 NSDT工具推荐: Three.js AI纹理开发包 - YOLO合成数据生成器 - GLTF/GLB在线编辑 - 3D模型格式在线转换 - 可编程3D场景

D触发器(D Flip-Flop)与D锁存器(D Latch)

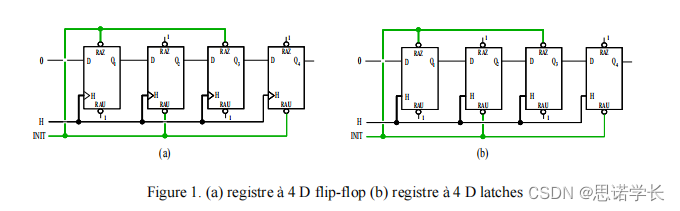

1 基础概念 我们先来简单回顾一下D触发器(D flip-flop)和D锁存器(D latch)的概念,以及它们在数字电路中的作用。 1.1 D触发器(D Flip-Flop) D触发器是一种数字存储器件,它在时钟信号的特定边沿(上升沿或下降沿)上捕获并存储输入信号的状态。因此,它被称为边沿触发设备。 在给定的时钟边沿到来时,如果D输入为高(1)

寄存器 Flip-Flop

组合逻辑是电平输入和电平输出。(组合逻辑虽然符合人的思维习惯,并且元器件结构简单,但问题是如果输入含有毛刺,输出就有毛刺。eg. 如果输入信号突然从0变成1后又在短时间内恢复0,可以视为毛刺,输出信号受到输入信号的影响,也产生了毛刺)时序逻辑就是以时钟作为驱动源的电路。一个触发器,在时钟的驱动下,将D输入端的信号送到Q端输出。时序逻辑上的时钟,一个周期为一拍(1T)。复位信号rst_n解复位,该触