本文主要是介绍FPGA基础:触发器和锁存器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

- 锁存器(Latch)

- D触发器(Flip-Flop)

- 最基本时序电路

- 时序块(Sequential blocks):

- 同步与异步

- 触发器概念

- 触发器分类

- 触发器的Verilog实现

- 1. 上升沿触发的触发器

- 2. 带异步复位、上升沿触发的触发器

- 3. 带异步复位和置位、上升沿触发的触发器

- 4.带异步复位和同步使能、上升沿触发的触发器

- 5.带同步复位、上升沿触发的触发器

锁存器(Latch)

module latch(D, clk, Q);input D, clk;output reg Q;always@(D, clk)if (clk) Q = D;

endmodule

D触发器(Flip-Flop)

module flipflop(D, clk, Q);input D, clk;output reg Q;always@(posedge clk)Q <= D;endmodule

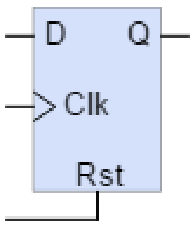

最基本时序电路

On positive edge of clk, Q <= D(在上升沿时被采样)

module dff (

input clk,

input rst,

input D,

output reg Q

alwaysd(posedge clk or posedge rst)beginif(rst==1)0<=0;elseQ<=D;

end

endmodule

时序块(Sequential blocks):

在时钟上升边缘触发(Will trigger at rising edge of clk):always@(posedge(clk))

在时钟下降边缘触发(Triggers at falling edge of clk):always@(negedge(clk))

使用异步复位(Using an asynchronous reset):always@(posedge(clk) or (posedge(rst))

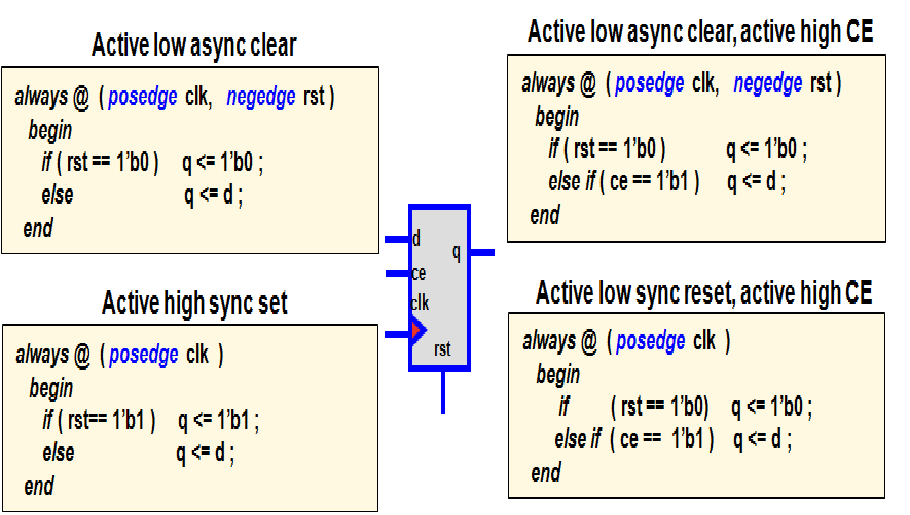

同步与异步

同步控制信号是指该信号有效的时候必须在有时钟边沿到来的情况下才能对电路起作用。异步控制信号是指该信号在任何时刻只要有效,就会对电路起作用,而不必等时钟边沿信号。在verilog HDL中,异步控制信号用关键字posedge和negedge表示是高有效或者低有效。

触发器概念

(1)有两个稳定状态(简称稳态),正好用来表示逻辑 0 和 1。

(2)在输入信号作用下,触发器的两个稳定状态可相互转换(称为状态的翻转)。输入信号消失后,新状态可长期保持下来,因此具有记忆功能,可存储二进制信息。

(3)一个触发器可存储 1 位二进制数码。

(4)触发器有记忆功能,由它构成的电路在某时刻的输出不仅取决于该时刻的输入,还与电路原来状态有关。而门电路无记忆功能,由它构成的电路在某时刻的输出完全取决于该时刻的输入,与电路原来状态无关。

(5)触发器和门电路是构成数字电路的基本单元。

触发器分类

- 上升沿触发的触发器

- 带异步复位、上升沿触发的触发器

- 带异步复位和置位、上升沿触发的触发器

- 带异步复位和同步使能、上升沿触发的触发器

- 带同步复位、上升沿触发的触发器

触发器的Verilog实现

1. 上升沿触发的触发器

module dff(d,clk,q,qn);input d, clk;output q, qn;reg q, qn;always@(posedge clk)begin {q, qn}<={d, ~d};end

endmodule

只列出了上升沿触发的时钟clk,而没有将输入d列写进去,是因为输入d要想起作用,必须要有时钟边沿信号的触发。

2. 带异步复位、上升沿触发的触发器

module dff_asynrst(data,rst,clk,q);input data,rst,clk;output q;reg q;

always@(posedge clk , posedge rst)

begin if(rst==1’b1) q<=1’b0; else q<=data;

end

endmodule

3. 带异步复位和置位、上升沿触发的触发器

module dff_asynrst(data,rst,set,clk,q);input data,rst,set,clk;output reg q;always@(posedge clk , posedge rst , posedge set)begin if(rst==1’b1) q<=1’b0;else if(set==1’b1)q<=1’b1; else q<=data;end

endmodule

4.带异步复位和同步使能、上升沿触发的触发器

module dff_asynrst(data,rst,en,clk,q);input data,rst,en,clk;output q;reg q;

always@(posedge clk , posedge rst) begin if(rst==1’b1) q<=1’b0;else if(en==1’b1)q<=data;

end

endmodule

5.带同步复位、上升沿触发的触发器

module dff_synrst(data,rst,clk,q);input data,rst,clk;output q;reg q;

always@(posedge clk)

begin if(rst==1’b1) q<=1’b0;elseq<=data;

end

endmodule

关注微信公众号获取更多资讯:

这篇关于FPGA基础:触发器和锁存器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!