加法器专题

【计算机组成原理】二、数据的表示和运算:3.算术逻辑单元ALU(逻辑运算、加法器)

4.运算器ALU 文章目录 4.运算器ALU4.1逻辑运算非(NOT)与(AND)或(OR)异或(XOR)同或(XNOR) 4.2加法器4.2.1一位全加器4.2.2串行加法器4.2.3并行加法器 4.3ALU功能与结构 运算器由 算术逻辑单元ALU和若干 通用寄存器(用于暂存操作数和中间结果),如 累加器ACC, 乘商寄存器MQ, 操作数寄存器X, 变址寄存器IX

1074 宇宙无敌加法器(测试点5)

solution 每位权值不同的高精度加法测试点5:结果为0的情况 #include<iostream>#include<string>using namespace std;int main(){string rule, a, b, ans = "";int carry = 0, temp, cnt, power;cin >> rule >> a >> b;for(int i =

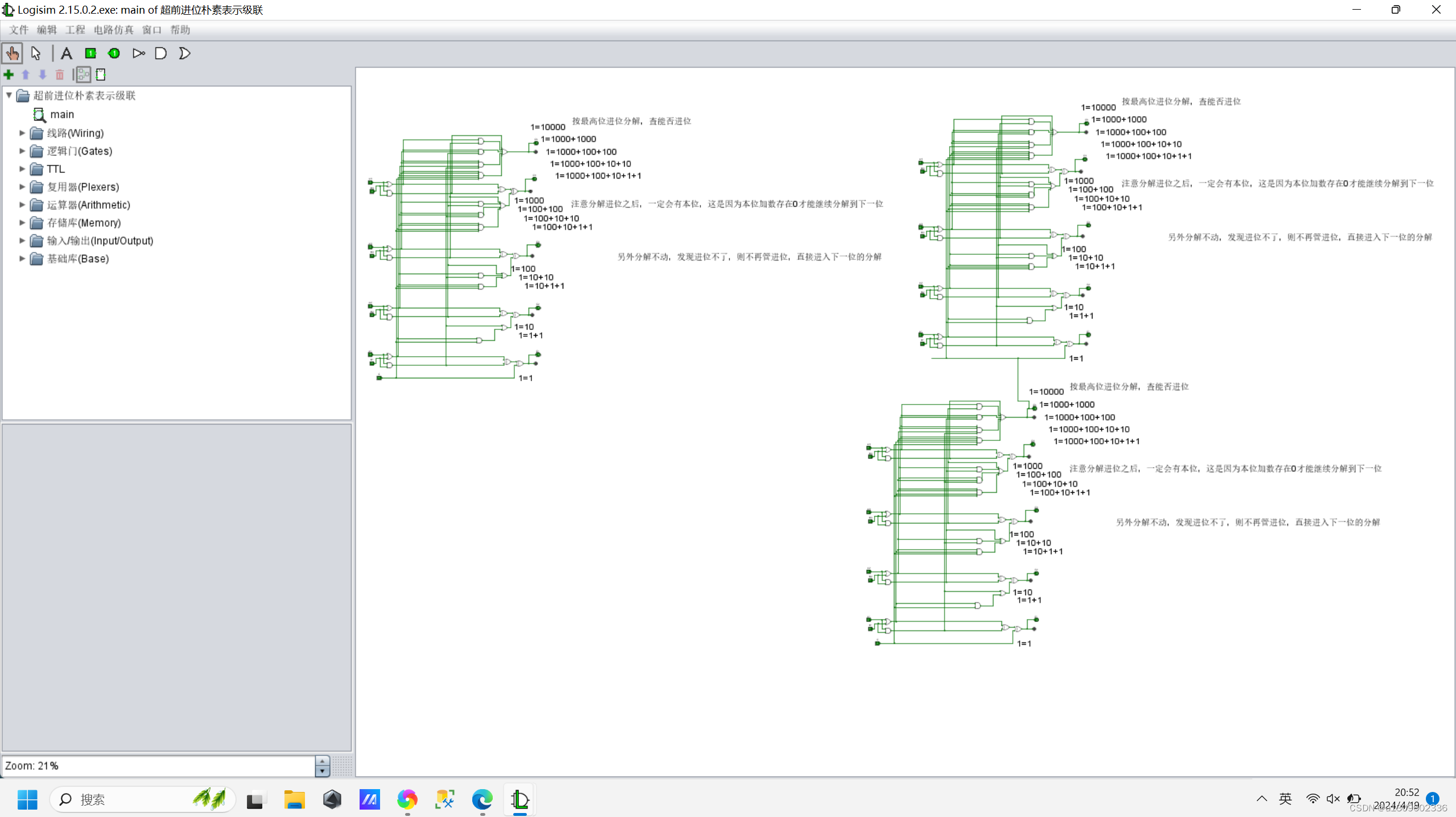

logisim 图解超前进位加法器原理解释

鄙人是视频作者,文件在视频简介的网盘链接。 找规律图解超前进位加法器与原理解释_哔哩哔哩_bilibili 一句话就是“把能导致进位到这个位置的情况全都穷举一遍。” 穷举情况看图中算式。 视频讲解比较啰嗦。

1074 宇宙无敌加法器 (20 分)【有坑,做题时发现,可回顾】

题目概述: 地球人习惯使用十进制数,并且默认一个数字的每一位都是十进制的。而在 PAT 星人开挂的世界里,每个数字的每一位都是不同进制的,这种神奇的数字称为“PAT数”。每个 PAT 星人都必须熟记各位数字的进制表,例如“……0527”就表示最低位是 7 进制数、第 2 位是 2 进制数、第 3 位是 5 进制数、第 4 位是 10 进制数,等等。每一位的进制 d 或者是 0(表示十进制)、或者是

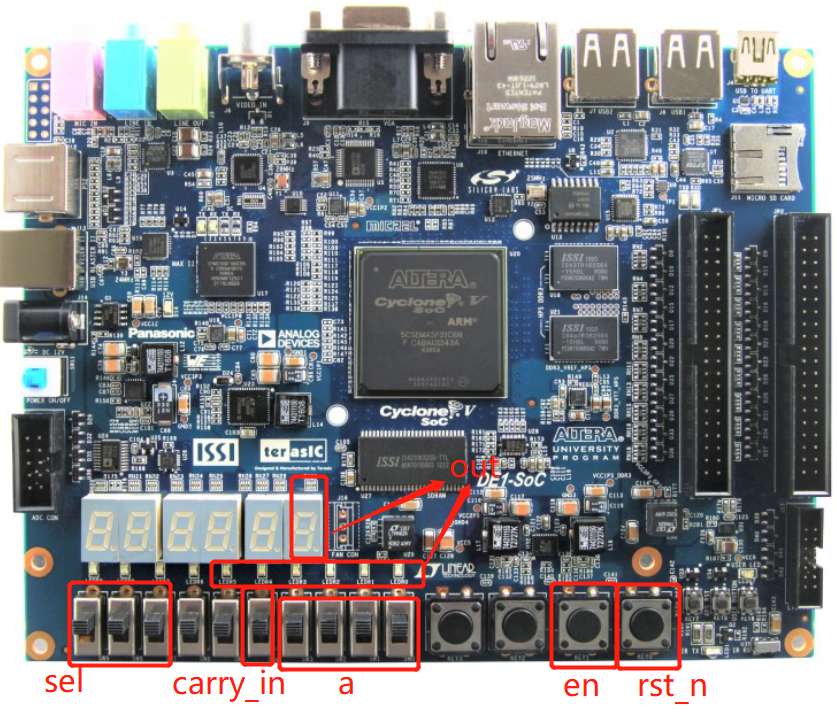

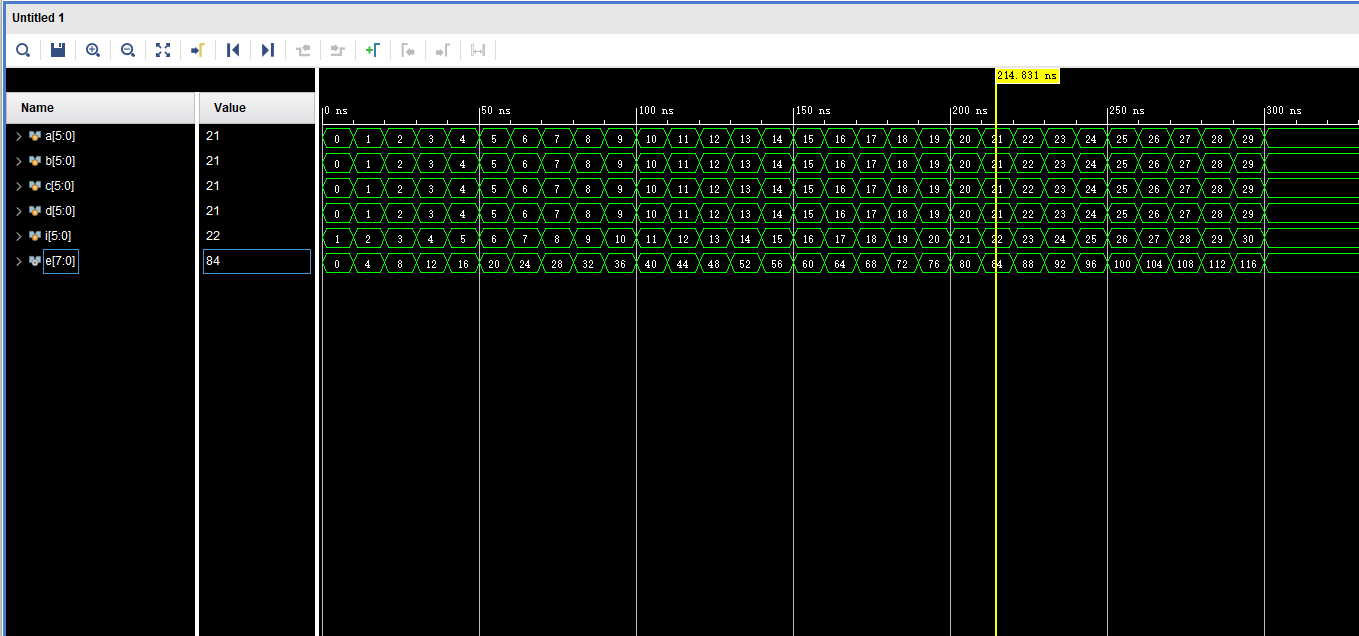

视觉图像处理和FPGA实现第三次作业--实现一个加法器模块

一、adder模块 module adder(ina, inb, outa);input [5:0] ina ;input [5:0] inb ;output [6:0] outa ;assign outa = ina+ inb;endmodule 二、add模块 module add(a,b,c,d,e);input [5:0] a

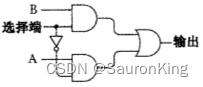

Verilog HDL小练习(一)二路选择器amp;amp;三位加法器

二路选择器是一种及基础的逻辑电路其基本功能描述为,当选择0时输出a,选择1时输出b RTL级描述如下: module muxtwo(out,a,b,sl);input a,b,sl;output out;//============================reg out;always@(sl or a or b)//表示只要有一个变化就执行下面的语句if(!sl)out=

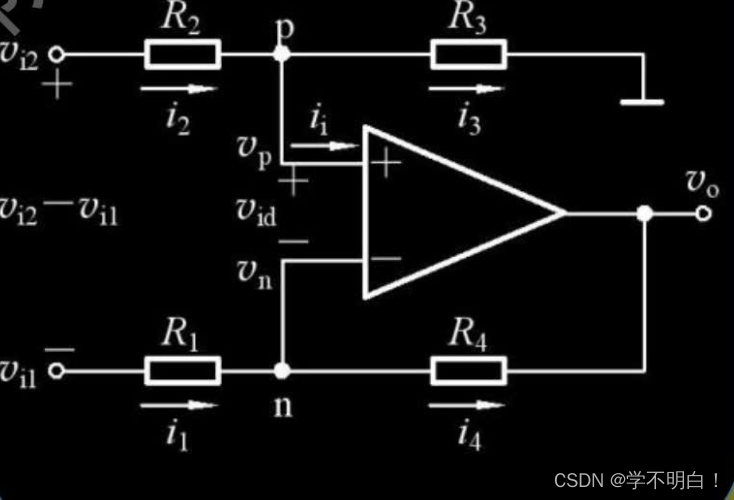

模拟电子技术——同相比例运算放大电路、反向运算比例放大电路、反向加法器电路、差分减法器电路

文章目录 一、同相比例运算放大电路什么是比例运算放大电路线性区与非线性区电压跟随器 二、反向运算比例放大电路什么是反比例运算放大器电路及特点 三、反向加法器电路什么是反向加法器电路及特点及参数计算电路及特点及参数计算 四、差分减法器电路什么是差动减法器 总结 提示:以下是本篇文章正文内容,下面案例可供参考 一、同相比例运算放大电路 什么是比例运算放大电路 基本运算放大器包

用verilog实现加法器

用verilog实现加法器 加法器是组合逻辑电路中的常见器件,了解其结构很有必要。 解决加法问题的根本是解决进位问题,解决进位问题的根本是理解加法竖式。比如计算二进制加法 1001(reg[3:0] in1) + 1101(reg[3:0] in2)。先计算个位in1[0]+in2[0] = 1+1,此时有两个输出,一个是最终结果的末位,应该输出0,这里记录out[0] = 0;还有就是

超前进位加法器(verilog)

文章目录 1.串行进位加法器2.超前进位加法器 加法器单元可以分为全加器和半加器,半加器没有输入进位端,所以半加器时两个比特相加,而全加器时3个比特相加。如下为一个1位半加器, 而一个1位全加器单元的逻辑门数量要比半加器多,: 1.串行进位加法器 多位数相加时,直接描述产生串行进位加法器。代码如下: //3位半加器module(cout,sum,a,b

Modelsim 第一个仿真程序 四位加法器

4位全加器 //4位全加器module a4(sum,cout,a,b,cin);input [3:0] a,b;input cin;output cout;output [3:0] sum;assign {count,sum} = a+b+cin;endmodule 4位全加器的仿真程序 //4位全加器的仿真程序`timescale 1ns/1ns `include "M

c语言实现n位带标志加法器,笔记 | 计算机系统基础:02-逻辑运算电路

零. 课程要点: 了解基础逻辑电路 C语言中的各类运算 判断溢出与数据舍入 如果没学过基础逻辑电路,应该是有专门的一门课《数字逻辑电路》,那门课里有更详细的介绍。因为比较注重逻辑推理,据大学的数电老师说,自从教了这门课,反正他打桥牌就没怎么输过。在计算机系统基础这门课里只是引用一些逻辑部件,更重要的是理解C语言中各类运算是怎么通过电路实现的,由此可能存在怎样的溢出问题,这才是我们学习的重点。 另

天梯赛 宇宙无敌加法器

L1-3 宇宙无敌加法器(20 分) 地球人习惯使用十进制数,并且默认一个数字的每一位都是十进制的。而在 PAT 星人开挂的世界里,每个数字的每一位都是不同进制的,这种神奇的数字称为“PAT数”。每个 PAT 星人都必须熟记各位数字的进制表,例如“……0527”就表示最低位是 7 进制数、第 2 位是 2 进制数、第 3 位是 5 进制数、第 4 位是 10 进制数,等等。每一位的进制

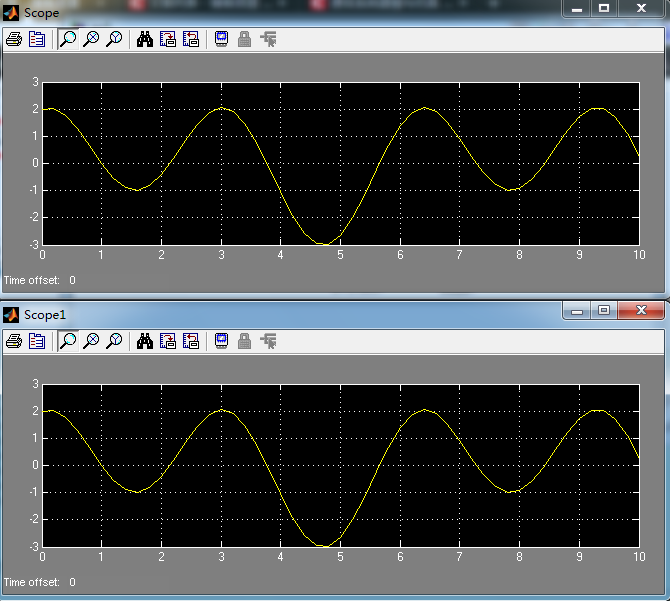

通信系统建模与仿真 笔记4 加法器M文件S函数

编写 加法器M文件S函数 1、启动simulink 2、拖入sine wave 、Add、Scope、S-Functiom、Mux模块 3、按图连接,并保存为ec5.mdl 4、注意把sine wave模块一个设为正弦波,另一个设为余弦波(不会设置看前面的文章http://blog.csdn.net/so_cracy/article/details/64920502) 为了便于显示

并发编程实战14-LongAdder统计加法器-计数器jdk8

传统的原子锁AtomicLong/AtomicInt虽然也可以处理大量并发情况下的计数器,但是由于使用了自旋等待,当存在大量竞争时,会存在大量自旋等待,而导致CPU浪费,而有效计算很少,降低了计算效率。 而LongAdder是根据ConcurrentHashMap这类为并发设计的类的基本原理——锁分段,通过维护一个计数数组cells来保存多个计数副本,每个线程只对自己的副本进行操作,最后汇总来得

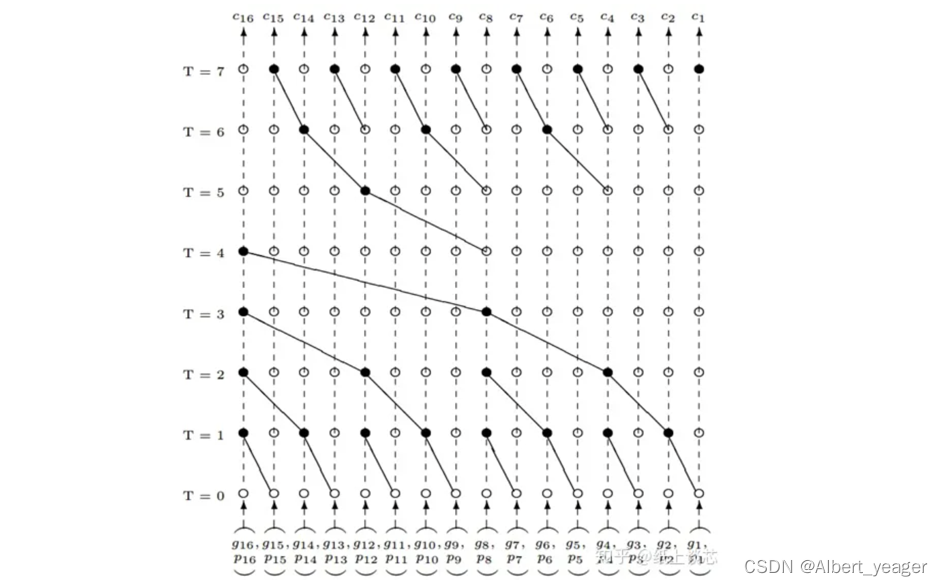

各种加法器的比对分析与Verilog实现(2)

本文将介绍Kogge-Stone加法器和brent-kung加法器的原理,在下一篇博客中我将用Verilog进行实现。 目录 1. 并行前缀加法器(Parallel-Prefix Adder, PPA) 2. Kogge-Stone加法器原理 3. brent-kung加法器原理 1. 并行前缀加法器(Parallel-Prefix Adder, PPA)

各种加法器的比对分析与Verilog实现(3)

上一篇博客介绍了Kogge-Stone加法器和brent-kung加法器,本文将用Verilog代码进行实现。原理部分请看: 各种加法器的比对分析与Verilog实现(2)_Albert_yeager的博客 1. Kogge-Stone加法器的Verilog实现 module koggle_stone (input [3:0] a_i,b_i,input c_i,ou

32位快速加法器设计

32位快速加法器设计 实验目的 帮助学生理解成组进位产生函数,成组进位传递函数的概念,熟悉 Logisim 平台子电路的概念,能利用前述实验封装好的4位先行进位子电路以及4位快速加法器子电路构建16位、32位、64位快速加法器,并能利用相关知识分析对应电路的时间延迟,理解电路并行的概念。 实验内容 利用16位快速加法器以及先行进位电路构建32位快速加法器,并探讨其时间延迟。 可能方案:(1

4位行波加法器vhdl_推动未来雷达技术发展的4大关键技术

人类在掌握电磁波技术的50年以后,发展出了无线电雷达技术,它在第二次世界大战中崭露锋芒,发挥了巨大的作用。 近年来随着微波、计算机、半导体、大规模集成电路等各个领域科学进步,雷达技术在不断发展,其内涵和研究内容都在不断地拓展。雷达功能也由单一功能慢慢演变成多任务、多功能雷达系统。雷达使用的器件也由当初的晶体管发展成GaAs/ GaN/ SiGe的器件。 雷达技术及应用的最新发展趋势 当前面对

C语言【微项目03】—大整数加法器(采用人手算加法过程实现)【2021-10-02】

C语言【微项目03】—大整数加法器(采用人手算加法的过程实现) BigIntadd.c运行结果示例 【TDTX】 【注1】作两正整数相加时,不用输入“+”号;作两负整数相加时,需要都输入“-”号。 【注2】可通过调整字符数组a、b的大小,增大或减小作加法运算的位数。 【注3】使用单链表,采用头插法保存结果的数字。因先是低位作加法,故要在最后输出,则采用头插法。

[Verilog] 加法器(半加法器 | 全加法器 | 串行加法器 | 并行加法器 | 十进制加法器)详解

前言 在数字电路中,加法器是一种常见的逻辑电路,用于将两个数字相加。本文将介绍如何使用Verilog实现各种加法器。 1 加法器种类 整数加法器 半加器(Half Adder):它是最简单的加法器,只能进行两个输入位的相加操作,不包括进位位。全加器(Full Adder):它是最基本的加法器,可以对两个输入位和进位位进行相加,并产生一个输出位和进位输出。多位加法器(Bit Adder):它是

[Verilog] 加法器实现

1. 4位的加法器 先来一个最基本的的Verilog加法器 设计代码 module adder_4bit (input [3:0] a, b, output [3:0] sum, output carry);assign

Modelsim 第一个仿真程序 四位加法器

4位全加器 //4位全加器module a4(sum,cout,a,b,cin);input [3:0] a,b;input cin;output cout;output [3:0] sum;assign {count,sum} = a+b+cin;endmodule 4位全加器的仿真程序 //4位全加器的仿真程序`timescale 1ns/1ns `include "M

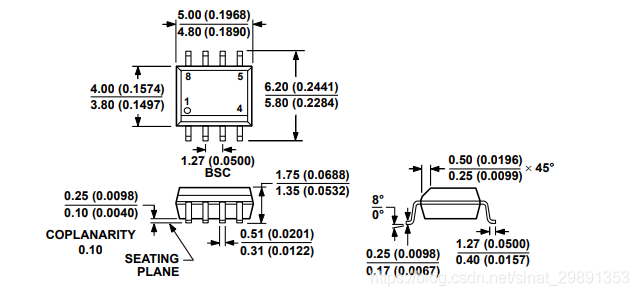

双极性电压测量电路 负电压测量电路 正负电压测量电路 运放OP07运用 加法器 电压跟随器

一、 需求: 1. 测量电压范围-100V~+100V 2. 元器件:越简单越好 3. 精度:待定。 二、设计电路结果: 分压电路+电压跟随器+加法器+分压电路得到0~3.3V间的电压,再通过STM32系列芯片的ADC进行采集 三、测量结果: 分别对-100V, 0V, +100V进行测试如下图: 100V输出2.5V,即100V对应着2.5V 0V输出1.25V,即0

双极性电压测量电路 负电压测量电路 正负电压测量电路 运放OP07运用 加法器 电压跟随器

一、 需求: 1. 测量电压范围-100V~+100V 2. 元器件:越简单越好 3. 精度:待定。 二、设计电路结果: 分压电路+电压跟随器+加法器+分压电路得到0~3.3V间的电压,再通过STM32系列芯片的ADC进行采集 三、测量结果: 分别对-100V, 0V, +100V进行测试如下图: 100V输出2.5V,即100V对应着2.5V 0V输出1.25V,即0

![[Verilog] 加法器(半加法器 | 全加法器 | 串行加法器 | 并行加法器 | 十进制加法器)详解](/front/images/it_default.gif)

![[Verilog] 加法器实现](https://img-blog.csdnimg.cn/direct/5a6e645cba2e49e8a0cdcf1883984cb1.png)