本文主要是介绍视觉图像处理和FPGA实现第三次作业--实现一个加法器模块,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、adder模块

module adder(ina, inb, outa);

input [5:0] ina ;

input [5:0] inb ;

output [6:0] outa ;assign outa = ina+ inb;

endmodule

二、add模块

module add(a,b,c,d,e);

input [5:0] a ;

input [5:0] b ;

input [5:0] c ;

input [5:0] d ;

output [7:0] e ;

wire [6:0] outa1,outa2 ;assign e = outa1 + outa2;adder adder1

(.ina ( a ) ,.inb ( b ) ,.outa ( outa1 )

);

adder adder2

(.ina ( c ) ,.inb ( d ) ,.outa ( outa2 )

);endmodule

三、testbench

`timescale 1ns / 1ps

module add_tb();

reg [5:0] a ;

reg [5:0] b ;

reg [5:0] c ;

reg [5:0] d ;

wire [7:0] e ;

reg [5:0] i ;add u_add(.a ( a ),.b ( b ),.c ( c ),.d ( d ),.e ( e )

);initial begina=0; b=0; c=0; d=0;for(i=1; i<31; i= i+1)begin#10;a=i; b=i; c=i; d=i;end

endinitial begin$monitor($time,,,"%d+ %d+ %d+ %d= {%d}", a, b, c, d, e);#500 $finish;

endendmodule

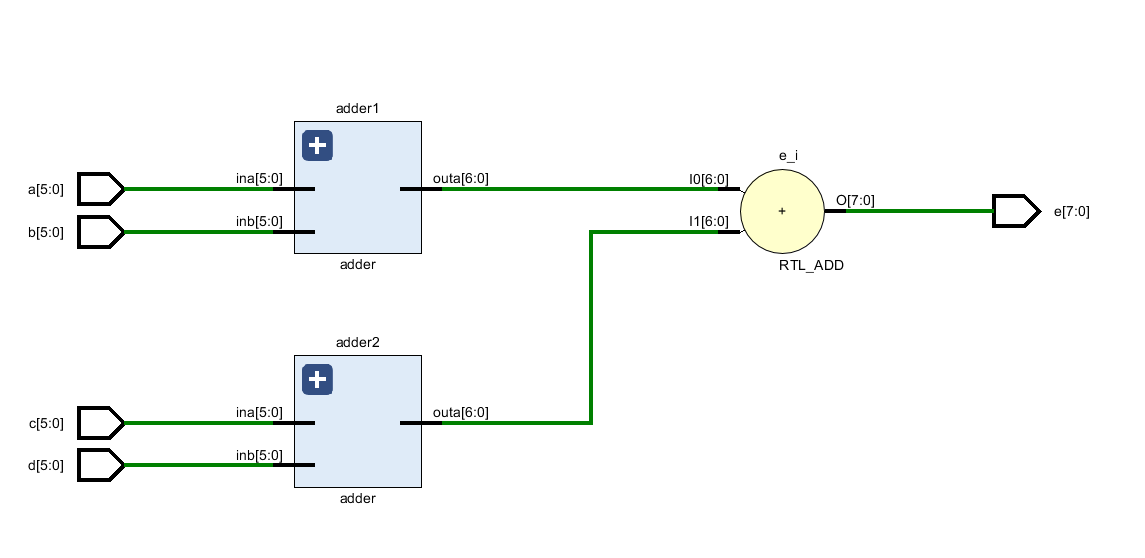

四、RTL图

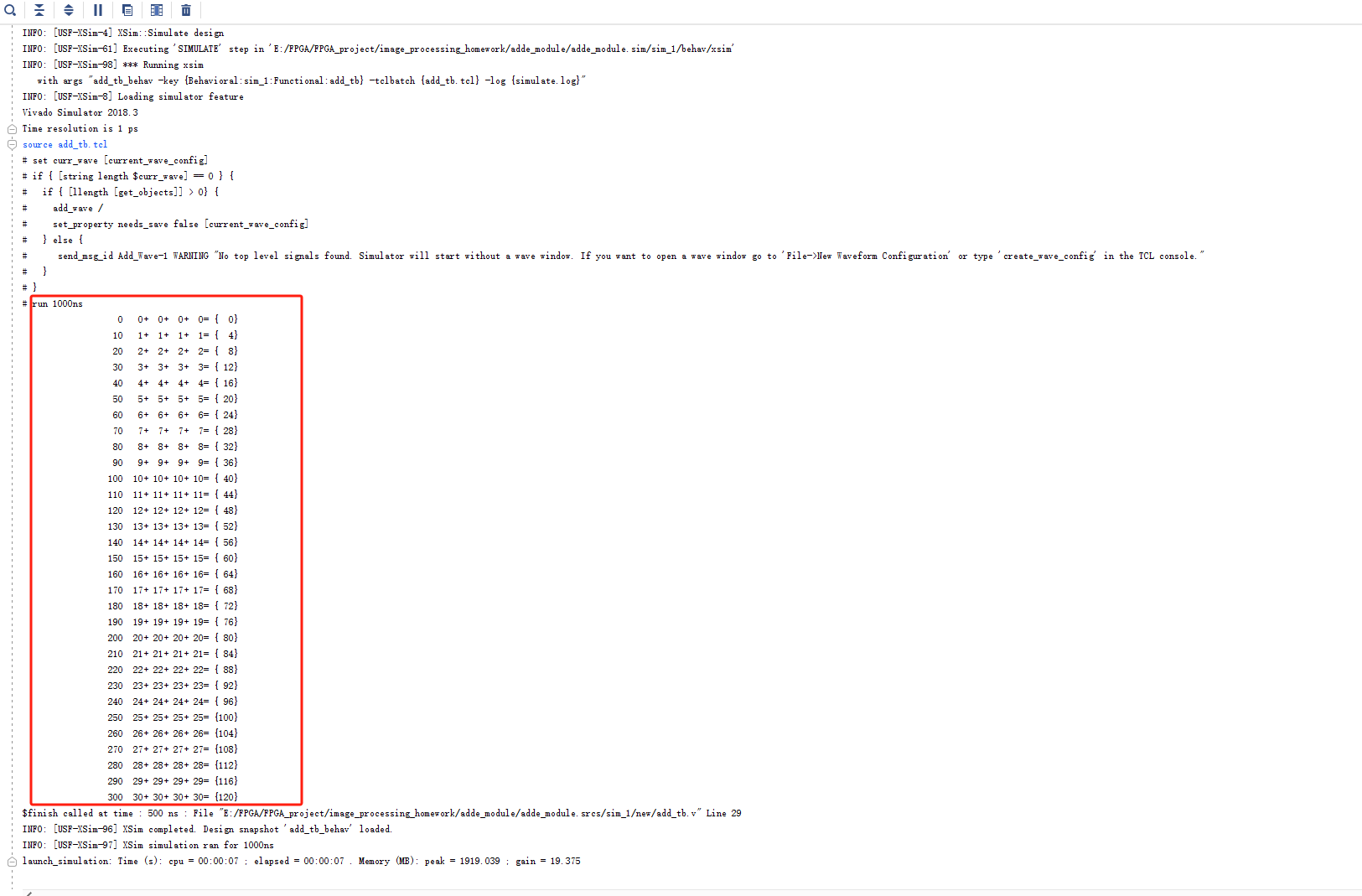

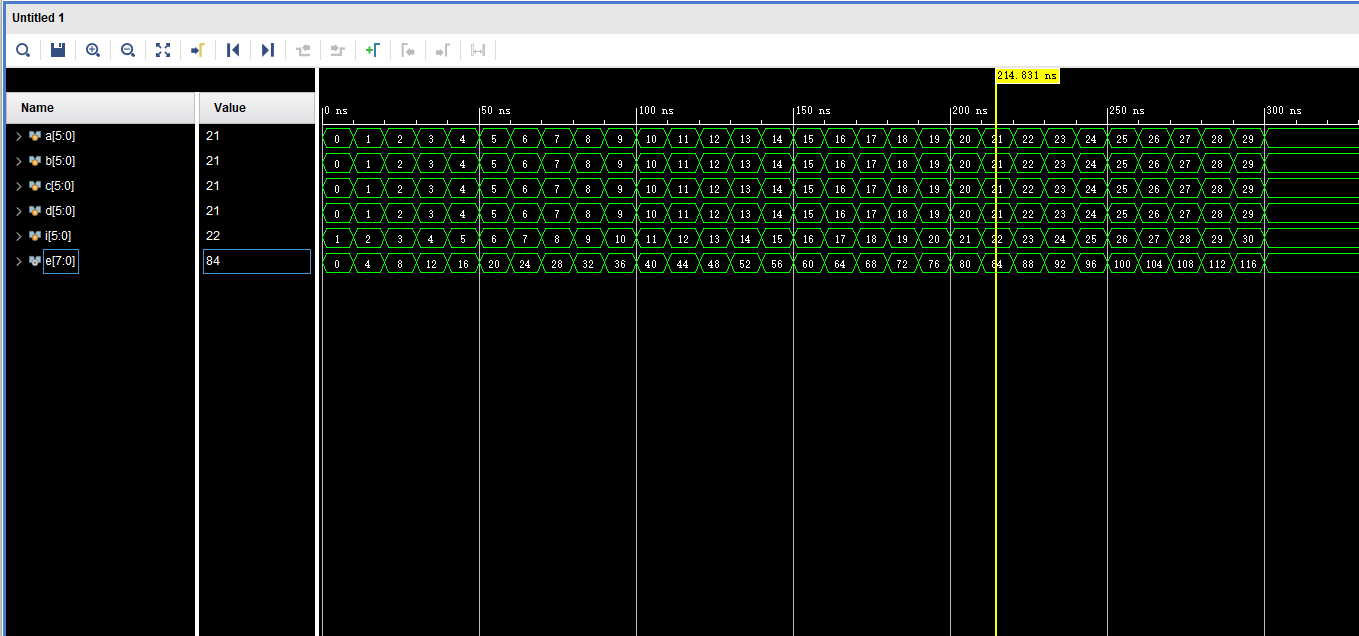

五、仿真

这篇关于视觉图像处理和FPGA实现第三次作业--实现一个加法器模块的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!