乘法器专题

关于FPGA设计16位乘法器的两…

原文地址:关于FPGA设计16位乘法器的两种算法 作者:ChrisChan 部分原代码如下: 用特权的右移算法虽复杂点,但节省不少LEs,如下图: 用左移算法尽管浅显易懂,但因每次都会从最右端移位,会占用更大面积,速度暂不说,如下图:

FPGA通过移位相加实现无符号乘法器(参数化,封装成IP可直接调用)

目录 1.前言2.原理3.移位无符号乘法器实现,并参数化 微信公众号获取更多FPGA相关源码: 1.前言 在硬件设计中,乘法器是非常重要的一个器件,乘法器的种类繁多,常见的有并行乘法器、移位相加乘法器和查找表乘法器。 并行乘法器的实现非常简单,在Verilog中只需要通过 * 实现,若要进行有符号的乘法,需使用 系统函数$signed。 查找表乘法器实际上是先将乘法的计算

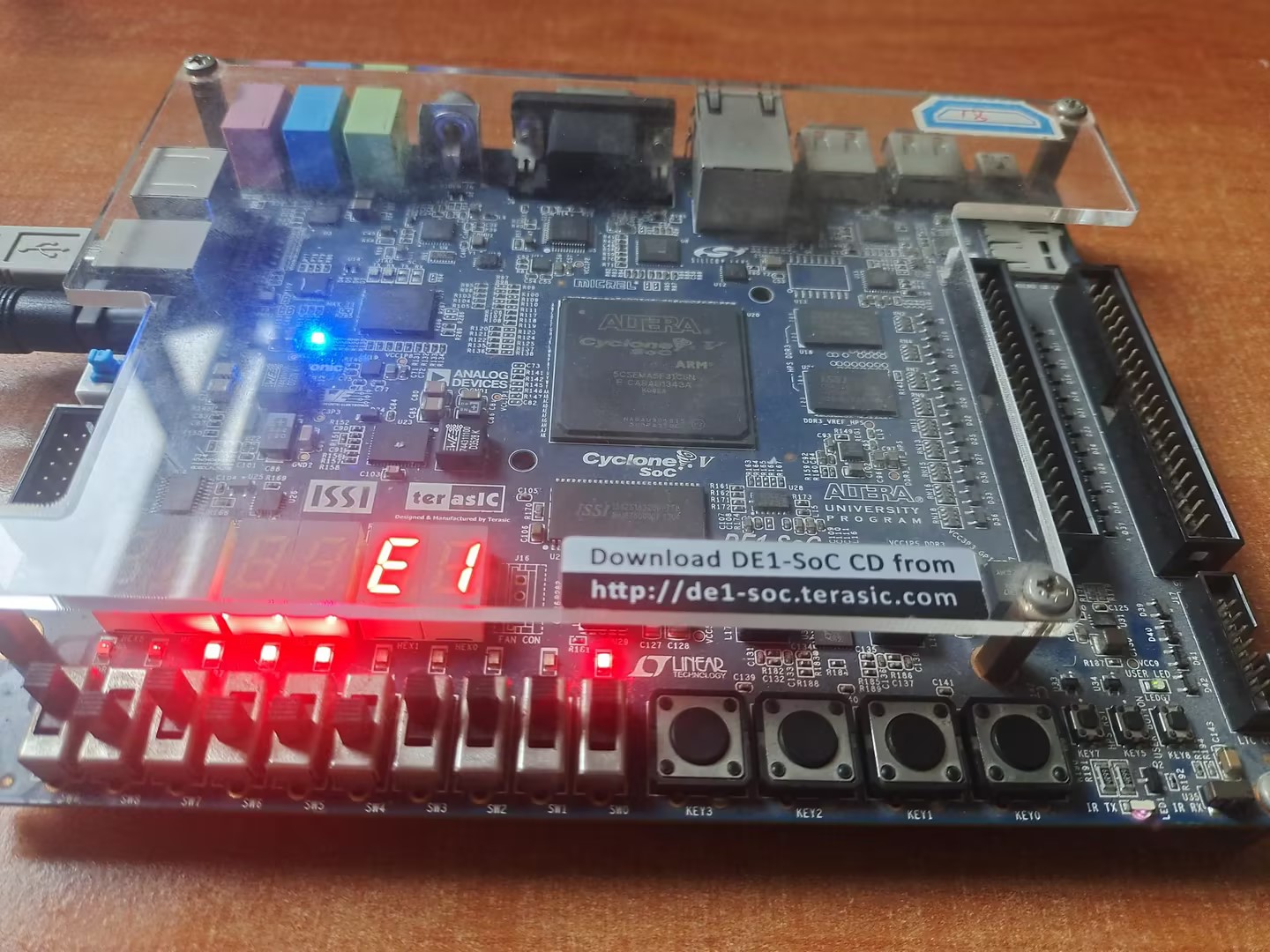

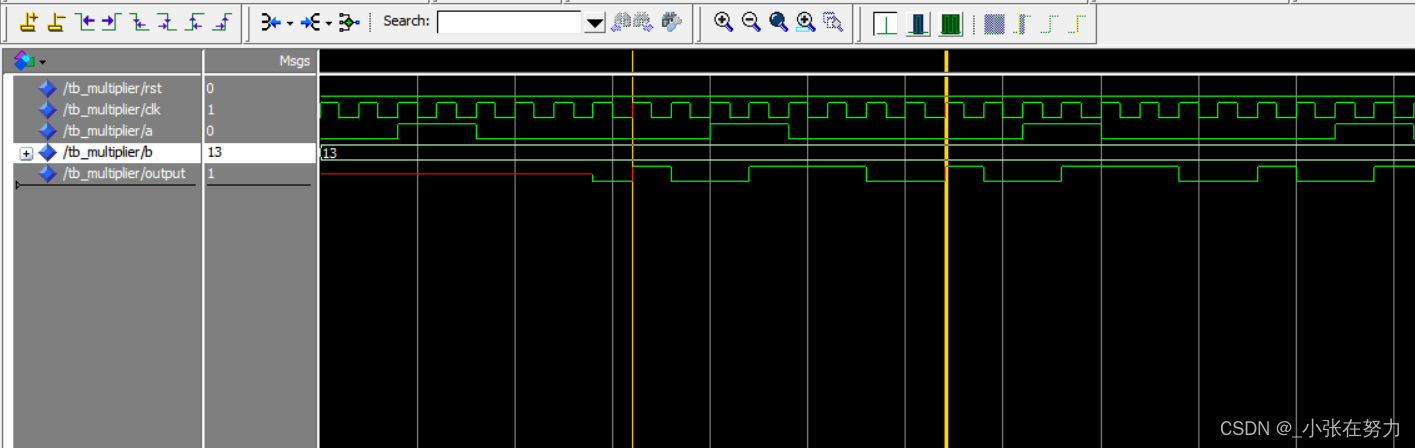

使用FPGA实现串-并型乘法器

介绍 其实我们知道,用FPGA实现乘法器并不是一件很简单的事,而且在FPGA中也有乘法器的IP核可以直接调用,我这里完全就是为了熟悉一些FPGA的语法然后写了这样一个电路。 串-并型乘法器模块 从字面上看,串-并乘法器就是其中一个乘数是串行的,另一位乘数是并行的。我在这里只描述一下模块的输入输出端口,相比于并行乘法器,串-并型乘法器占用的资源更少。 在这里,a是串行的数据,b是并行

CY2300相位对齐时钟乘法器

这份文件是关于Cypress Semiconductor Corporation生产的CY2300型号的Phase-Aligned Clock Multiplier(相位对齐时钟乘法器)的技术手册。以下是该文件的核心内容概述: 产品特性: 4倍频输出配置。单一锁相环(PLL)架构。相位对齐功能。低抖动、高准确度输出。输出使能引脚。支持3.3V操作电压。5V容忍度输入。内部环路滤波器。8引脚15

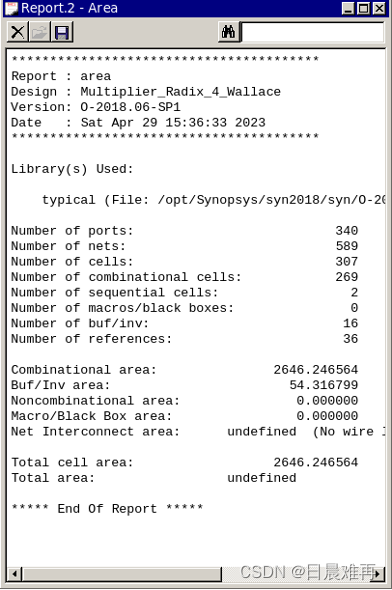

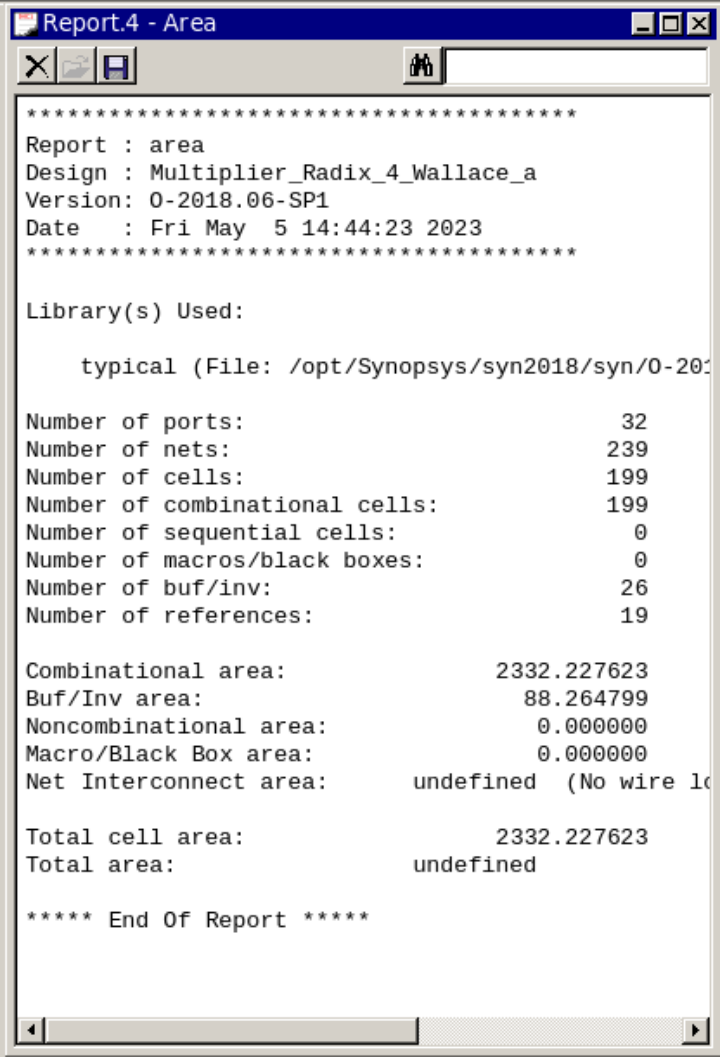

数字IC前端学习笔记:数字乘法器的优化设计(基4布斯编码华莱士树乘法器)

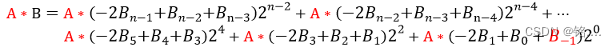

相关阅读 数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482 使用基2布斯乘法器虽然能减少乘数中0的数量,但最终还是无法减少部分积的数量,因此一种更合理的编码方式产生了——基4布斯编码。它可以将部分积的数量减少一半,本文中还会使用华莱士树结构对部

verilog编程之乘法器的实现

知识储备 首先来回顾一下乘法是如何在计算机中实现的。 假设现在有两个32位带符号定点整数x和y,我们现在要让x和y相乘,然后把乘积存放在z中,大家知道,两个32位数相乘,结果不会超过64位,因此z的长度应该为64位。 z = x * y中,x是被乘数,在Verilog代码中 multiplicand表示,y是乘数,在代码中用multiplier表示。因为x和y都是带符号数,所以应该是用补码乘法

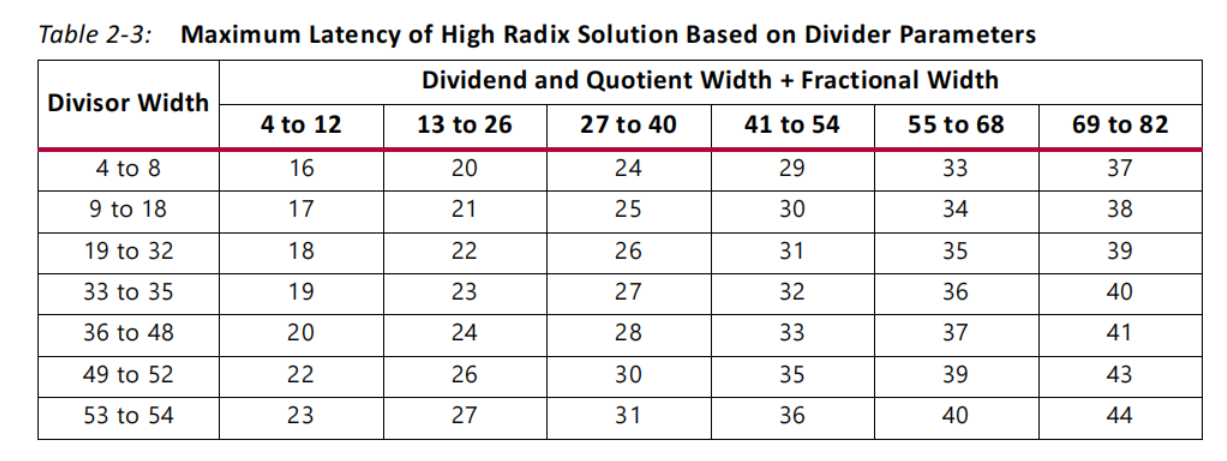

图像处理算法:白平衡、除法器、乘法器~笔记

参考: 基于FPGA的自动白平衡算法的实现 白平衡初探 (qq.com) FPGA自动白平衡实现步骤详解-CSDN博客 xilinx 除法ip核(divider) 不同模式结果和资源对比(VHDL&ISE)_ise除法器ip核-CSDN博客 数字信号处理-04- FPGA常用运算模块-除法器(二)-阿里云开发者社区 (aliyun.com) 【F

chisel入门初步1——基4的booth编码的单周期有符号乘法器实现

基4的booth编码乘法器原理说明 基2的booth编码 本质来说就是一个裂项重组,乘法器最重要的设计是改变部分积的数量,另外在考虑有符号数的情况下,最高位符号位有特别的意义。 (注:部分积是指需要最后一起加和的所有部分乘积的项) 下面直接套用其他人图片进行展示,来源如下 https://blog.csdn.net/weixin_42330305/article/details/1228682

IAR开发stm8系列,C语言实现16位乘法器和32位除法器函数

stm8是8位单片机,在ADC采样采用12bit采样值进行定点整型运算的时候,为了保证精度需要通过16位乘法器 进行扩大,通过32位除法器缩小运算。但是用c语言直接用“*"和"/"计算是无法实现。c语言的math函数库也没有提供这样的计算函数,只好自己编写了一段。开始想用c语言嵌套汇编的方式来做,但是发现调试通过的函数,放到大程序中执行总是计算错误,只好放弃,完全用c语言来实现,过程有点复杂,这里

11.7加减计数器,可置位~,数字钟分秒,串转并,串累加转并,24位串并128,流水乘法器,一些乘法器

信号发生器 方波,就是一段时间内都输出相同的信号 锯齿波就是递增 三角波就是先增后减 加减计数器 当mode为1则加,Mode为0则减;只要为0就输出zero 这样会出问题,因为要求是十进制,但是这里并没有考虑到9之后怎么办,所以就会使number输出超过9,应该额外要添加十进制的边缘判断,即mode为1,要加的时候也要判断一下是不是要继续加,而不是直接加

数字IC前端学习笔记:优化的基4布斯编码华莱士树乘法器

相关阅读 数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html 本文是对前文设计的乘法器,即基4布斯编码华莱士树乘法器的补充和优化,具体关于基4布斯编码和华莱士树的内容可以从以往的文章中获得。 数字IC前端学习笔记:数字乘法器的优化设计(基4布斯编码华莱士树乘法器)https://bl

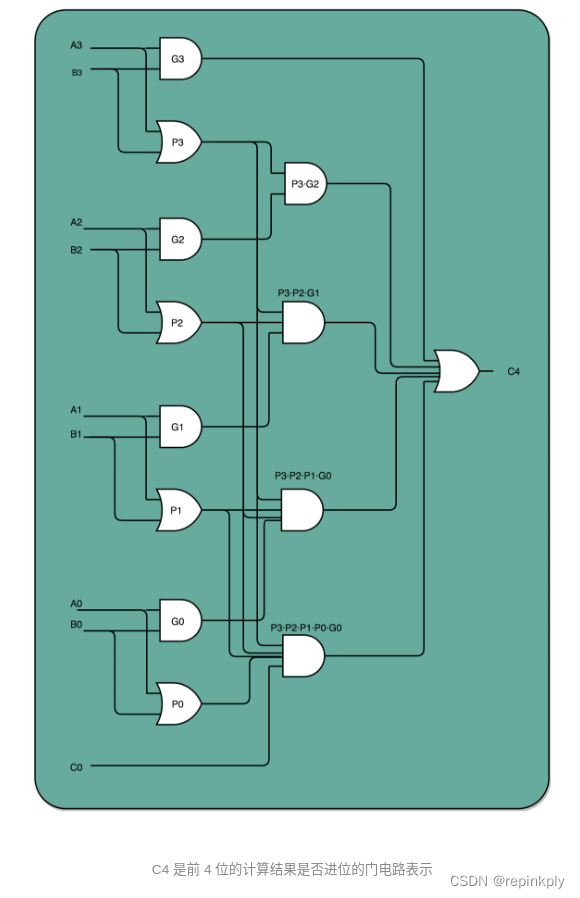

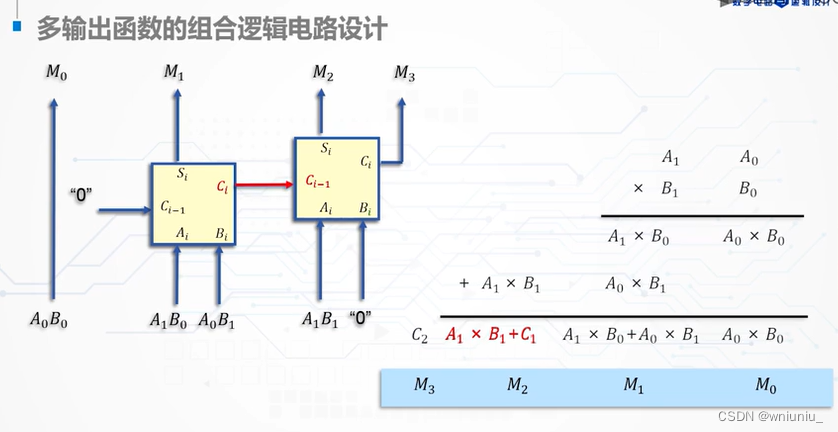

乘法器:如何像搭乐高一样搭电路(下)?

目录 背景 顺序乘法的实现过程 并行加速方法 电路并行 小结 背景 和学习小学数学一样,学完了加法之后,我们自然而然就要来学习乘法。既然是退回到小学,我们就把问题搞得简单一点,先来看两个 4 位数的乘法。这里的 4 位数,当然还是一个二进制数。我们是人类而不是电路,自然还是用列竖式的方式来进行计算。 十进制中的 13 乘以 9,计算的结果应该是 117。我们通过转换成二

【【二进制 无符号乘 有符号 乘法器 的设计verilog代码+testbench 】】

二进制 无符号乘 有符号 乘法器 的设计verilog代码+testbench usmultiplier.v module usmultiplier #(parameter NUMBER1 = 8 ,parameter NUMBER2 = 8 )(input [NUMBER1-1 : 0]

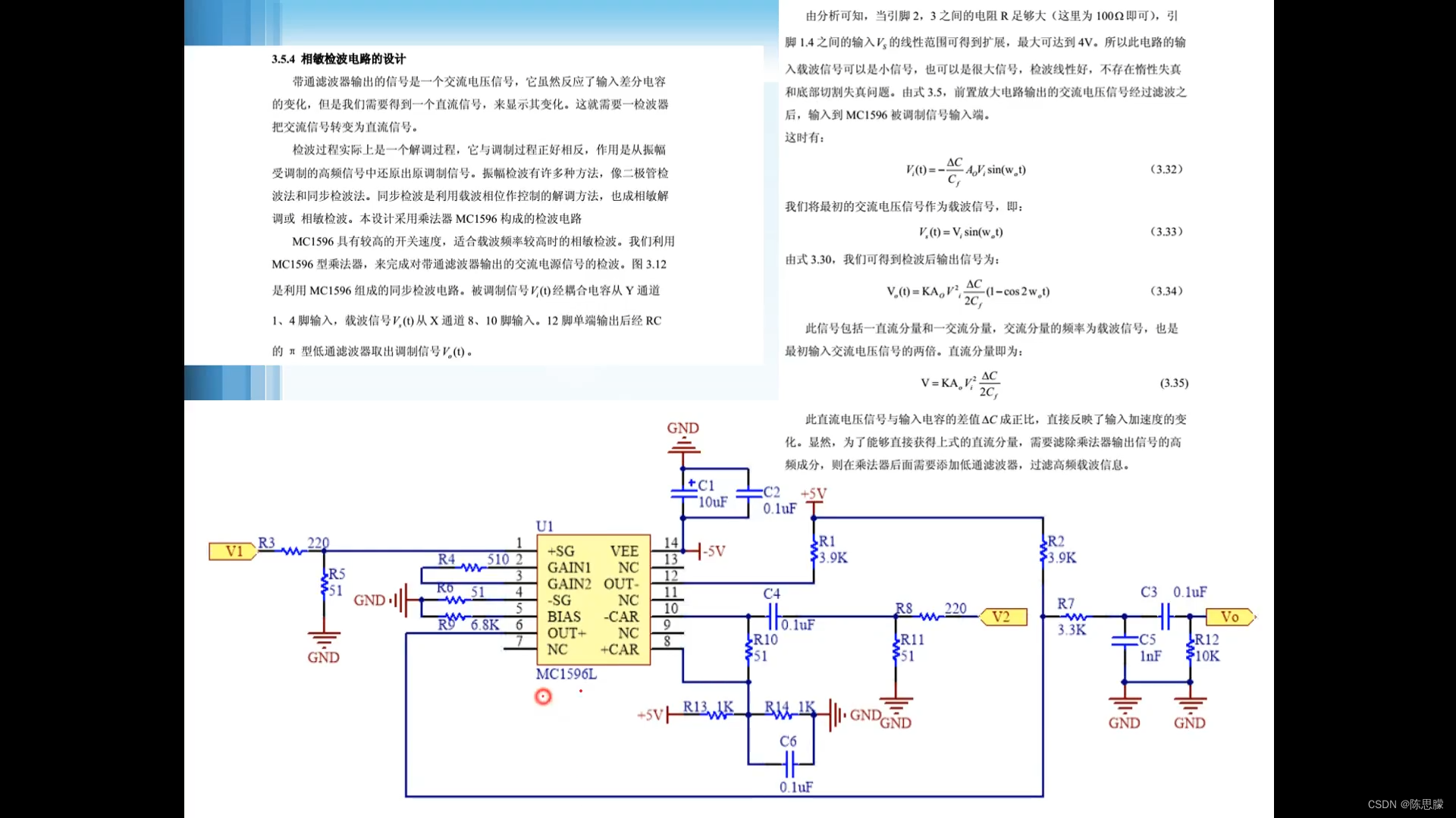

AGC电路,模拟乘法器

文章目录 AGC电路乘法器 AGC电路 注:下面三个没试过 乘法器 TI只有这一种乘法器,跟ADI的AD534一模一样 这个报告里有很多错误 做乘法器最厉害的是ADI

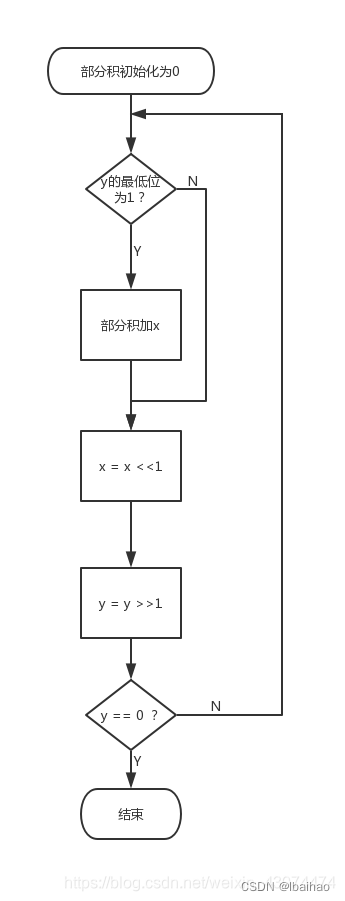

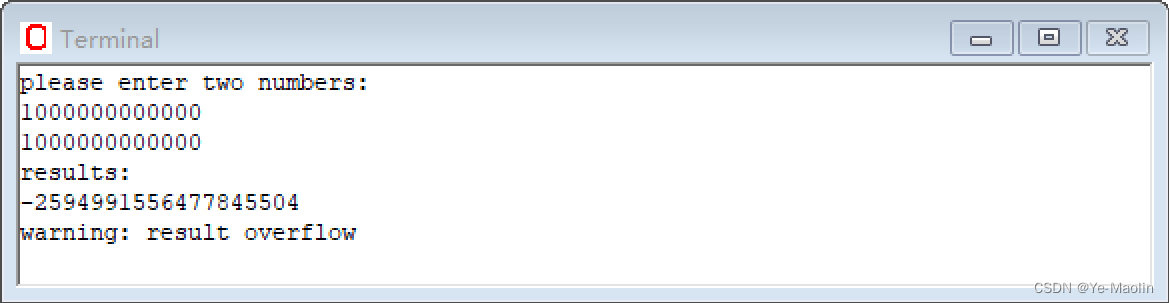

MIPS64乘法器模拟实验

目录 忽略溢出的乘法器 溢出提示的乘法器 忽略溢出的乘法器 首先,我们得了解乘法器如何由加法器设计得到,此处,我们以32位乘法为例。 总共分为4步: 1. 测试乘数最低位是否为1,是则给乘积加上被乘数,将结果写入乘积寄存器; 2. 被乘数寄存器左移1位; 3. 乘数寄存器右移一位; 4. 判断是否循环了32次,如果是,则结束,否则返回步骤1

MIPS64乘法器模拟实验

目录 忽略溢出的乘法器 溢出提示的乘法器 忽略溢出的乘法器 首先,我们得了解乘法器如何由加法器设计得到,此处,我们以32位乘法为例。 总共分为4步: 1. 测试乘数最低位是否为1,是则给乘积加上被乘数,将结果写入乘积寄存器; 2. 被乘数寄存器左移1位; 3. 乘数寄存器右移一位; 4. 判断是否循环了32次,如果是,则结束,否则返回步骤1

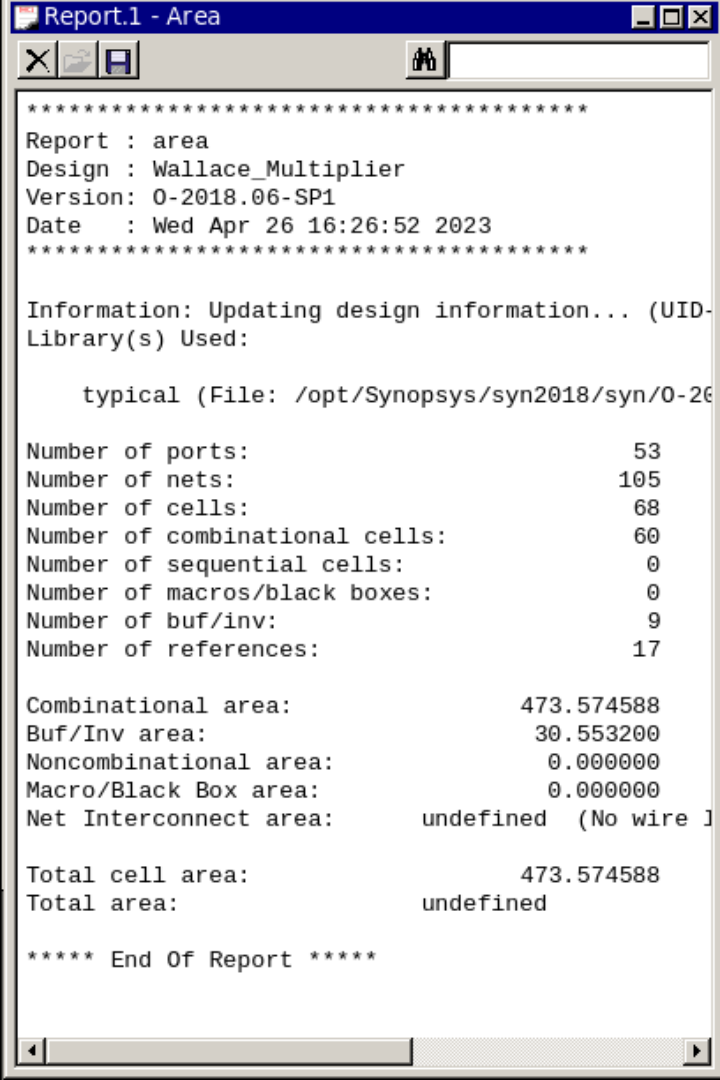

数字IC前端学习笔记:数字乘法器的优化设计(Wallace Tree乘法器)

相关阅读 数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482 进位保留乘法器依旧保留着阵列的排列规则,只是进位是沿斜下角,如果能使用树形结构来规划这些进位保留加法器,就能获得更短的关键路径延迟和更小的器件开销,这种结构的乘法器被称为华莱士树(Wa

数字IC前端学习笔记:数字乘法器的优化设计(Dadda Tree乘法器)

相关阅读 数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482 华莱士树仍然是一种比较规则的结构(这使得可以方便地生成树的结构),这导致了它所使用的全加器和半加器个数不是最少的,Dadda提出了一种改良华莱士树的方式,这后来被称为Dadda Tr