testbench专题

在使用VScode自动生成verilog testbench文件时,提示No module named 'chardet'

https://www.cnblogs.com/whylinux/p/9839162.html 解决方法为: pip install certifi pip install chardet pip install idna pip install urllib3

【乌拉喵.教程】编写TestBench,quartus与modelsim时序仿真

最近将多年来收集到的教学视频、国内外图书、源码等整理整合拿出来,涉及arm、Linux、python、信号完整性、FPGA、DSP、算法、stm32、单片机、制图、电子模块、kali、出版社图书等。资料目前约1.5TB+。详情请见: https://www.bilibili.com/read/cv20701606 昨天搜了一圈,也没整会这个仿真,今天在武梦梦的指导下修改了testbench,

testbench tb仿真

Verilog功能模块HDL设计完成后,并不代表设计工作的结束,还需要对设计进行进一步的仿真验证。掌握验证的方法,即如何调试自己的程序非常重要。在RTL逻辑设计中,要学会根据硬件逻辑来写测试程序即写Testbench。Verilog测试平台是一个例化的待测(MUT)模块,重要的是给它施加激励并观测其输出。逻辑块与其对应的测试平台共同组成仿真模型,应用这个模型就可以测试该模块能否符合自己的设计要求。

testbench仿真文件编写规则

编写TESTBENCH的目的是为了对使用硬件描述语言设计的电路进行仿真验证,测试设计电路的功能、性能与设计的预期是否相符。编写测试文件的过程如下: (1)产生模拟激励(波形); (2) 将产生的激励加入到被测试模块中并观察其响应; (3) 将输出响应与期望值相比较。 一,各部分写法 1,testbench文件结构 module Test_bench();//通常无输入无输出信号或变量声明定

如何写一个仿真文件——testbench

欲观原文,请君移步微信 testbench作用是什么? testbench就是对写的FPGA文件进行测试的文件。任何设计都是有输入输出的,testbench的作用就是给这个设计输入,然后观察输出是否符合我们的预期,这就是testbench的功能。运行环境一般是ise或者vivado自带的仿真工具,或者如modelsim一样的第三方仿真工具。 如下图所示,仿真模型就好比是"一道菜"(Verilo

testbench测试大批量数据

源代码: module example_1(input clk,input [7:0] a_in,output [7:0] b_out);reg [7:0]b_out;reg [7:0]c;always @(posedge clk)beginc<=a_in;b_out<=c; endendmodule 激励文件: module example_1tb();reg clk;reg [7:0

Verilog基础:在testbench中使用阻塞赋值和非阻塞赋值的区别

相关阅读 Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482 本文详细阐述了在一个testbench中,应该如何使用阻塞赋值与非阻塞赋值。首先说结论,建议在testbench中,对时钟信号(包括分频时钟)使用阻塞赋值,对其他同步信号使用非阻

使用verilog写一个模拟比特币挖矿游戏及testbench

设计模拟比特币挖矿游戏需要考虑到以下几个方面: 游戏目标和规则: 确定游戏的目标,例如挖取尽可能多的比特币或达到一定的挖矿目标。确定游戏的规则,例如通过计算难题来进行挖矿、使用特定的硬件设备等。 确定状态及状态转移条件: 确定游戏中可能存在的状态,如等待开始、准备解析难题、解析难题中、成功挖矿等。确定不同状态之间的转移条件,例如何时从等待开始状态转移到准备解析难题状态,如何判断难题是否解析成

使用verilog实现井字棋游戏设计及其testbench

井字棋是一种经典的二人策略棋类游戏,也被称为Tic-Tac-Toe。游戏通常在一个3x3的方格棋盘上进行,每名玩家轮流在空格中放置自己的标记,一般玩家1使用"X"标记,玩家2使用"O"标记,直到有一名玩家在水平、垂直或对角线上连成三个自己的标记为止。 井字棋的规则非常简单: 游戏开始时,棋盘为空,交替玩家轮流落子。每次落子,玩家可以选择一个未被占据的空格放置自己的标记。玩家目标是通过在水平、垂

基于HSV色度空间的图像深度信息提取算法FPGA实现,包含testbench和MATLAB辅助验证程序

目录 1.算法运行效果图预览 编辑2.算法运行软件版本 3.部分核心程序 4.算法理论概述 5.算法完整程序工程 1.算法运行效果图预览 将FPGA结果导入到matlab显示结果如下: matlab的对比测试结果如下: 2.算法运行软件版本 vivado2019.2 matlab2022a 3.部分核心程序 `timescale 1ns / 1ps//

认识Testbench仿真激励

一、认识Testbench Bench有平台之意,所以Testbench就是测试平台的意思。 任何一个被测模块,都有输入和输出,此模块是否合格的判断依据,就是在满足输入要求的情况下,能否得到符合预期的输出。我们把被测模块称作UUT(Unit Under Test)。 Vivado提供了Simulator(仿真)功能,用户可以通过编写仿真文件,根据UUT

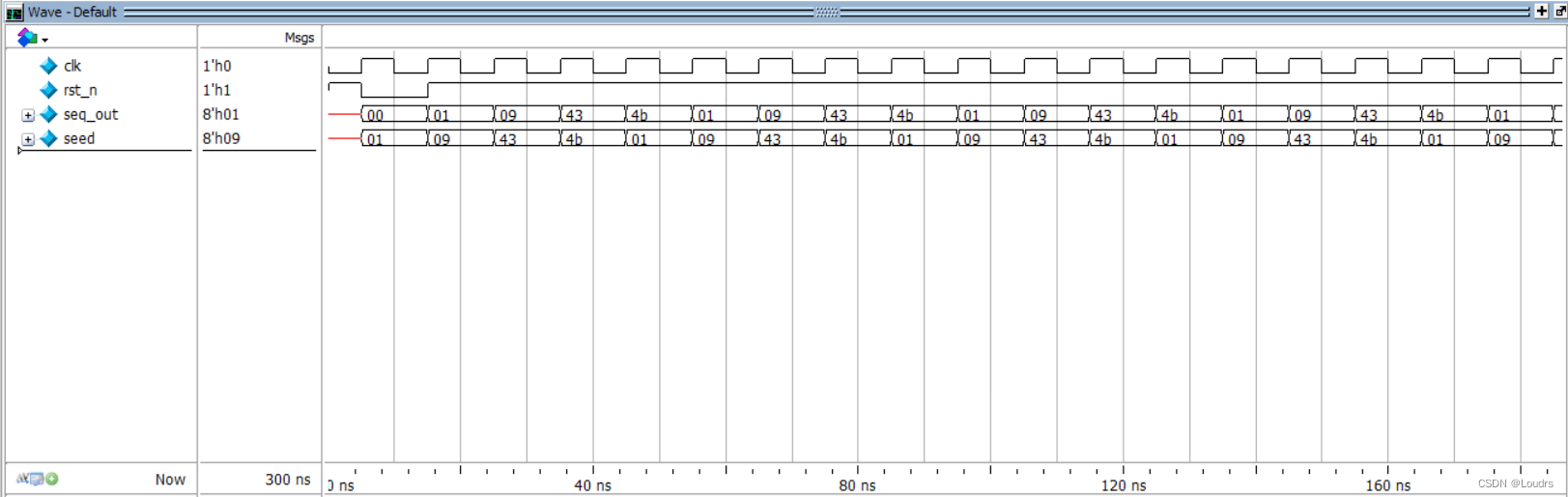

序列发生器(两类序列、三种设计方法和两种发生模式|verilog代码|Testbench|仿真结果)

序列发生器 一、前言二、状态机法、寄存器法和计数器法2.1 状态机法2.1.1使用状态机生成序列10012.1.2 Verilog代码2.1.3 Tsetbench2.1.4 仿真结果 2.2移位寄存器法2.2.1使用移位寄存器生成序列10012.2.2 Verilog代码2.2.3 Tsetbench2.2.4 仿真结果 2.3计数器法2.3.1 使用计数器生成序列10012.3.2 Ve

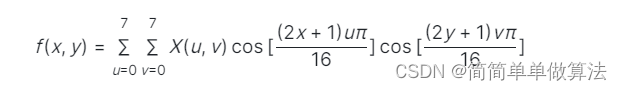

基于FPGA的二维DCT变换和逆变换verilog实现,包含testbench

目录 1.算法运行效果图预览 2.算法运行软件版本 3.部分核心程序 4.算法理论概述 5.算法完整程序工程 1.算法运行效果图预览 数据导入到matlab显示图像 2.算法运行软件版本 vivado2019.2 matlab2022a 3.部分核心程序 `timescale 1ns / 1ps//// Company: // Engineer: /

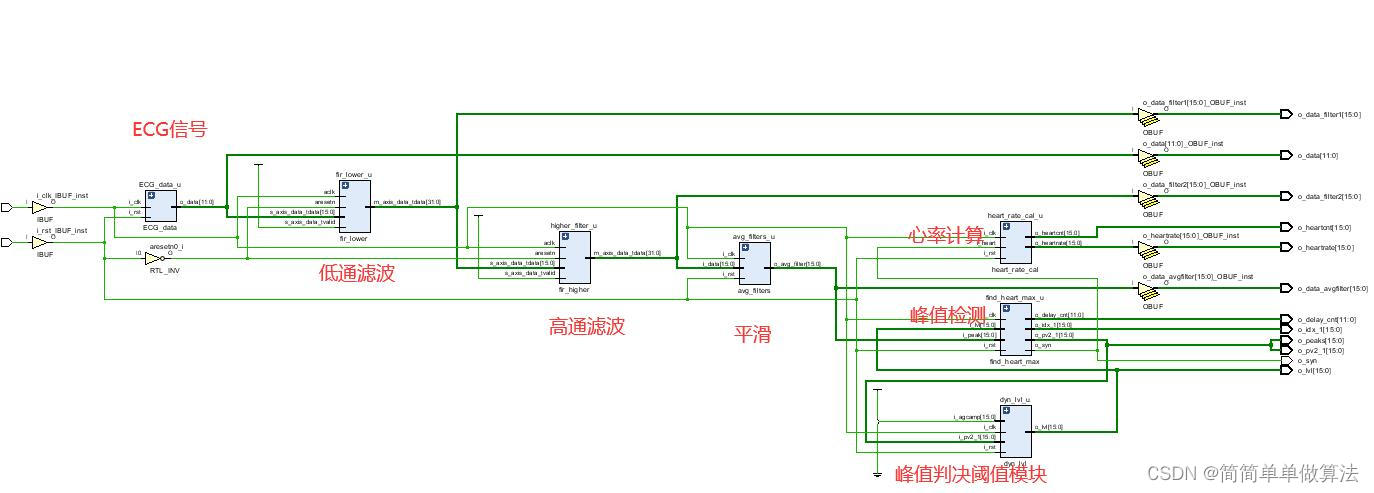

基于FPGA的ECG信号滤波与心率计算verilog实现,包含testbench

目录 1.算法运行效果图预览 2.算法运行软件版本 3.部分核心程序 4.算法理论概述 4.1 ECG信号的特点与噪声 4.2 FPGA在ECG信号处理中的应用 4.3 ECG信号滤波原理 4.4 心率计算原理 4.5 FPGA在ECG信号处理中的优势 5.算法完整程序工程 1.算法运行效果图预览 其RTL结构如下: 2.算法运行软件版本 vivado2

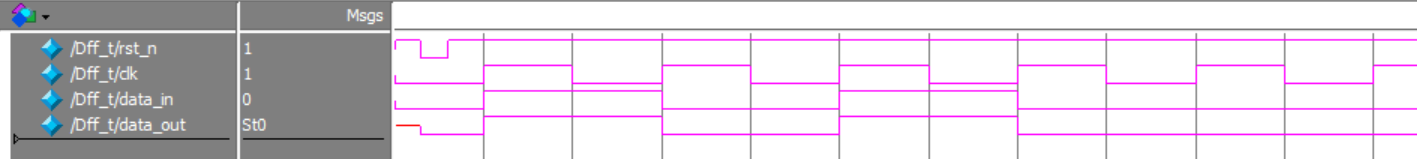

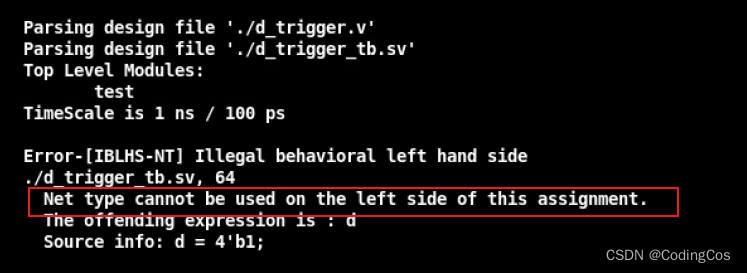

【芯片设计- RTL 数字逻辑设计入门 6 -- 带同步复位的D触发器 RTL实现及testbench 验证】

文章目录 带同步复位的D触发器Verilog 代码testbench 代码编译及仿真问题小结 带同步复位的D触发器 同步复位 :复位只能发生在在clk信号的上升沿,若clk信号出现问题,则无法进行复位。 Verilog 代码 // timescale ins/1nsmodule flopr (input rstn,input clk,input[3:0] d,

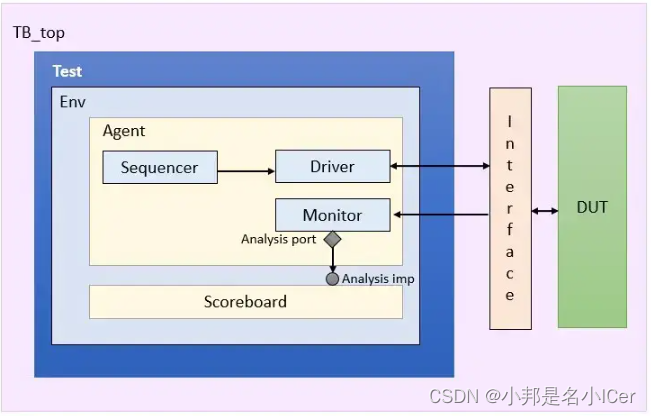

30 UVM Adder Testbench Example

1 Adder Design 加法器设计在时钟的上升沿产生两个变量的加法。复位信号用于clear out信号。注:加法器可以很容易地用组合逻辑开发。引入时钟和重置,使其具有测试台代码中时钟和重置的样子/风格。 module adder(input clk, reset, input [7:0] in1, in2, output reg [8:0] out);always@(posedge cl

关于Testbench的知识(内含例程)

关于Testbench的知识(内含例程) Testbench功能 产生激励Generate stimulus将激励输入到待测设计DUB-Design Under Verification产生预期Generate Expectation获取响应Capture response检查相应的正确性Check the response for correctness根据验证目标评估验证进度Measure

Verilog Tips 1:TestBench编写注意事项【concurrent assignment to a non-net ‘xxxx‘ is not permitted】解决

一个案例: 待测试模块输入输出为: TestBench测试文件为: 一仿真,报错 concurrent assignment to a non-net ‘xxxx’ is not permitted 原因分析: 对于待测试模块的输出 “dout_7888”,在编写测试文件的时候,不能将与之交联的“dout_7888”定义为 reg 型,须改为 wire 型。 对于模块中的输出来说 即,不能

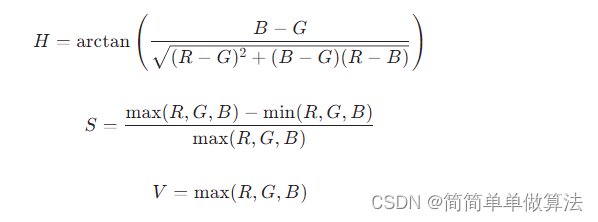

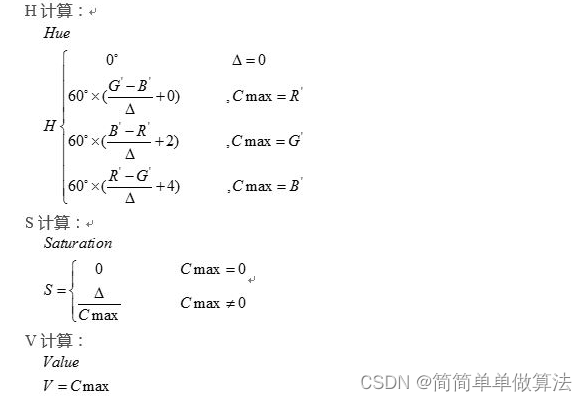

基于FPGA的图像RGB转HSV实现,包含testbench和MATLAB辅助验证程序

目录 1.算法运行效果图预览 2.算法运行软件版本 3.部分核心程序 4.算法理论概述 4.1. RGB与HSV色彩空间 4.2. RGB到HSV转换原理 5.算法完整程序工程 1.算法运行效果图预览 将FPGA的仿真结果导入到matlab中: 2.算法运行软件版本 vivado2019.2 matlab2022a 3.部分核心程序 `timescale

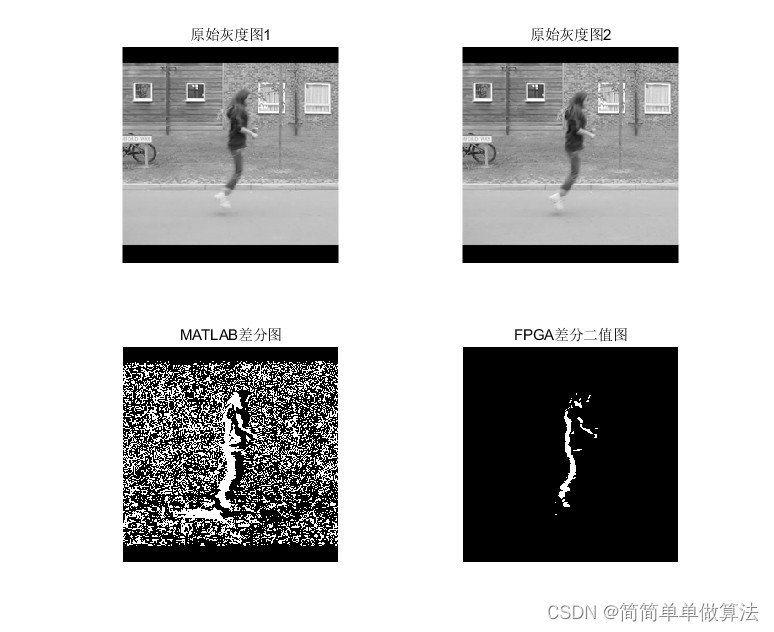

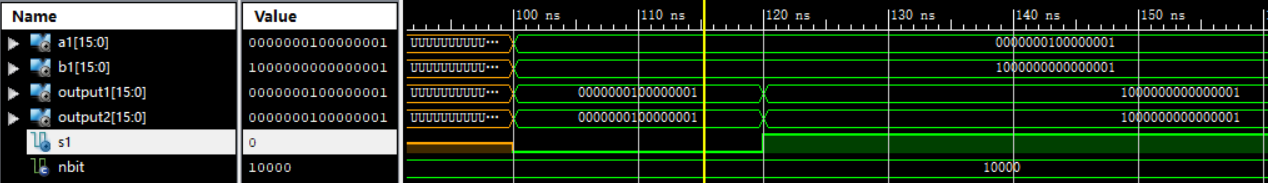

基于FPGA的图像差分运算及目标提取实现,包含testbench和MATLAB辅助验证程序

目录 1.算法运行效果图预览 2.算法运行软件版本 3.部分核心程序 4.算法理论概述 5.算法完整程序工程 1.算法运行效果图预览 2.算法运行软件版本 matlab2022a 3.部分核心程序 `timescale 1ns / 1ps//// Company: // Engineer: // // Create Date: 2022/07/28

【【二进制 无符号乘 有符号 乘法器 的设计verilog代码+testbench 】】

二进制 无符号乘 有符号 乘法器 的设计verilog代码+testbench usmultiplier.v module usmultiplier #(parameter NUMBER1 = 8 ,parameter NUMBER2 = 8 )(input [NUMBER1-1 : 0]

【【带有握手信号的无符号数乘法verilog+ testbench 代码】】

带有握手信号的无符号数乘法verilog+ testbench 代码 uumultiplier.v module uumultiplier #(parameter NUMBER1 = 8 ,parameter NUMBER2

仿真测试平台文件(TestBench)(二)

2. 测试平台文件的结构 使用VHDL语言编写测试平台文件时,所有的基本VHDL语法都是适用的,但是测试平台文件与一般的项目设计存在一些区别。一个测试平台文件必须包括与所测试的元件(UUT)相对应的原件声明,以及输入到UUT的激励描述。一个测试平台文件的基本结构如例1: 【例1】LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY t

VHDL学习笔记-(2)LAB1.2 根据MUX21的testbench写DUT

提供了testbench文件tb_mux21_generic.vhd,用mux21元件,用behavioral和structural两种方式写parametric multiplexer。 tb_mux21_generic.vhd: -- TestBench Template LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.numeric_s

Systemverilog中使用interface连接testbench和dut的端口

1.dut的端口声明如下,文件名为top.v: module top(input clk ,input rst_n ,input wr_n ,input rd_n ,input cs0_n ,input cs7_n ,input [15 : 0] bus_addr_in ,//UART淇″彿input rx0_d ,o

System verilog从Testbench中dump出所需要的数据代码

下面是一个System verilog的dump示例代码: `define DUMP_PATH $sformatf("./dump/")`define CHO_DEINTERLEAVER ldpc_decoder_top_tbch.fec_ofdm_top.fec_ofdm_top_0.de_interleaverinitial beginch0_file_ptr_data = $fopen