本文主要是介绍VHDL学习笔记-(2)LAB1.2 根据MUX21的testbench写DUT,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

提供了testbench文件tb_mux21_generic.vhd,用mux21元件,用behavioral和structural两种方式写parametric multiplexer。

tb_mux21_generic.vhd:

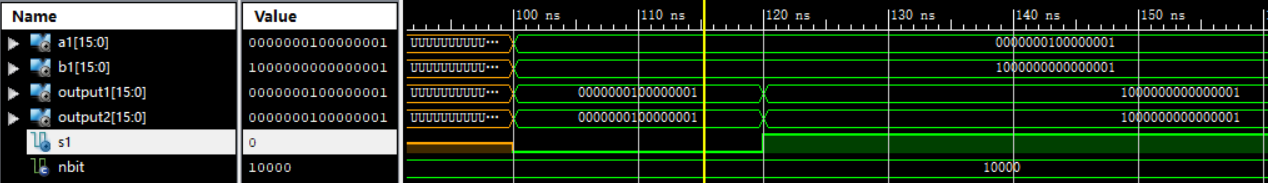

-- TestBench Template LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.numeric_std.ALL;ENTITY TBMUX21_GENERIC ISEND TBMUX21_GENERIC;ARCHITECTURE TEST OF TBMUX21_GENERIC IS CONSTANT NBIT:INTEGER:=16;SIGNAL A1,B1,OUTPUT1,OUTPUT2:STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0);SIGNAL S1:STD_LOGIC;-- Component DeclarationCOMPONENT MUX21_GENERICGENERIC(NBIT:INTEGER:=16);PORT(S : IN std_logic;A,B : IN std_logic_vector(NBIT-1 downto 0); Y: OUT std_logic_vector(NBIT-1 downto 0));END COMPONENT;BEGIN-- Component Instantiationuut1: MUX21_GENERIC GENERIC MAP(NBIT)PORT MAP(A => A1,B => B1,S => S1,Y => OUTPUT1);uut2: MUX21_GENERIC GENERIC MAP(NBIT)PORT MAP(A => A1,B => B1,S => S1,Y => OUTPUT2);-- Test Bench Statementstb : PROCESSBEGINwait for 100 ns; -- wait until global set/reset completes-- Add user defined stimulus hereA1 <= "0000000100000001";B1 <= "1000000000000001";S1 <= '0', '1' AFTER 20 ns;wait; -- will wait foreverEND PROCESS tb;-- End Test Bench END TEST;

基本元件mux21:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity mux21 isPORT(A,B,S:IN STD_LOGIC;Y :OUT STD_LOGIC);

end mux21;architecture DATAFLOW of mux21 is

beginY<=A WHEN S='0' ELSE B;

end DATAFLOW;那么parametric multiplexer的

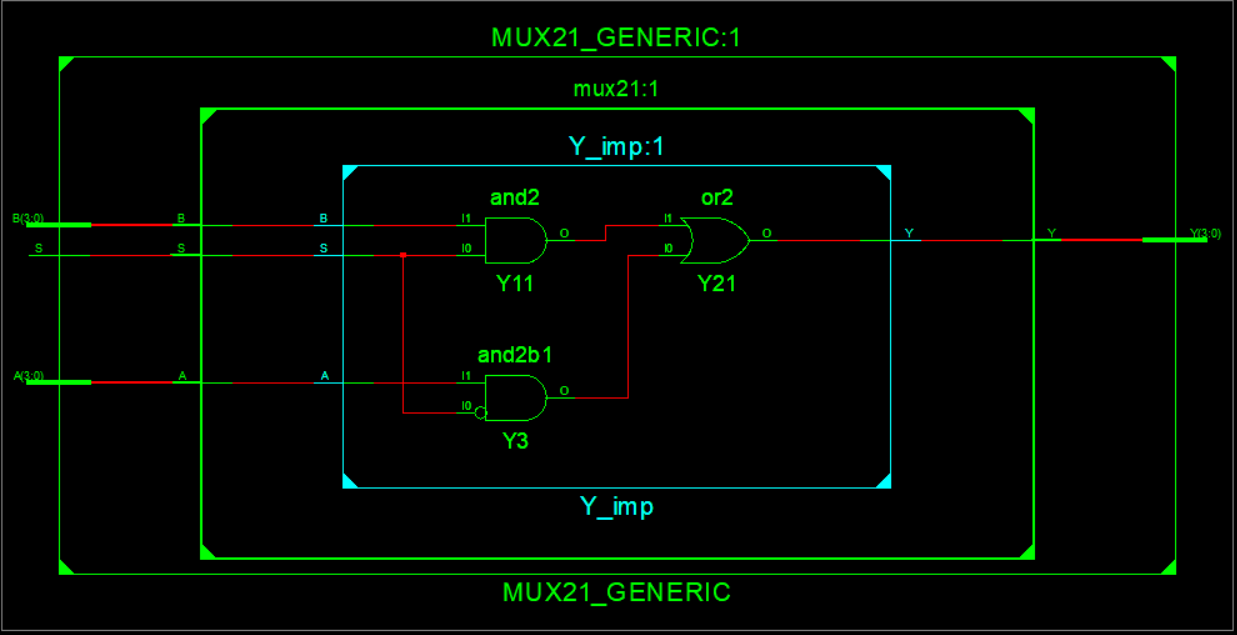

STRUCTURAL形式:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity MUX21_GENERIC is

GENERIC(NBIT:INTEGER:=4);

PORT(A,B:IN STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0);S:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0));

end MUX21_GENERIC;architecture structural of MUX21_GENERIC is

component mux21 isport(A,B,S:IN STD_LOGIC;Y :OUT STD_LOGIC);

end component;

beginu: for i in 0 to nbit-1 generatemux: mux21 port map (A => A(i),B => B(i),S => S,Y => Y(i));end generate;end structural;

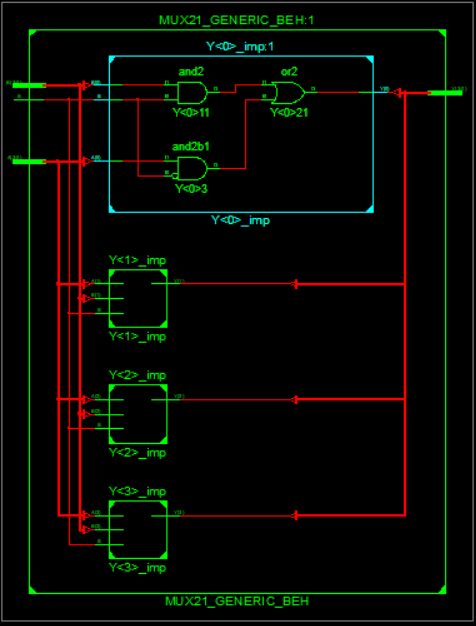

BEHAVIORAL形式:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity MUX21_GENERIC_BEH is

GENERIC (NBIT:INTEGER:=4);

PORT(A,B:IN STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0);S :IN STD_LOGIC;Y :OUT STD_LOGIC_VECTOR(NBIT-1 DOWNTO 0));

end MUX21_GENERIC_BEH;architecture Behavioral of MUX21_GENERIC_BEH isbeginPROCESS(A,B,S)BEGINIF(S='0') THEN Y<=A;ELSE Y<=B;END IF;END PROCESS;end Behavioral;

可以看出,structural和behavioral两种描述形式在综合器中是不同的。

最后附上模拟结果:

这篇关于VHDL学习笔记-(2)LAB1.2 根据MUX21的testbench写DUT的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!