fsm专题

基于Verilog表达的FSM状态机

基于Verilog表达的FSM状态机 1 FSM1.1 Intro1.2 Why FSM?1.3 How to do 在这里聚焦基于Verilog的三段式状态机编程; 1 FSM 1.1 Intro 状态机是一种代码实现功能的范式;一切皆可状态机; 状态机编程四要素:– 1.状态State: 2.转态跳转Condition Jump: 3.行为Action: 4.次态–>现

有限状态机—— FSM(finite-state machine)

//有限状态机 finite-state machine #include <stdio.h> #include <stdlib.h> #include <sys/types.h> #include <sys/stat.h> #include <fcntl.h> #include <unistd.h> #include <errno.h> #define TTY1 "/dev/tty1

HDLBits刷题Day24,3.2.5.9 Design a Moore FSM

3.2.5.9 Design a Moore FSM 问题描述 分析: 1.s=000时,打开fr1,fr2,fr3和补充水dfr 2.s=001时,打开fr1,fr2 3.s=011时,打开fr1 4.s=111时,关闭 5.当水位下降时,打开dfr 绘制一下状态转移图 代码: module top_module (input clk,input reset,input

使用函数指针实现FSM

使用函数指针实现FSM的思路:建立相应的状态表和动作查询表,根据状态表、事件、动作表定位相应的动作处理函数,执行完成后再进行状态的切换。 首先我们定义出小明一天的活动状态 //比如我们定义了小明一天的状态如下enum{GET_UP,GO_TO_SCHOOL,HAVE_LUNCH,DO_HOMEWORK,SLEEP,}; 我们也定义出会发生的事件 enum{EVENT1 = 1,EV

Gateway API 实践之(六)FSM Gateway 的健康检查功能

FSM Gateway 流量管理策略系列: 故障注入黑白名单访问控制限速重试会话保持健康检查负载均衡算法TLS 上游双向 TLS 网关的健康检查功能是一种自动化监控机制,用于定期检查和验证后端服务的健康状况,确保流量只被转发到那些健康且能正常处理请求的服务。这一功能在微服务或分布式系统中尤为关键,因为它通过及时识别并隔离故障或性能下降的服务,来维护系统的高可用性和弹性。 通过健康检查

Unity——FSM有限状态机

有限状态机就是有限个切换状态的条件,要制作有限状态机,有几个必要点:状态抽象类、FSMSystem类、FSMSystem实现类、FSM状态实现类。 每一个控制者都有一个状态机,每一个状态机都有其包含的状态,每一个状态都有能转换的状态和与之对应的转换条件。 状态抽象类 我们首先要知道,每个状态都有一个枚举类型叫Transition,这个是用来记录切换的条件的,还有一个枚举类型是

【IC设计】ICer‘s 乾坤大挪移——FSM状态机

目录 理论解读写几段式状态机? 设计实战两种state的FSM(异步复位) 理论解读 写几段式状态机? 设计实战 两种state的FSM(异步复位) 实现下图所示的摩尔状态机,复位为异步复位。 代码实现: module top_module(input clk,input areset, // Asynchronous reset to state Binpu

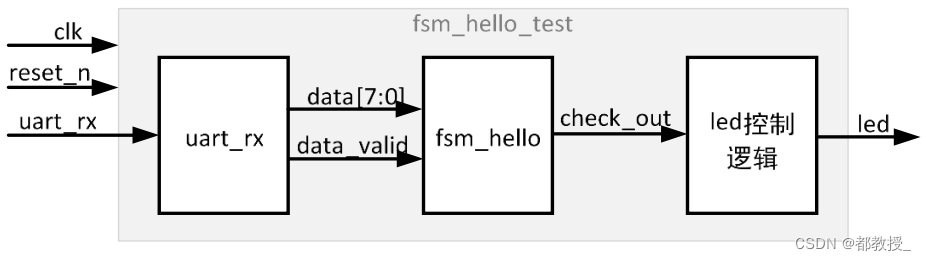

小梅哥Xilinx FPGA学习笔记16——FSM(状态机)的学习

目录 一、 状态机导读 1.1 理论学习 1.2 状态机的表示 1.3 状态机编码 1.4 状态机描述方式 二 、实战演练一(来自野火) 2.1 实验目标 2.2 模块框图 2.3 状态转移图绘制 2.4 设计文件 2.5 仿真测试文件 2.6 仿真结果 三、 实战演练二(来自野火) 3.1 实验目标 3.2 模块框图 3.3 状态转移图绘制 3.4 设计文

有限状态机(FSM)的Java 演示

版权声明:本文为博主原创文章,未经博主允许不得转载。 目录(?)[+] 本文从简单的例子入手,逐步演变成非常复杂的程序。 在简明 状态模式(5.8)中,状态之间的变换由外界控制,或者说,多种状态是分割的、无关的。状态模式最有趣的地方正是讨论其状态的变迁。 1.引子 空调(air-condition)的遥控器有两个按钮(更多的按钮在后面的例子中引入),power/电源键和cool/制冷键。

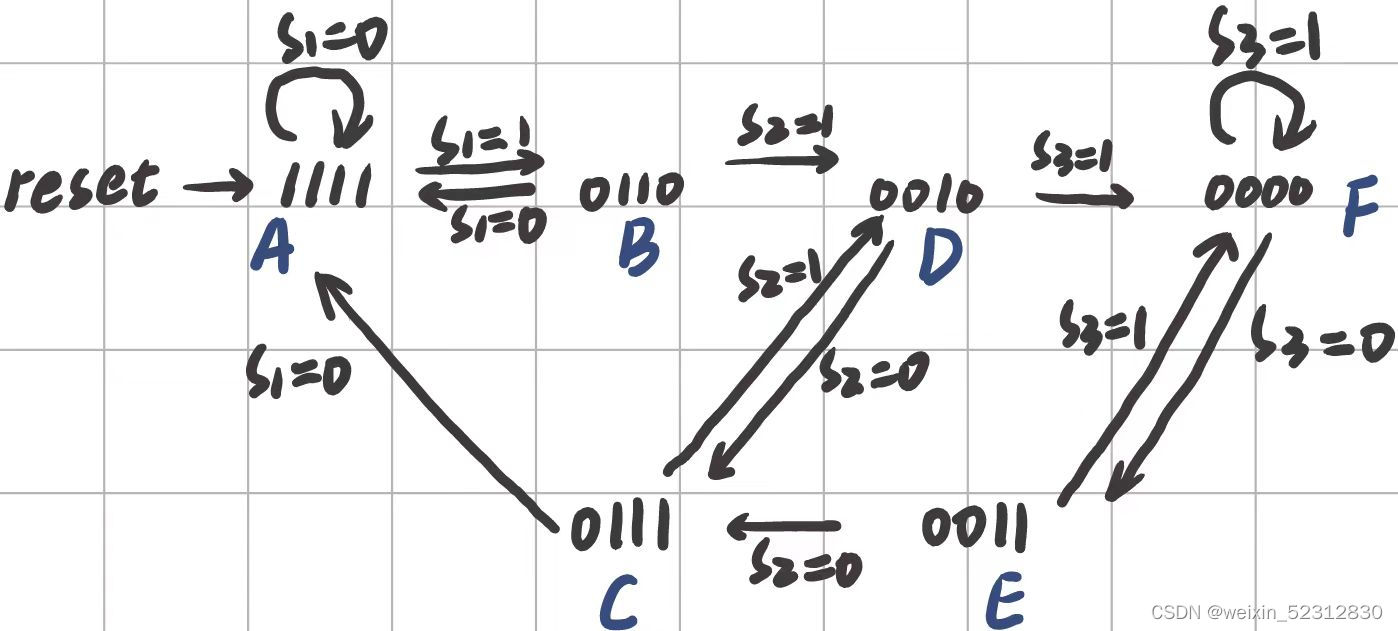

【状态机FSM 序列检测 饮料机_2023.12.1】

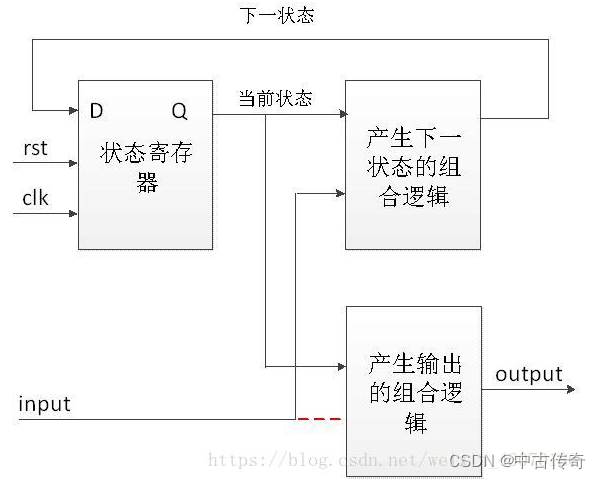

同步状态机 概念 同步状态机(同一脉冲边沿触发):有限个离散状态及某状之间的转移 异步状态机无法综合 分类 Moore状态机 只和状态有关,与输入无关 Mealy状态机 和状态和输入都有关 Mealy型比Moore型少一个状态 结构 由状态寄存器(触发器)作为状态记忆部件 仅当触发信号到达时刻才可能发生状态改变 n个触发器,最多2^n个状态 三要素 状态——状态方程 输出——输出方

EDA——连续0或连续1序列检测的有限状态机(FSM)实现

连续0或连续1序列检测的FSM实现 问题描述问题分析实现代码测试代码结果展示 UPC《EDA设计基础》课程上机作业整理 问题描述 设计一个4连续0或者4个连续1的序列检测 FSM,定义一个长序列,在七段管上分别显示检测的4个连续0和4个连续1的个数。连续0和连续1的个数在七段管上的显示,分别用函数和任务实现。 问题分析 1.什么是FSM? 有限状态机简写为FSM(Fini

FSM 有限状态机 (Finite State Machine)

状态机(FSM) 根据状态数目是否有限可以将时序状态机分为有限状态机(Finite Status Machine,FSM)和无限状态机。 FSM: Mealy & Moore Mealy: 时序逻辑电路的输出不但取决于当前状态还取决于输入。 Moore: 时序逻辑电路的输出只取决于当前状态。 在实际的设计中,其实大部分状态机都属于Mealy状态机 状态图或者状态转移表以表格的形式表示在

【小黑嵌入式系统第六课】嵌入式系统软件设计基础——C语言简述、程序涉及规范、多任务程序设计、状态机建模(FSM)、模块化设计、事件触发、时间触发

上一课: 【小黑嵌入式系统第五课】嵌入式系统开发流程——开发工具、交叉开发环境、开发过程(生成&调试&测试)、发展趋势 文章目录 一 单片机的C语言简述1、为什么要用C语言?2、单片机的C语言怎么学?之一:变量定义之二:特殊寄存器操作之三:位操作之四:中断之五:内部函数(intrinsic Function)之六:函数的可重入性讨论与总结: 二 程序设计规范1、什么要学习程序设计规

FPGA状态机 clk_divider_3_fsm

此图仅供参考,程序中3个always@语句,分别完成激励方程、转换方程和输出方程的功能。 Verilog程序 module clk_divider_3_fsm ( input sys_clk, input sys_rst_n, output reg

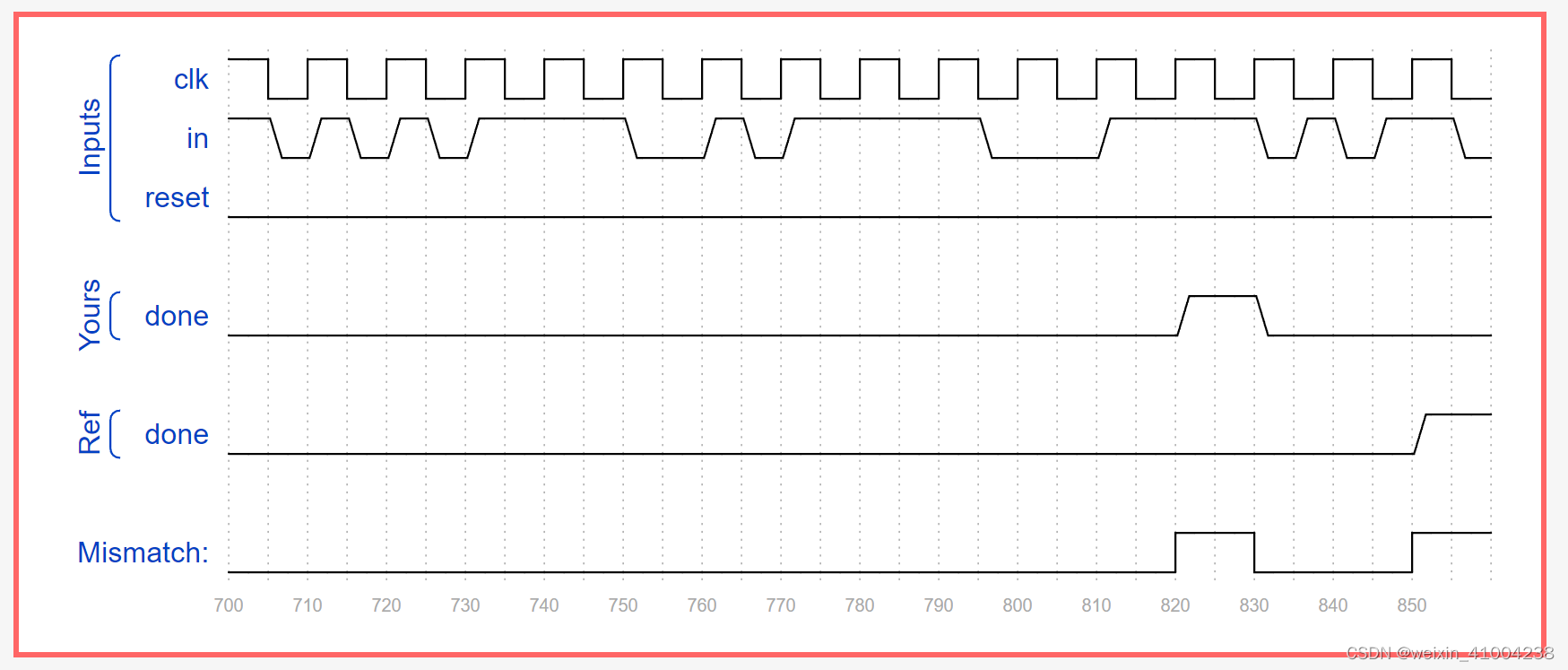

HDLbits: Fsm serial

根据题意设计了四个状态,写出代码如下: module top_module(input clk,input in,input reset, // Synchronous resetoutput done); parameter IDLE = 3'b000, START = 3'b001, DATA = 3'b010, STOP = 3'b100, bit_counter_end = 4'

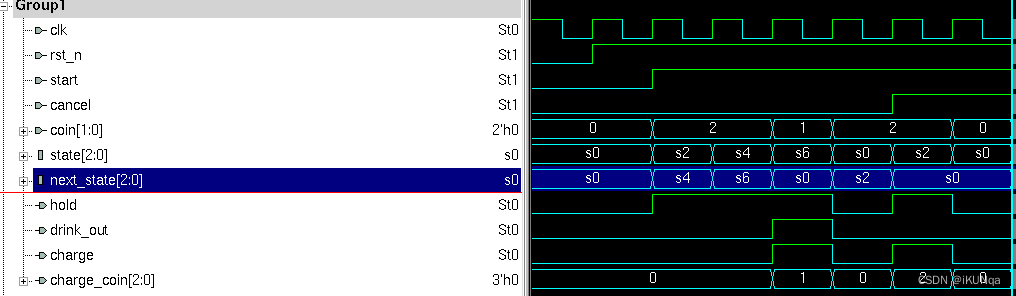

Verilog 每日一题(VL14 自动贩售机1--FSM常见题型)

自动贩售机 题目描述: 设计一个自动贩售机,输入货币有三种,为0.5/1/2元,饮料价格是1.5元,要求进行找零,找零只会支付0.5元。 ps:投入的货币会自动经过边沿检测并输出一个在时钟上升沿到1,在下降沿到0的脉冲信号 注意rst为低电平复位 信号示意图: d1 0.5元 d2 1元 d3 2元 out1 饮料 out2 零钱 这一题第一

[HDLBits] Fsm serial

In many (older) serial communications protocols, each data byte is sent along with a start bit and a stop bit, to help the receiver delimit bytes from the stream of bits. One common scheme is to use o

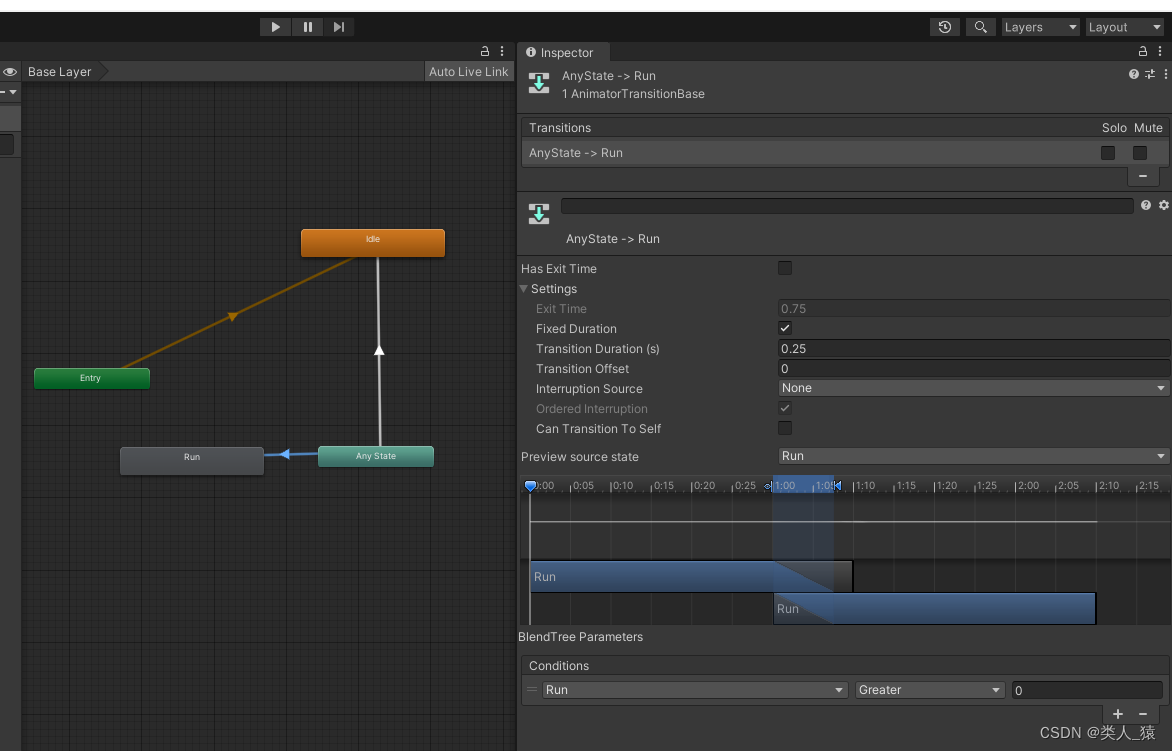

FSM人物动画状态机

人物动画状态机 介绍FSM角色模型的设置角色动作的设置角色动画控制器的设置书写角色动画的具体状态,实现缓动起步的FSM总结 介绍 摇杆我就不介绍了,之前我在这里面讲过怎么用摇杆,摇杆连接。 这里我先说下什么是FSM人物动画状态机,说白了就是一个集中管理控制角色动画状态的一个管理器。可以切换操作对象的不同动作状态。下面我放一个实例Gif这个是人物FSM动画控制+人物动作匹配缓动起步

[HDLBits] Fsm serialdata

See also: Serial receiver Now that you have a finite state machine that can identify when bytes are correctly received in a serial bitstream, add a datapath that will output the correctly-received da

HDLbits: Fsm serial

根据题意设计了四个状态,写出代码如下: module top_module(input clk,input in,input reset, // Synchronous resetoutput done); parameter IDLE = 3'b000, START = 3'b001, DATA = 3'b010, STOP = 3'b100, bit_counter_end = 4'

HDLbits: Fsm ps2

本题目理解起来有点难,要观察题目中给的三个时序图,通过时序图可以发现,状态有四个:byte1、byte2、byte3,还有一个“?”状态。其中,byte1的下一个状态一定是byte2,byte2的下一个状态一定是byte3,但是byte3的下一个状态可能是“?”,需要通过in[3]来确定。于是先写出下面的代码(运行错误): module top_module(input clk,input [7

HDLbits: Fsm ps2

本题目理解起来有点难,要观察题目中给的三个时序图,通过时序图可以发现,状态有四个:byte1、byte2、byte3,还有一个“?”状态。其中,byte1的下一个状态一定是byte2,byte2的下一个状态一定是byte3,但是byte3的下一个状态可能是“?”,需要通过in[3]来确定。于是先写出下面的代码(运行错误): module top_module(input clk,input [7

HDLbits:Fsm onehot

这道题理解有误,以为s0=10'b0000000001,s0=10'b0000000010,写成了如下的代码(有误): module top_module(input in,input [9:0] state,output [9:0] next_state,output out1,output out2);parameter s0=10'b0000000001,s1=10'b0000000010