本文主要是介绍[HDLBits] Fsm serialdata,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

See also: Serial receiver

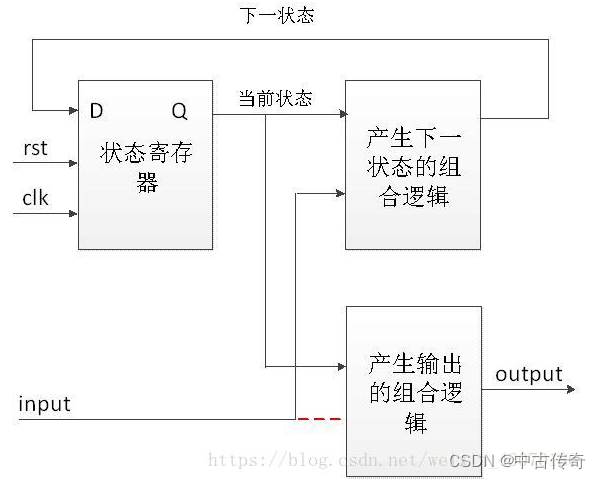

Now that you have a finite state machine that can identify when bytes are correctly received in a serial bitstream, add a datapath that will output the correctly-received data byte. out_byte needs to be valid when done is 1, and is don't-care otherwise.

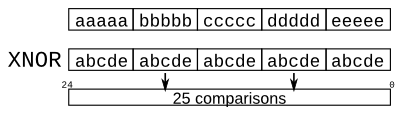

Note that the serial protocol sends the least significant bit first.

module top_module(input clk,input in,input reset, // Synchronous resetoutput [7:0] out_byte,output done

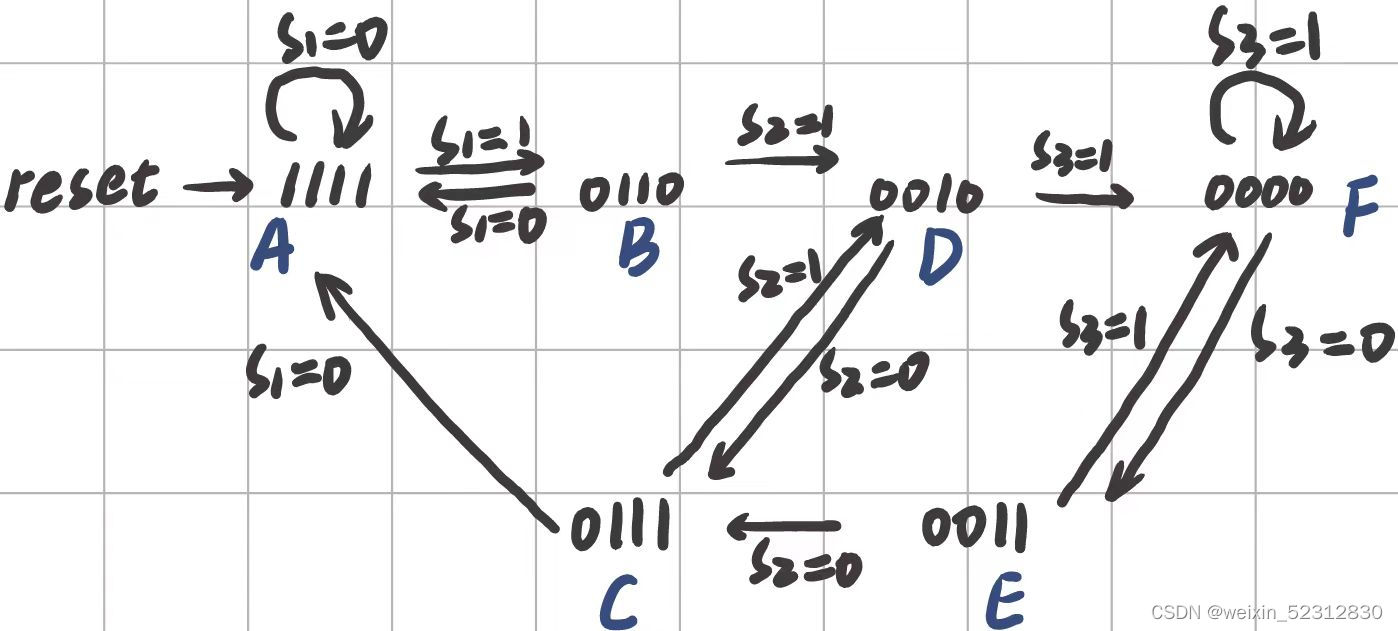

); //reg [3:0] state,next;//0:还没接到起始位,1:接到起始位,...,9:接到最后一个数据位,10:接到终止位,11:没接到终止位always@(*) begincase(state)0:next<=in?0:1;1:next<=2;2:next<=3;3:next<=4;4:next<=5;5:next<=6;6:next<=7;7:next<=8;8:next<=9;9:next<=in?10:11;10:next<=in?0:1;//接到终止位后接到0即开始位,那就直接跳到111:next<=in?0:11;//判断是否接到终止位。这里是设置了两种终止位状态来判断是否doneendcaseendalways@(posedge clk) beginif(reset)state<=0;elsestate<=next;endassign done=(state==10);// Use FSM from Fsm_serialalways@(posedge clk) begincase(state)1:out_byte[0]<=in;2:out_byte[1]<=in;3:out_byte[2]<=in;4:out_byte[3]<=in;5:out_byte[4]<=in;6:out_byte[5]<=in;7:out_byte[6]<=in;8:out_byte[7]<=in; endcaseend// New: Datapath to latch input bits.endmodule

这篇关于[HDLBits] Fsm serialdata的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[HDLBits] Simple wire](/front/images/it_default.gif)