本文主要是介绍[HDLBits] Fsm serial,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

In many (older) serial communications protocols, each data byte is sent along with a start bit and a stop bit, to help the receiver delimit bytes from the stream of bits. One common scheme is to use one start bit (0), 8 data bits, and 1 stop bit (1). The line is also at logic 1 when nothing is being transmitted (idle).

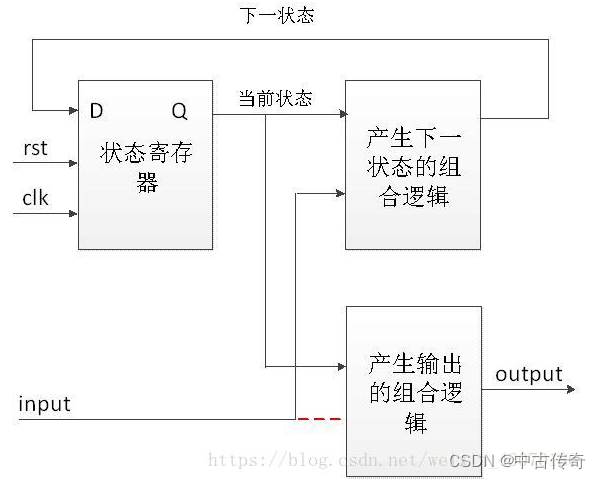

Design a finite state machine that will identify when bytes have been correctly received when given a stream of bits. It needs to identify the start bit, wait for all 8 data bits, then verify that the stop bit was correct. If the stop bit does not appear when expected, the FSM must wait until it finds a stop bit before attempting to receive the next byte.

module top_module(input clk,input in,input reset, // Synchronous resetoutput done

); reg [3:0] state,next;//0:还没接到起始位,1:接到起始位,...,9:接到最后一个数据位,10:接到终止位,11:没接到终止位always@(*) begincase(state)0:next<=in?0:1;1:next<=2;2:next<=3;3:next<=4;4:next<=5;5:next<=6;6:next<=7;7:next<=8;8:next<=9;9:next<=in?10:11;10:next<=in?0:1;//接到终止位后接到0即开始位,那就直接跳到111:next<=in?0:11;//判断是否接到终止位。这里是设置了两种终止位状态来判断是否doneendcaseendalways@(posedge clk) beginif(reset)state<=0;elsestate<=next;endassign done=(state==10);

endmodule

这篇关于[HDLBits] Fsm serial的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!