chisel专题

chisel note

使用jupyter/binder(Scala编程第四版高宇翔译):https://gke.mybinder.org/ https://github.com/freechipsproject/chisel-bootcamp 等待几秒后:点击对应的标签就可以一章一章的在线练习了: //------------------------------------------------

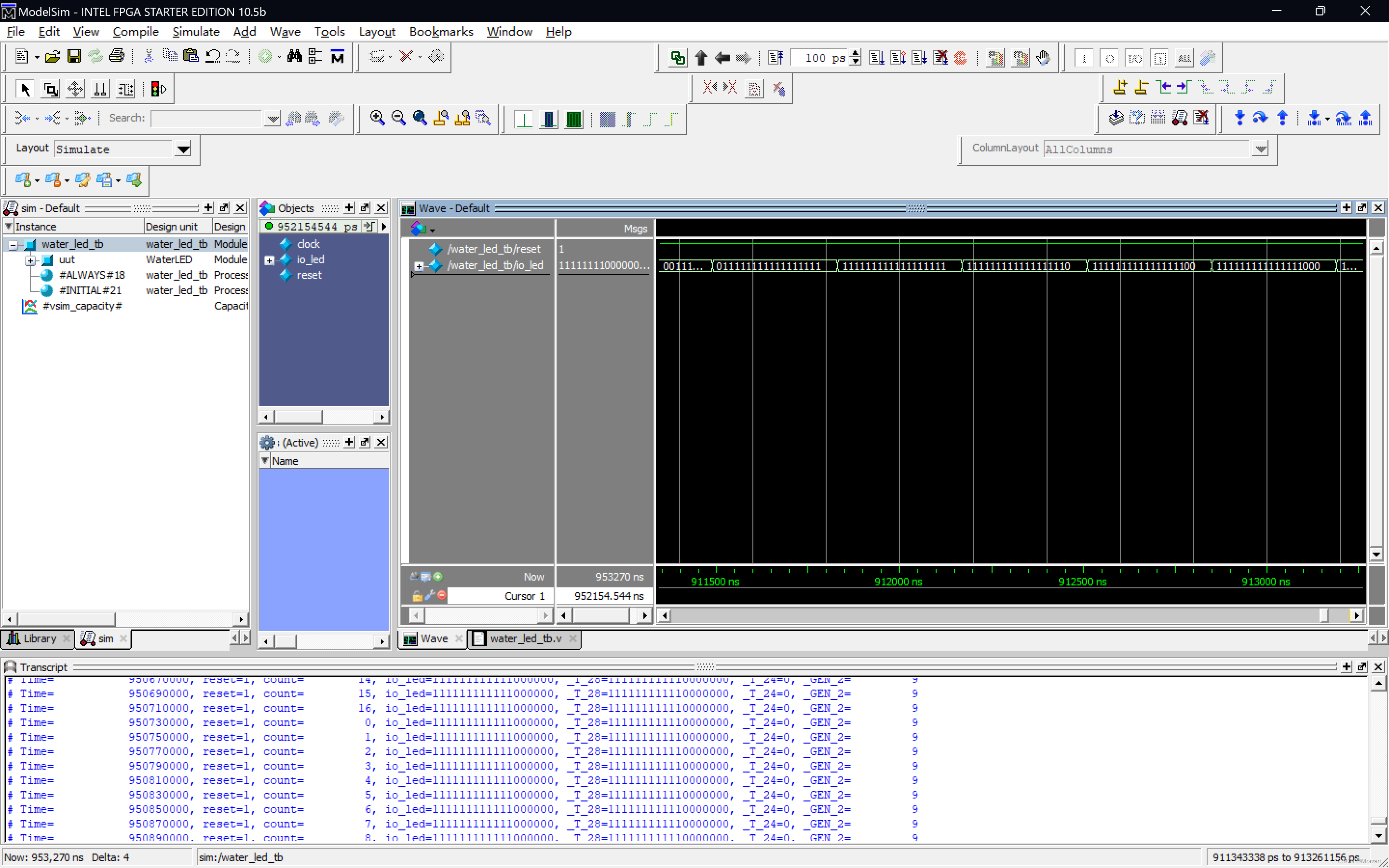

基于Chisel的FPGA流水灯设计

Chisel流水灯 一、Chisel(一)什么是Chisel(二)Chisel能做什么(三)Chisel的使用(四)Chisel的优缺点1.优点2.缺点 二、流水灯设计 一、Chisel (一)什么是Chisel Chisel是一种基于Scala的硬件构造语言,它允许设计者使用高级的编程概念来构建硬件。Chisel的设计哲学是“不要重复自己”(DRY),这意味着它鼓励设计者通

基于Chisel语言的FPGA流水灯程序

目录 一、 内容概要二、 Chisel介绍三、 Chisel的使用四、 流水灯实现五、 心得体会六、 参考链接 一、 内容概要 Chisel介绍Chisel使用流程Chisel流水灯实操 二、 Chisel介绍 Chisel 是一种构建硬件描述语言(HDL)的高级编程语言,它允许硬件设计师以更抽象的方式编写代码,然后编译生成低级的硬件描述语言(通常是Verilog)代码,进而

【chisel】chisel怎么在withClockAndReset中使用非时钟信号

在 Chisel 中,withClockAndReset 是一个用于在特定时钟和复位信号下定义硬件行为的上下文管理器。当你需要在 withClockAndReset 块中使用非时钟信号时,你可以直接引用这些信号,只要它们已经在模块的 I/O 中定义,并且已经被连接到相应的端口。 以下是如何在 withClockAndReset 块中使用非时钟信号的示例: class MyModule exte

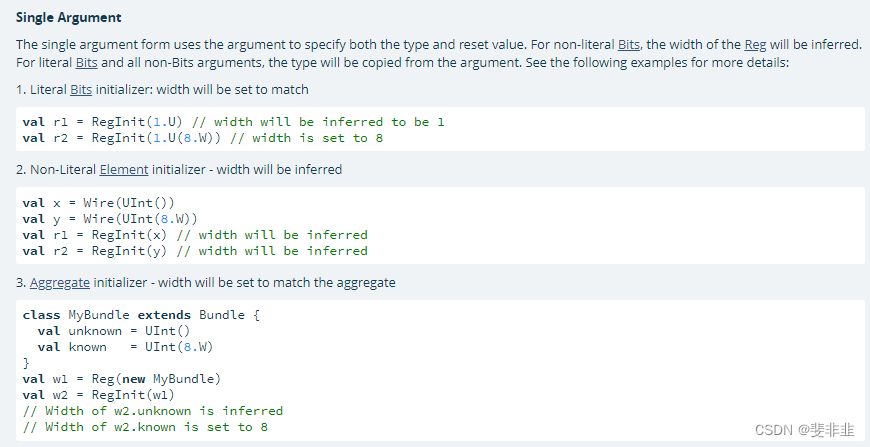

【chisel】chisel怎么给io wire定义初值

在 Chisel 中,为 IO 节点的 Wire 定义初始值通常与特定的信号类型和使用场景有关。以下是一些定义初始值的常见方法: 使用 RegInit 创建寄存器并定义初始值: 当您想要为一个寄存器类型的 Wire 定义初始值时,可以使用 RegInit。以下是一个例子: class MyModule extends Module {val io = IO(new Bundle

【chisel】如何用chisel写一个上升沿检测程序

自定义上升沿检测 class RisingEdgeDetector extends Module {val io = IO(new Bundle {val inSig = Input(Bool())val outSig = Output(Bool())val clock = Input(Clock())})// 定义 risingedge 函数def risingedge(x: Bool): B

【Chisel】chisel中怎么处理类似verilog的可变位宽和parameter

在 Chisel 中处理可变位宽和参数的方式与 Verilog 有一些不同,因为 Chisel 是建立在 Scala 语言之上的。以下是如何在 Chisel 中处理这些概念的方法: 参数化(Parameters) 在 Chisel 中,参数化是通过在模块构造函数中定义参数来实现的。这些参数可以是整数、位宽、硬件类型等。例如: class MyModule(va

Chisel中对对<: 和:的理解(其实是Scala中的理解)

在 Scala 语言和 Chisel 硬件构造语言中,<: 和 : 是用于类型注解的两个不同的符号,它们在泛型编程和类型系统中扮演重要角色。下面是它们各自的意义和用途: <:(子类型关系) <: 符号在 Scala 中表示子类型关系,即左边的类型是右边类型的子类型。在类或特质的参数列表中使用时,它用来限制类型参数可以扩展的具体类型或类型层次结构。 用法示例:trait Animalclas

在Chisel3中,不支持对子字(subword)进行赋值。在 Chisel 中,UInt 类型是一个不可变的位宽数据类型,它表示一个固定位宽的无符号整数。

在Chisel3中,不支持对子字(subword)进行赋值。这种设计决策背后的原因涉及到硬件描述语言中类型和数据抽象的最佳实践。 不支持子字赋值的原因 硬件描述的性质: 在硬件设计中,操作和修改单独的位或子字通常与较高的复杂性和资源消耗相关。而且,对单独位的操作可能会导致设计难以预测的时序问题和效率低下。 抽象和封装: Chisel鼓励使用更高级别的抽象,如Bundle(类似于结构体或记录

Windows上构建 Chisel-Bootcamp

windows环境构建本地Chisel-Bootcamp 安装摘要Chisel-boocamp环境搭建安装java安装Anaconda安装scala 下载Chisel-bootcamp 环境Reference 安装摘要 在windows上安装chisel-boocamp,与linux过程类似。 安装java8安装anaconda安装scala下载Chisel-bootcamp环

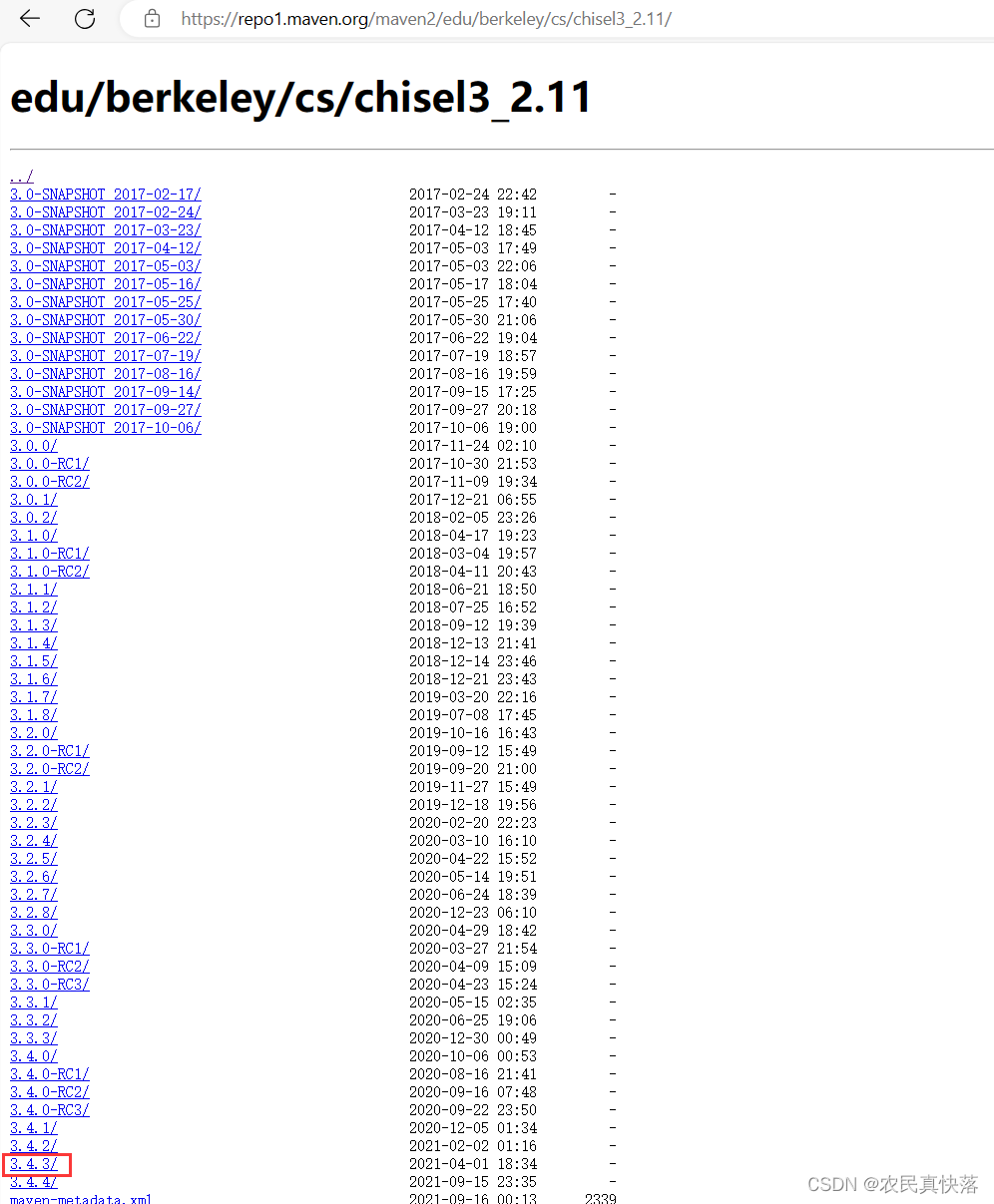

【异常处理】sbt构建Chisel库时出现extracting structure failed:build status:error的解决办法

文章目录 报错背景:解决思路:①IDEA中配置本地的SBT进行下载②更改下载源为华为的镜像站1. 修改sbtconfig.txt2. 增加repositories文件 ③查看报错信息 总结整理的Scala-Chisel-Chiseltest版本信息对应表 报错背景: 最近在写Chisel时,构建项目常常需要等待很久,然后报错extracting structure failed

chisel入门初步2_2——-1/2次方生成器

由之前的GCN网络的介绍可以得知,我们需要输入两个乘数(两个节点的节点度),并输出他们乘积的-1/2次方,此处由于当时设计的booth编码的乘法器为有符号数,而此处是无符号数,实在懒得再写一份了,这里直接写个乘号,留给chisel自己去优化吧 此处设计输入的节点度位宽为8位,即支持节点最高与255个节点相连。考虑到-1/2次方对于硬件设计中的艰难性——无论是对时间和资源的消耗还是对脑力的消耗,这

chisel RegInit/UInt/U

val reg = RegInit(0.U(8.W)) //okval reg = RegInit(0.UInt(8.W)) //err U 使用在数字 . 后边50.U UInt 使用在IO(new Bundle val a = Input(UInt(8.W)) 或者 def counter(max:UInt, a1:UInt) package emptyimport chi

【chisel】 环境,资料

Chisel环境搭建教程(Ubuntu) 根据上边的link去安装; 目前scala最高版本用scala-2.13.10,太高了 没有chisel的库文件支持;会在sbt下载的过程中报错; [error] sbt.librarymanagement.ResolveException: chisel chisel目前的一些状况,问题 Chisel,说爱你不容易 Chisel相较于verilo

chisel入门初步1——基4的booth编码的单周期有符号乘法器实现

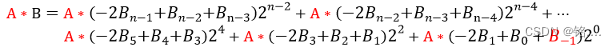

基4的booth编码乘法器原理说明 基2的booth编码 本质来说就是一个裂项重组,乘法器最重要的设计是改变部分积的数量,另外在考虑有符号数的情况下,最高位符号位有特别的意义。 (注:部分积是指需要最后一起加和的所有部分乘积的项) 下面直接套用其他人图片进行展示,来源如下 https://blog.csdn.net/weixin_42330305/article/details/1228682

iOS Chisel命令

//联系人:石虎 QQ: 1224614774 昵称:嗡嘛呢叭咪哄 一、概念 英文版: Debugger commands: apropos -- List debugger commands related to a word or subject. breakpoint -- Command

iOS lldb调试Chisel增强插件安装过程

//联系人:石虎 QQ: 1224614774 昵称:嗡嘛呢叭咪哄 一、概念 安装Chisel之前先安装一下Homebrew,在终端执行下面一行命令安装完毕 ruby -e "$(curl -fsSL https://raw.githubusercontent.com/Homebrew/install/master/install)" 图1:终端执行bre

第二十三章 Chisel基础——函数的应用

函数是编程语言的常用语法,即使是Verilog这样的硬件描述语言,也会用函数来构建组合逻辑。对于Chisel这样的高级语言,函数的使用更加方便,还能节省不少代码量。不管是用户自己写的函数、Chisel语言库里的函数还是Scala标准库里的函数,都能帮助用户节省构建电路的时间。 一、用函数抽象组合逻辑 与Verilog一样,对于频繁使用的组合逻辑电路,可以定义成Scala的函数形式,然后通过函数

Gemmini测试test文件chisel源码详解(二)

HeaderGenerationUnitTest.scala 源码如下: package gemminiimport org.scalatest.FlatSpecclass HeaderGenerationUnitTest extends FlatSpec {it should "generate a header" in {println(GemminiConfigs.defaultConf

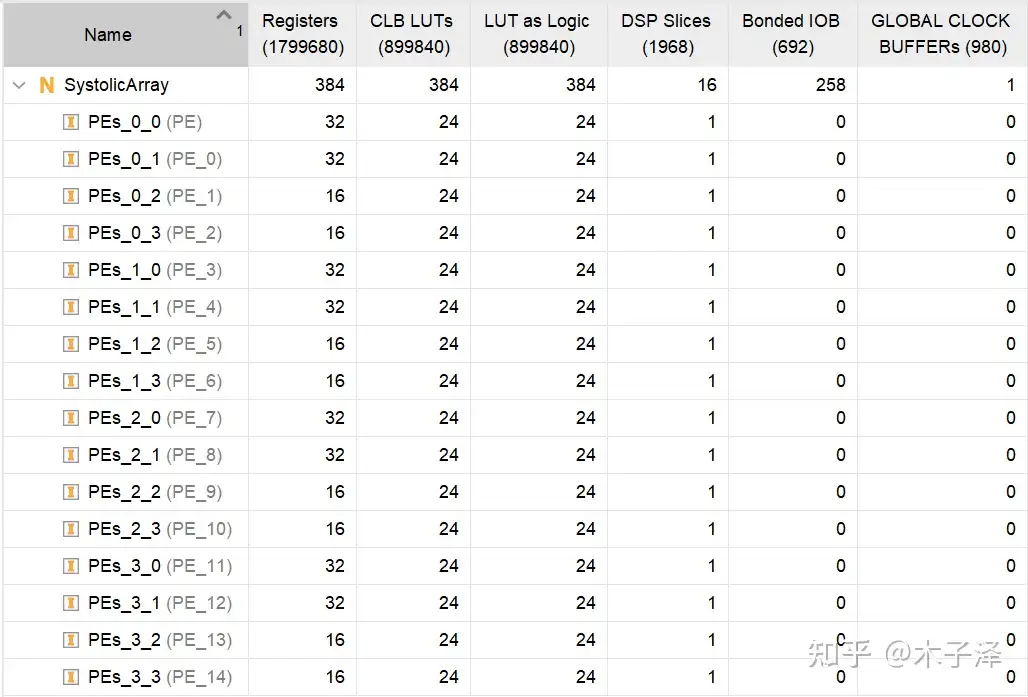

使用Chisel搭建Systolic Array

最近听到非常多人吹Chisel,为了方便快速做算法实现,就去尝试学了下,发现确实很香,有种相见恨晚的感觉。 今天是使用Chisel搭建个脉动阵列(Systolic Array, SA)[1],脉动阵列是神经网络中最基础也是最常用的组件之一。它主要是实现高效的矩阵乘法,而神经网络中到处都是矩阵乘法,从全连接层到卷积层(GEMM),都可以用矩阵乘法表示。UCB的Chipyard中专门集成了个脉动阵列

如何加快香山处理器Chisel->Verilog编译速度

=========================================== graalvm installation =========================================== 更换JVM。我们推荐使用GraalVM代替OpenJDK。 使用GraalVM免费版作为JVM编译香山比OpenJDK快10%-20%。 ----------------------