本文主要是介绍chisel RegInit/UInt/U,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

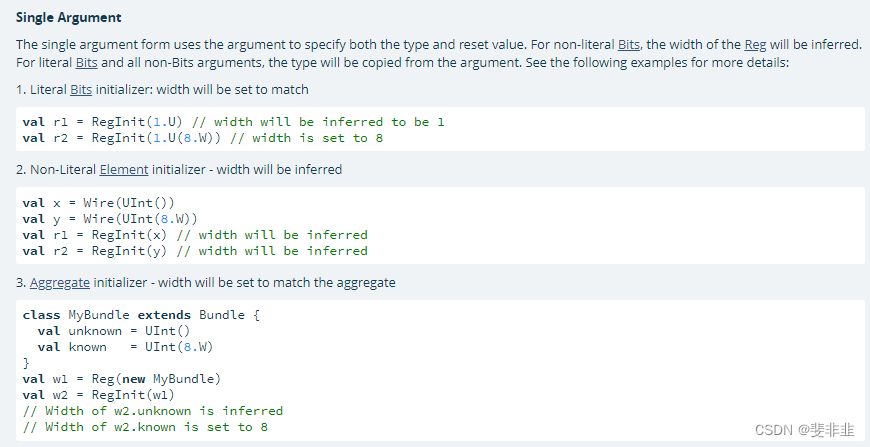

val reg = RegInit(0.U(8.W)) //ok

val reg = RegInit(0.UInt(8.W)) //err

U 使用在数字 . 后边50.U

UInt 使用在IO(new Bundle val a = Input(UInt(8.W)) 或者 def counter(max:UInt, a1:UInt)

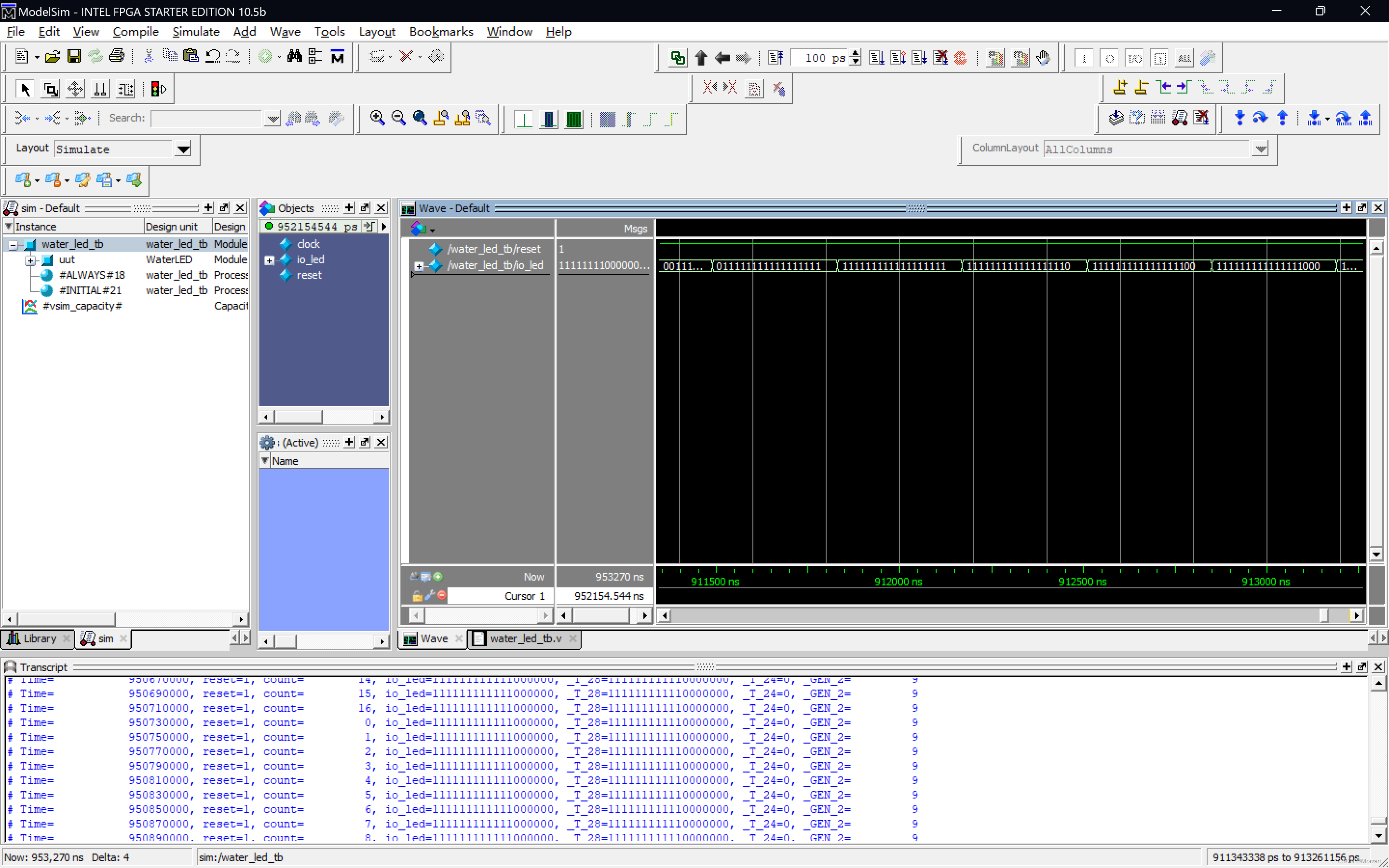

package emptyimport chisel3._

import chisel3.util._class MyCounter extends Module {val io = IO(new Bundle {val a = Input(UInt(8.W)) //val a = Input(U(8.W)) val c = Output(UInt(8.W))})val init = io.adef counter(max:UInt, a1:UInt) ={ //max:U //errval reg = RegInit(a1) //ok//val reg = RegInit(0.U(8.W)) //ok//val reg = RegInit(0.UInt(8.W)) //errwhen(reg===max) {reg := 0.U(max.getWidth.W)}.otherwise {reg := reg + 1.U(1.W)}reg // return value}io.c := counter(50.U, io.a)

}object MyCounterMain extends App {println("Generating the adder hardware")emitVerilog(new MyCounter(), Array("--target-dir", "generated"))

}这篇关于chisel RegInit/UInt/U的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![sql: Scan error on column index 6: converting driver.Value type []uint8 () to a uint: invalid synt](/front/images/it_default.jpg)