本文主要是介绍基于Chisel语言的FPGA流水灯程序,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

- 一、 内容概要

- 二、 Chisel介绍

- 三、 Chisel的使用

- 四、 流水灯实现

- 五、 心得体会

- 六、 参考链接

一、 内容概要

- Chisel介绍

- Chisel使用流程

- Chisel流水灯实操

二、 Chisel介绍

Chisel 是一种构建硬件描述语言(HDL)的高级编程语言,它允许硬件设计师以更抽象的方式编写代码,然后编译生成低级的硬件描述语言(通常是Verilog)代码,进而用于 FPGA 或 ASIC 的设计实现。Chisel 由加州大学伯克利分校的伯克利软件定义硬件(BSDH)项目开发,其主要目标是提高硬件设计的生产效率、可读性和可维护性。

概念:

Chisel 结合了现代软件工程的原理与硬件设计的实践,支持面向对象编程特性,如类、继承、多态等,同时也引入了静态类型和类型安全的概念,有助于在设计阶段捕捉错误。它利用Scala 语言作为基础,这意味着设计师可以利用Scala 强大的库和工具生态系统。Chisel 提供了一套丰富的数据类型和构造,使得设计者能够以高层次的抽象来描述数字电路,比如向量、内存、多路复用器等,并且支持参数化模块,便于设计复用和配置。

用途:

提高设计效率:Chisel 的高层抽象能力使得设计师可以更快地实现复杂的数字电路设计,减少手动编写底层 HDL 代码的工作量。

增强可读性和可维护性:通过使用高级语言特性,Chisel 设计的代码更加接近自然语言,易于阅读和理解,有利于团队协作和长期维护。

促进设计复用:Chisel 支持模块化和参数化设计,便于创建可配置的组件库,加速后续项目开发。

简化验证流程:Chisel 设计可以直接与验证框架(如Chisel Testers 2)集成,支持快速创建测试平台,加速设计验证过程。

教育和研究:Chisel 的高级特性降低了硬件设计的入门门槛,使其成为教学和研究的理想工具,特别是在计算机体系结构和并行计算领域。

综上所述,Chisel 作为一种现代化的硬件设计语言,极大地提升了硬件设计的抽象层次,促进了设计的灵活性、高效性和质量,是现代硬件设计和研究中的一个重要工具。

学习Chisel语法规则等可以在吃透Chisel语言进行学习

三、 Chisel的使用

本文将介绍Chisel在IDEA中的使用方法

Chisel 是以Scala语言为基础的语言,而Scala又是以Chisel为基础的语言,这样套壳,也可以认为Chisel是以Java为基础的语言,语法比较类似,同样也就能在IDEA进行编译

- 准备一个IDEA:下载地址

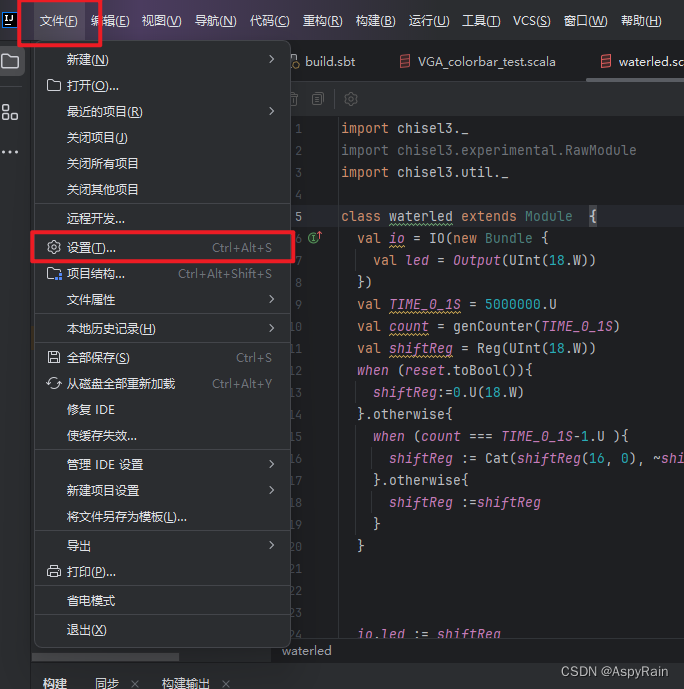

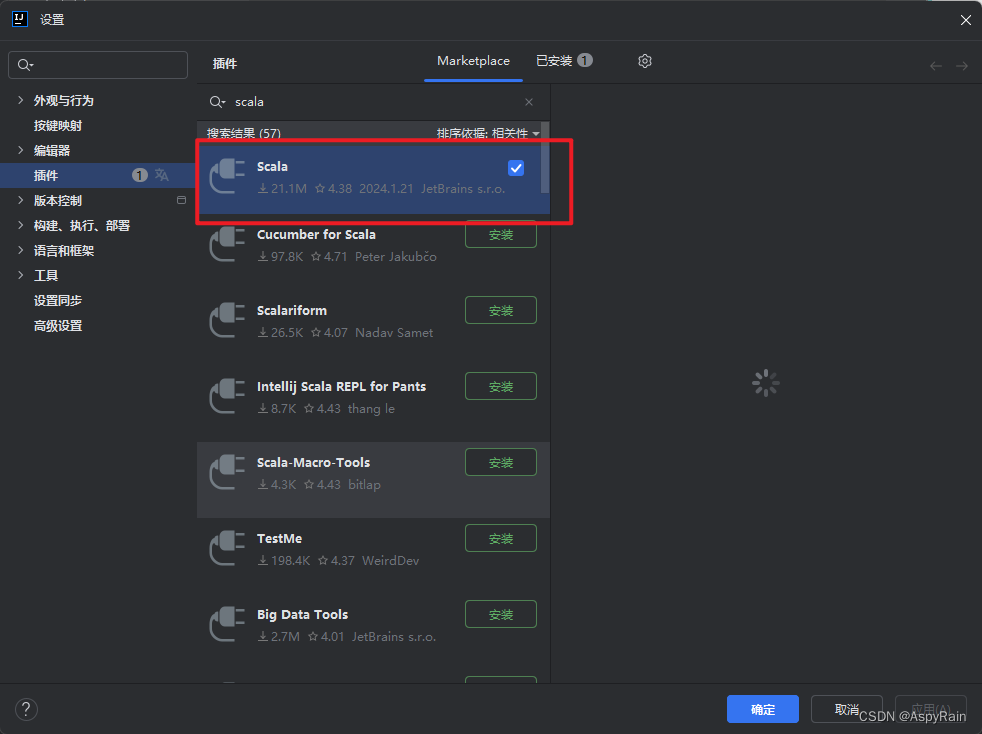

- 在IDEA里面下载scala插件:

(我的IDEA下载了汉化插件,所以界面文本是中文)

在files->setting->Plugin里面搜索Scala然后下载(也可以搜索chinese下一个汉化插件Chinese(simplified) Language)

下载完成后重启IDEA - 创建Scala项目

Scala版本必须选择2.12.12及以前的,后续版本不再支持Chisel - 配置Chisel

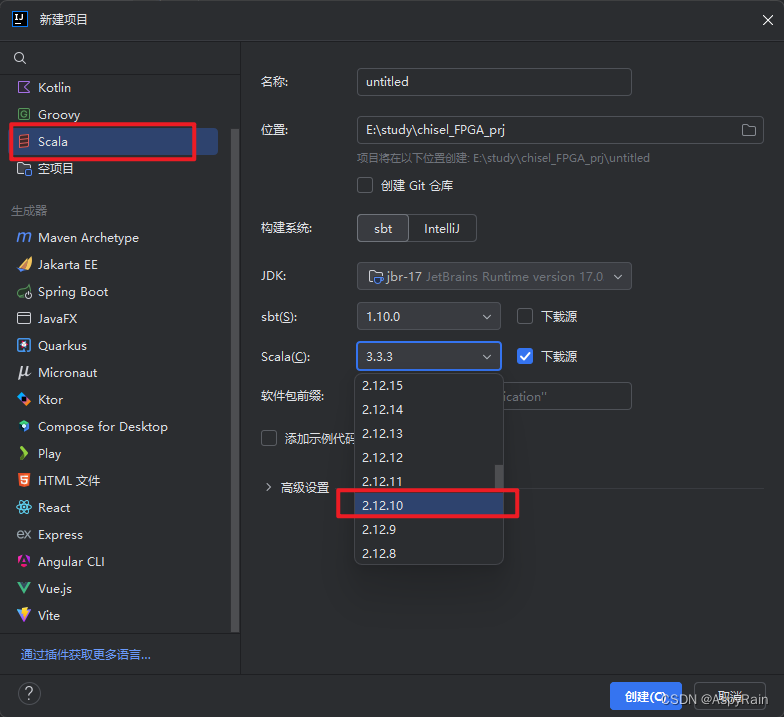

在根目录找到配置文件build.sbt,复制粘贴以下文本:

name := "chisel4De2115"version := "0.1"scalaVersion := "2.12.10"

scalacOptions += "-Xsource:2.11"

libraryDependencies += "edu.berkeley.cs" %% "chisel3" % "3.1.2"

libraryDependencies += "edu.berkeley.cs" %% "chisel-iotesters" % "1.2.3"

Scala版本根据自己版本选择,name也可自定义

然后点击以下按钮其中之一:

构建成功后就可以写Chisel代码了

四、 流水灯实现

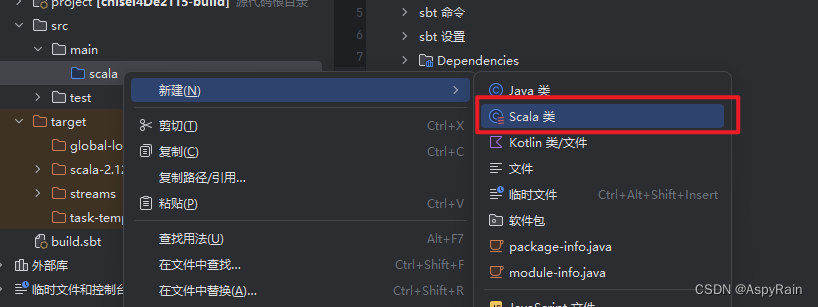

在src/main/scala目录下新建一个scala文件

复制粘贴以下代码:

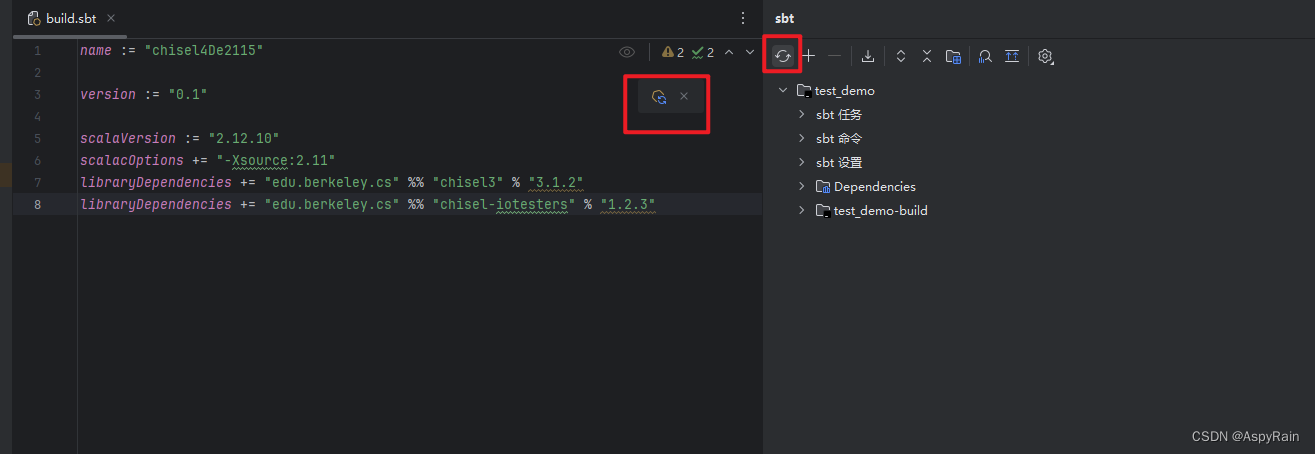

import chisel3._

import chisel3.experimental.RawModule

import chisel3.util._class waterled extends Module {val io = IO(new Bundle {val led = Output(UInt(18.W))})val TIME_0_1S = 5000000.Uval count = genCounter(TIME_0_1S)val shiftReg = Reg(UInt(18.W))when (reset.toBool()){shiftReg:=0.U(18.W)}.otherwise{when (count === TIME_0_1S-1.U ){shiftReg := Cat(shiftReg(16, 0), ~shiftReg(17))}.otherwise{shiftReg :=shiftReg}}io.led := shiftRegdef genCounter(n: UInt): UInt = {val cntReg = RegInit(0.U(32.W))cntReg := Mux(cntReg === n, 0.U, cntReg + 1.U)cntReg}

}object LEDCounterDriver extends App {chisel3.Driver.execute(args, () => new waterled())

}

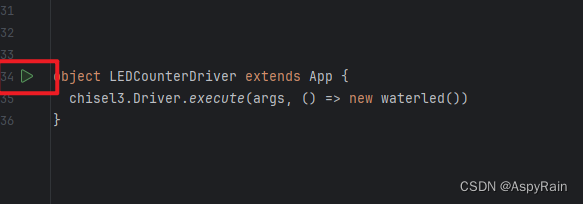

然后点击运行,将chisel代码转化成verilog代码

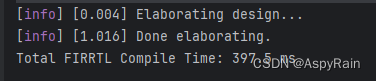

运行成功

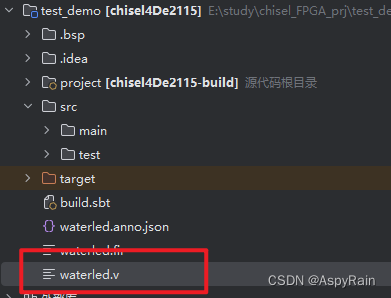

在根目录下可以找到.v文件

可以直接将这个文件放到quartus里面进行编译烧录查看结果:

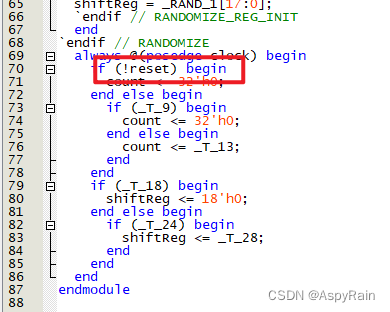

注意:这个代码是按住按钮才会进行流水灯,松开就灯灭重置,要想松>开流水灯,按下重置的话,暂时没有找到如何从chisel代码入手修改,所>以需要在verilog代码修改,只需要在reset前加一个感叹号取个反即可

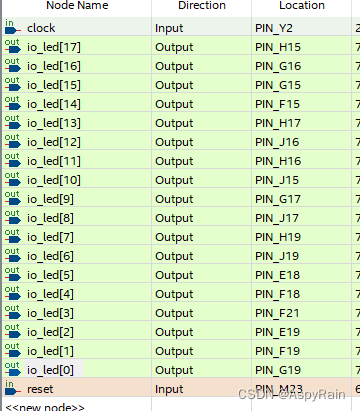

参考管脚:

运行结果:

五、 心得体会

学习Chisel语言是一段既充满挑战又极具启发性的旅程。Chisel以Scala为基础,它的抽象级别高,极大提升了硬件设计效率,让代码更简洁且易于维护。通过Chisel,我体验了用近似软件工程的思维做硬件设计的便捷,特别是在模块化、参数化设计上的优势,这为复用代码和快速迭代创造了条件。Chisel结合Scala的强大生态,使得测试和验证更加高效,同时降低了硬件设计的学习曲线,尤其适合教学和研究用途。亲手实践,如在IDEA中配置环境并实现流水灯项目,让我深刻理解了理论到实践的每一步,过程中遇到问题的解决也锻炼了自我探索能力。总之,Chisel正引领硬件设计的新风潮,它不仅丰富了我的技术栈,也激发了对硬件设计未来无限可能的想象。

六、 参考链接

- [Windows+Intellij IDEA 2020.2]chisel开发环境配置

- 吃透Chisel语言

这篇关于基于Chisel语言的FPGA流水灯程序的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!