本文主要是介绍以ARM Cortex-A55/A53为例分析 L1/L2/L3 cache所支持的写策略(write-back/wirte-through,写通和写回),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在文章 ARM 中缓存维护策略:Allocate policy(读分配/写分配),Write policy(写通/写回)以及replacement policy基础知识中,笔者介绍了ARM cache的Write policy(写通/写回)。今天我们以ARM Cortex-A55和A53为例,具体分析各级cache(L1/L2/L3 )对Write policy(写通/写回)的支持情况。

Cortex-A55/A53

- 一,Cortex-A53 处理器

- 二,Cortex-A55 处理器

一,Cortex-A53 处理器

Cortex-A53 处理器支持 L1 cache(instruction cache 和 data cache)以及L2 cache (unified cache)。

Cortex-A53处理器将缓存同步逻辑简化成了如下的内存类型:

- 当内存类型为nner Write-Back 和Outer Write-Back 时,数据可以被缓存到 L1 Data cache 以及L2 cache中。

- 当内存类型为Inner Write-Through时,Cortex-A53会将Inner Write-Through降级为Non-cacheable。

- 当内存类型为Outer Write-Through 或者 Outer Non-cacheable时,也会被Cortex-A53降级为Non-cacheable,就是内存的inner属性为Write-Back。

上述规则如何理解呢?

就是说Cortex-A53处理器的L1 data cache以及L2 cache都不支持Write-Through策略,当处理器访问内存类型为Write-Through的数据时,这些数据并不会经过L1 data cache和L2。

至于L1 instruction cache,对于指令数据,处理器只是读取,并不会写,所以cache 的写策略对指令缓存不起作用。

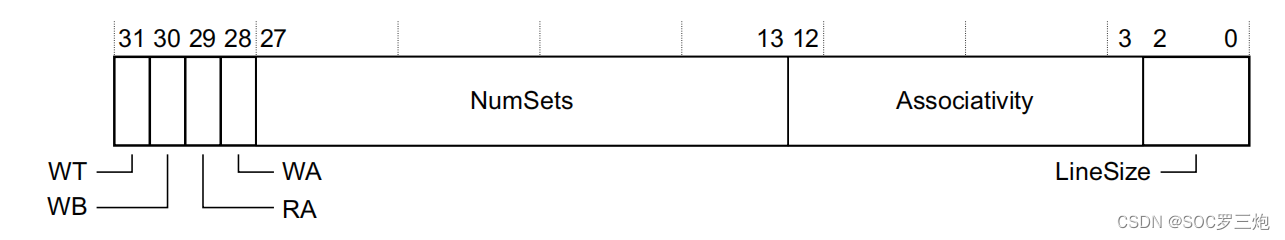

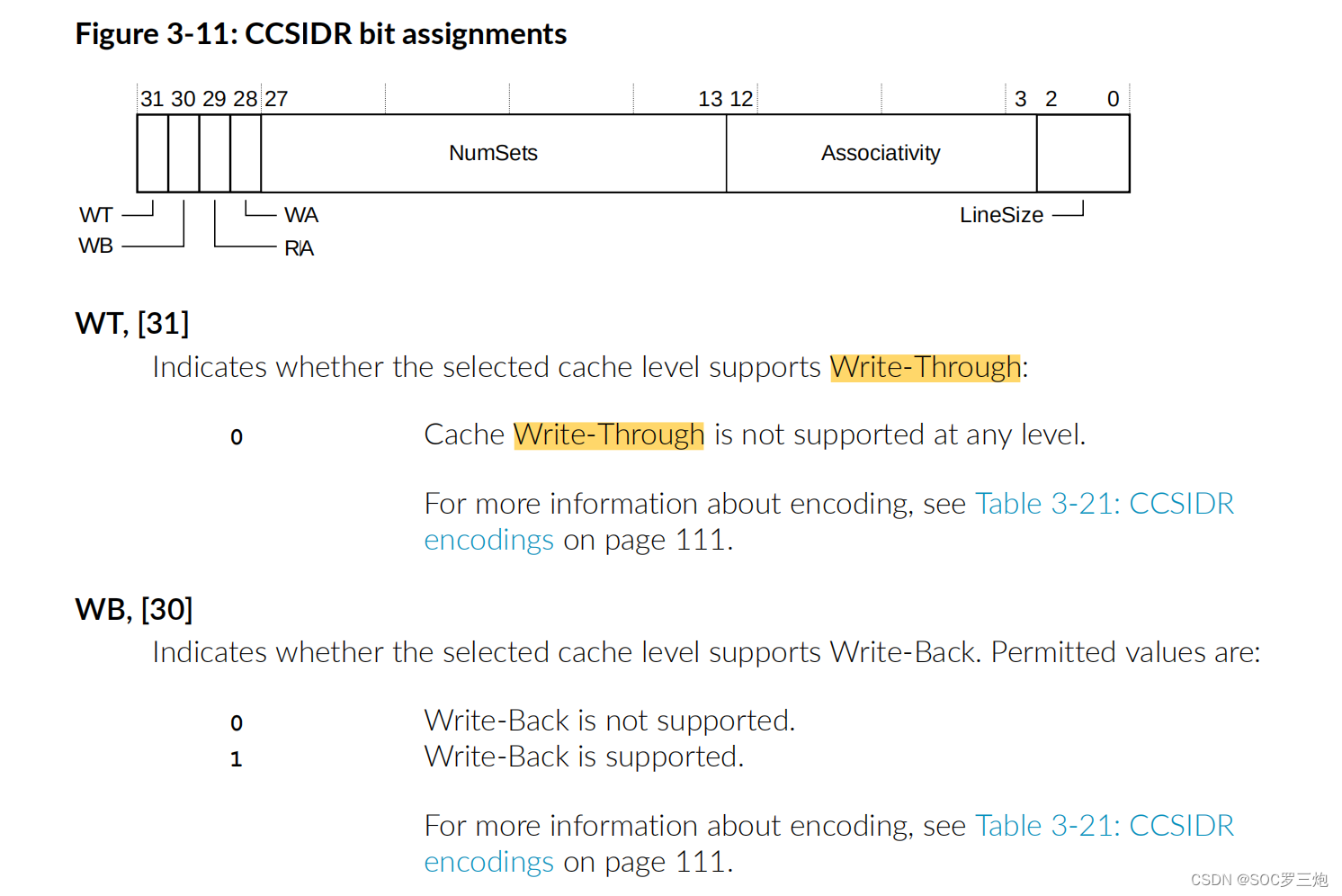

笔者在文章 关于cache maintenance 操作的四个寄存器(CTR,CLIDR,CSSELR,CCSIDR)解析中介绍过 CCSIDR寄存器,在访问CCSIDR之前,必须先在CSSELR寄存器中写入正确的值, 与CSSELR相对应,会根据CSSELR中的内容,显示指定cache的cache line大小、way的数量以及set的数量。

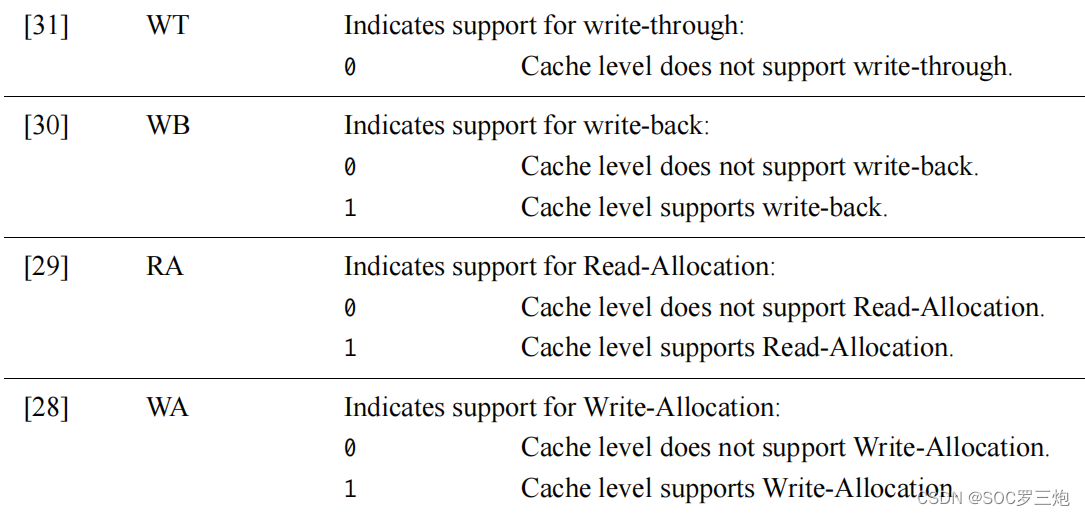

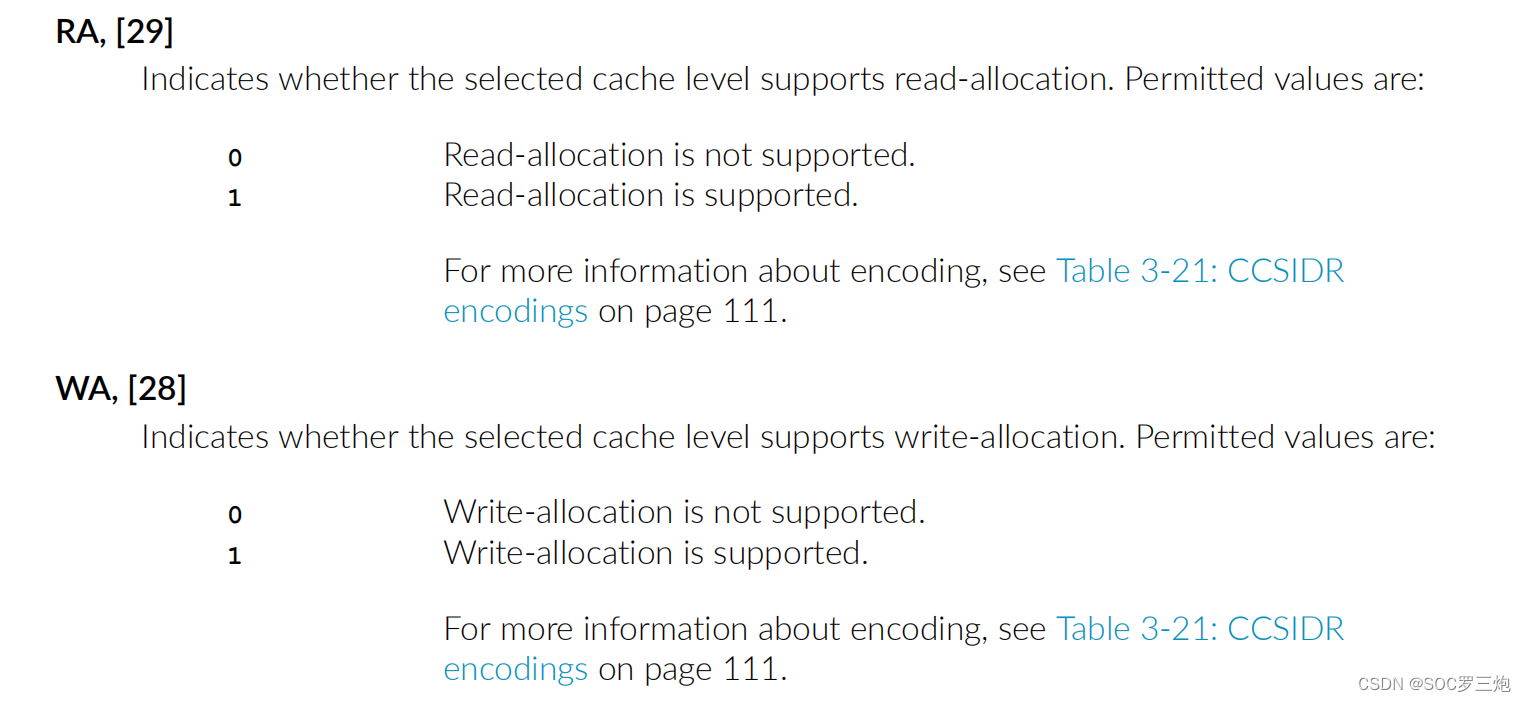

不仅如此,CCSIDR还提供了四个状态位:WT、WB、RA以及WA:

通过这四个状态位,我们可以知道当前cache所支持的读分配策略以及写策略。

从WT始终为0也可以知道:Cortex-A53的所有级别的cacahe都不支持 Write-Through策略。

二,Cortex-A55 处理器

Cortex-A53 处理器支持 L1 cache(instruction cache 和 data cache),L2 cache (unified cache)以及L3 cache。

Cortex-A55处理器也将缓存同步逻辑简化成了如下的内存类型:

- 当内存类型为Inner Write-Back 或者 Outer Write-Back 时,该内存上的数据才会被缓存到 L1 data cache 以及L2 cache中

- 当内存类型为其他类型(包括 Write-Through)时,都会被视为Non-cacheable,即都不会被缓存。

所以Cortex-A55处理器对Write-Through策略的处理也是大同小异:

当内存被标记为 Write-Through属性时,读写该内存上的数据,不会被cache缓存,也不会发起cache coherency请求。对于被标记为Write-Through 或者Write-Back的指令数据,它可以被存储在L1 instruction cache,但是只有Write-Back属性的数据可以被缓存到L2 cache或者L3 cache。

同Cortex-A53一样,其CCSIDR的WT状态位也始终为0,说明对Cortex-A55 来讲,它的任何级别的cache(L1/L2/L3)都不支持 Write-Through 策略。

这篇关于以ARM Cortex-A55/A53为例分析 L1/L2/L3 cache所支持的写策略(write-back/wirte-through,写通和写回)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!