a55专题

以ARM Cortex-A55/A53为例分析 L1/L2/L3 cache所支持的写策略(write-back/wirte-through,写通和写回)

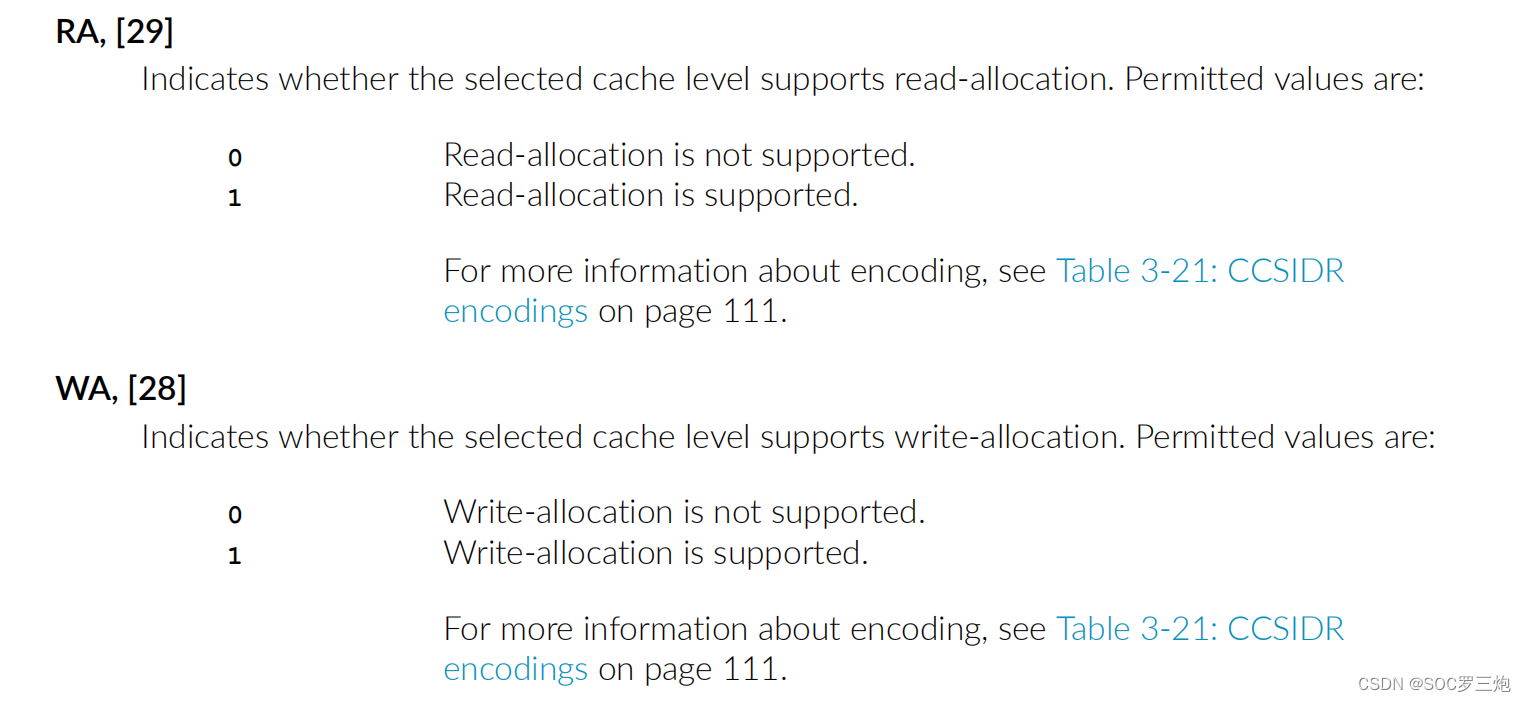

在文章 ARM 中缓存维护策略:Allocate policy(读分配/写分配),Write policy(写通/写回)以及replacement policy基础知识中,笔者介绍了ARM cache的Write policy(写通/写回)。今天我们以ARM Cortex-A55和A53为例,具体分析各级cache(L1/L2/L3 )对Write policy(写通/写回)的支持情况。

国产AI边缘计算盒子,双核心A55丨2.5Tops算力

边缘计算盒子 双核心A55丨2.5Tops算力 ● 2.5Tops@INT8算力,支持INT8/INT4/FP16多精度混合量化。 ● 4路以上1080p@30fps视频编解码,IVE模块独立提供图像基础算子加速。 ● 支持Caffe、ONNX/PyTorch深度学习框架,提供resnet50、yolov5等AI算法基础例程。 ● Mindstudio 图形化开发环境,集成模型转换量化和

国产AI边缘计算盒子,双核心A55丨2.5Tops算力

边缘计算盒子 双核心A55丨2.5Tops算力 ● 2.5Tops@INT8算力,支持INT8/INT4/FP16多精度混合量化。 ● 4路以上1080p@30fps视频编解码,IVE模块独立提供图像基础算子加速。 ● 支持Caffe、ONNX/PyTorch深度学习框架,提供resnet50、yolov5等AI算法基础例程。 ● Mindstudio 图形化开发环境,集成模型转换量化和

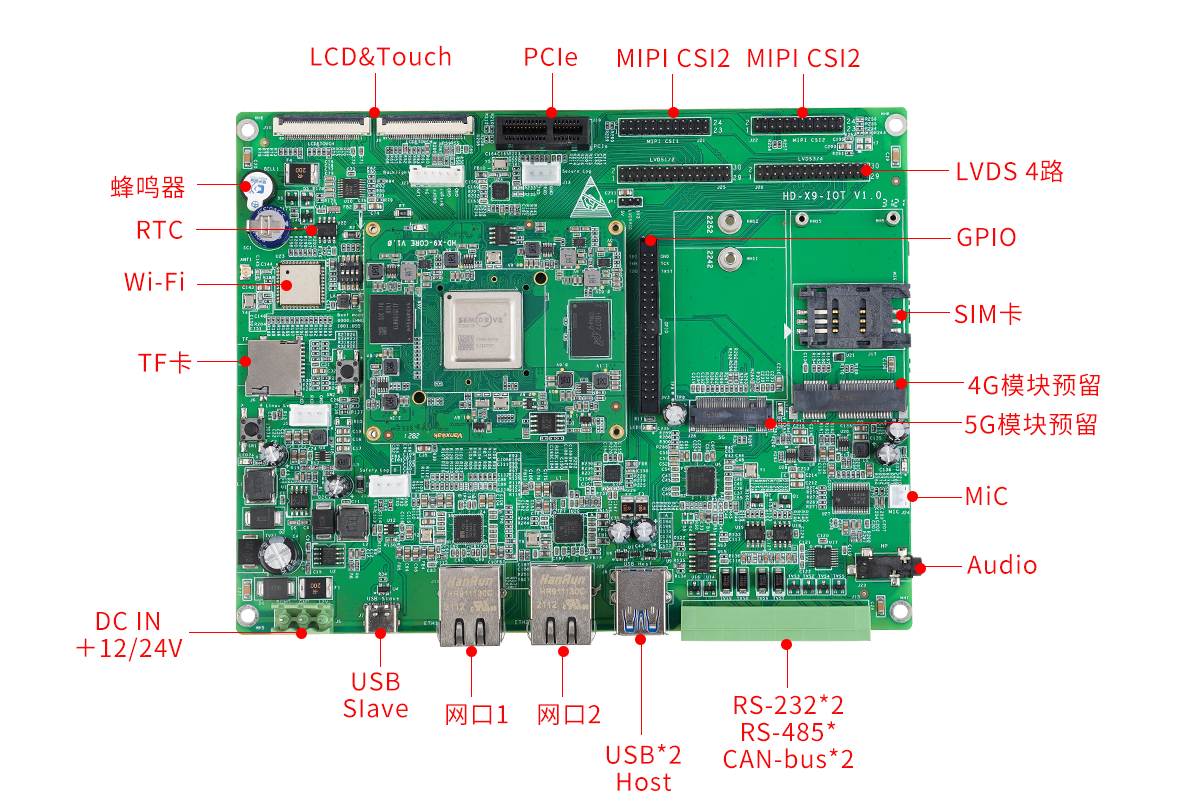

国产车规级6核Cortex-A55-芯驰X9

Cortex-A55核心板|X9六核 基于芯弛X9系列Cortex-A55高性能处理器设计,集成Cortex-R5安全岛(实时硬核),支持PCIe3.0、USB3.0、千兆网(TSN)、2路CAN-FD、高清显示接口、4路LVDS、摄像头接口、3D、H.264/H.265视频硬件编解码、16路串口、PWM、ADC等,适用于快速开发一系列最具创新性的应用,如智能驾仓、车载终端等。

海思专业级图像分析处理边缘计算盒子,双核A55 64位处理器+2.5TOPS算力

随着大模型、物联网等技术的快速发展,边缘计算逐渐成为了当今信息技术领域的研究热点,边缘算力的重要性愈加凸显。据市场需求反馈,大量长尾场景普遍具有小型化、灵活多变、即时性等特点,更需要关注算力的利用率、以及方案的成本、灵活性等问题,而轻量化的算力解决方案有助于项目降低成本、快速落地,回报更好。 在边缘算力的应用中,智能视频监控是核心的应用场景,而华为海思芯片在视频处理领域的应用有更出色的表现,

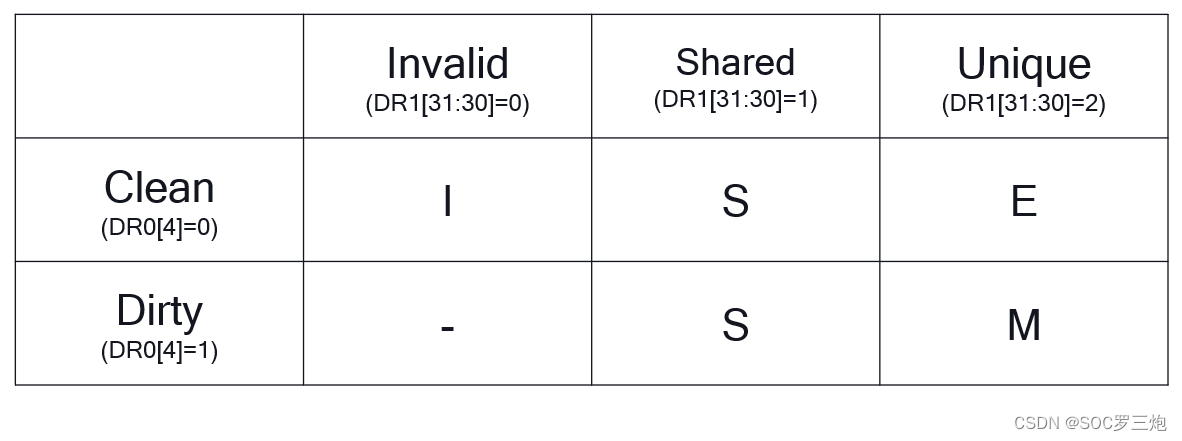

ARMv8如何读取cache line中MESI 状态以及Tag信息(tag RAM dirty RAM)并以Cortex-A55示例

Cortex-A55 MESI 状态获取 一,系统寄存器以及读写指令二,Cortex-A55 Data cache的MESI信息获取(AARCH 64)2.1 将Set/way信息写入Data Cache Tag Read Operation Register2.2 读取Data Register 1和Data Register 0数据并解码 参考文章: 一,系统寄存器以及读写指令