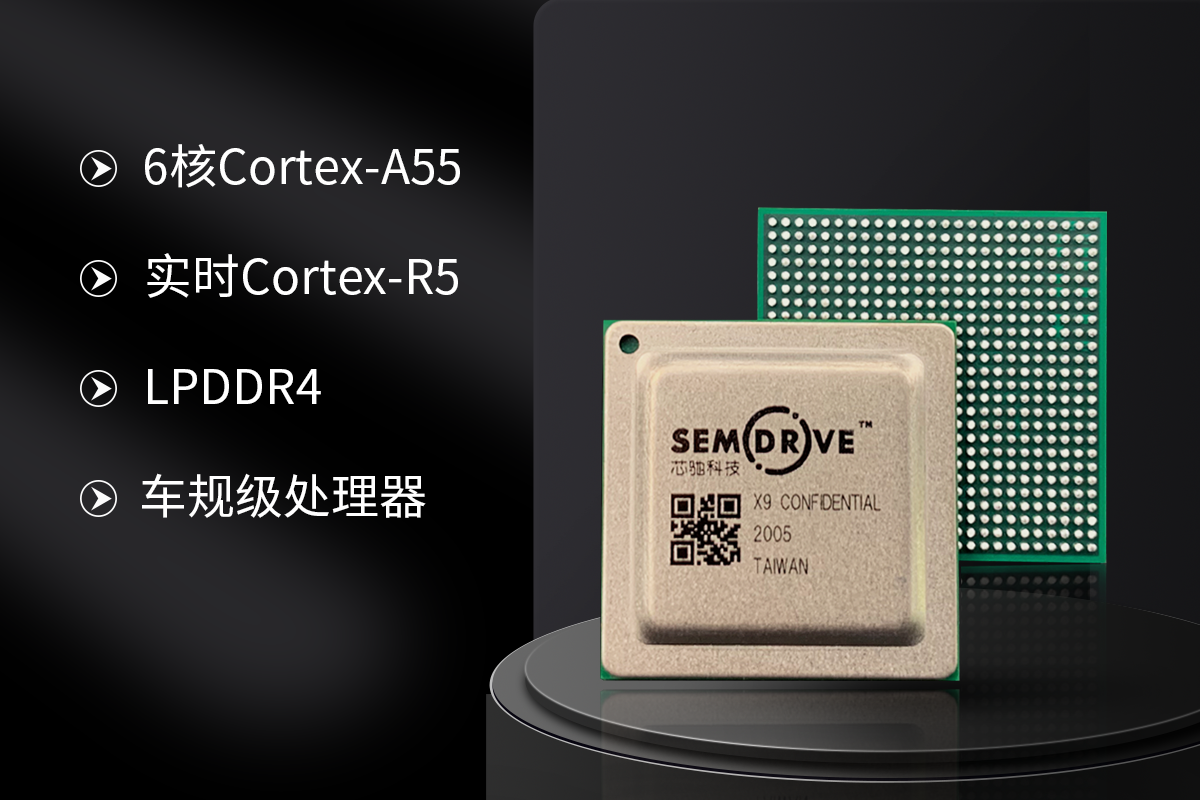

本文主要是介绍国产车规级6核Cortex-A55-芯驰X9,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Cortex-A55核心板|X9六核

基于芯弛X9系列Cortex-A55高性能处理器设计,集成Cortex-R5安全岛(实时硬核),支持PCIe3.0、USB3.0、千兆网(TSN)、2路CAN-FD、高清显示接口、4路LVDS、摄像头接口、3D、H.264/H.265视频硬件编解码、16路串口、PWM、ADC等,适用于快速开发一系列最具创新性的应用,如智能驾仓、车载终端等。

Cortex-A55核心板|X9六核

车规级 | 高性能 | 丰富接口

X9系列处理器接口全面,车规级芯片标准,功耗低至4W,适用于汽车电子、电力、轨道交通、环保等多行业领域。

车规级 | 高性能 | 丰富接口

六核Cortex-A55 +实时硬核Cortex-R5

万象奥科X9核心板搭载2/4/6核Cortex-A55,主频1.6GHz;集成Cotex-R5硬核满足现场实时任务处理需求。

六核Cortex-A55 +实时硬核Cortex-R5

4K超高清 | 多屏同显异显

集成3D图形加速引擎,支持4K/1080P/H.264编解码/H.265解码,支持多屏同显、多屏异显。

4K超高清 | 多屏同显异显

Android & Linux & RTOS三系统同时运行

支持Android、Linux与RTOS三系统同时运行,影音娱乐、通信控制、实时任务异核同步运行!

Android & Linux & RTOS三系统同时运行

高速且丰富的通信接口

集成PCIe3.0、USB3.0、千兆网(支持TSN)、2路CAN-FD接口、16路UART接口等,并支持网口、CAN、串口功能扩展。

高速且丰富的通信接口

硬件参数

芯驰X9硬件参数

详尽开发配套资料

万象奥科结合芯驰X9高端处理器芯片性能优势、原厂供货与技术保障,共同为用户提供深度技术服务,并结合行业特点可提供个性化定制服务。

芯驰X9详尽开发配套资料

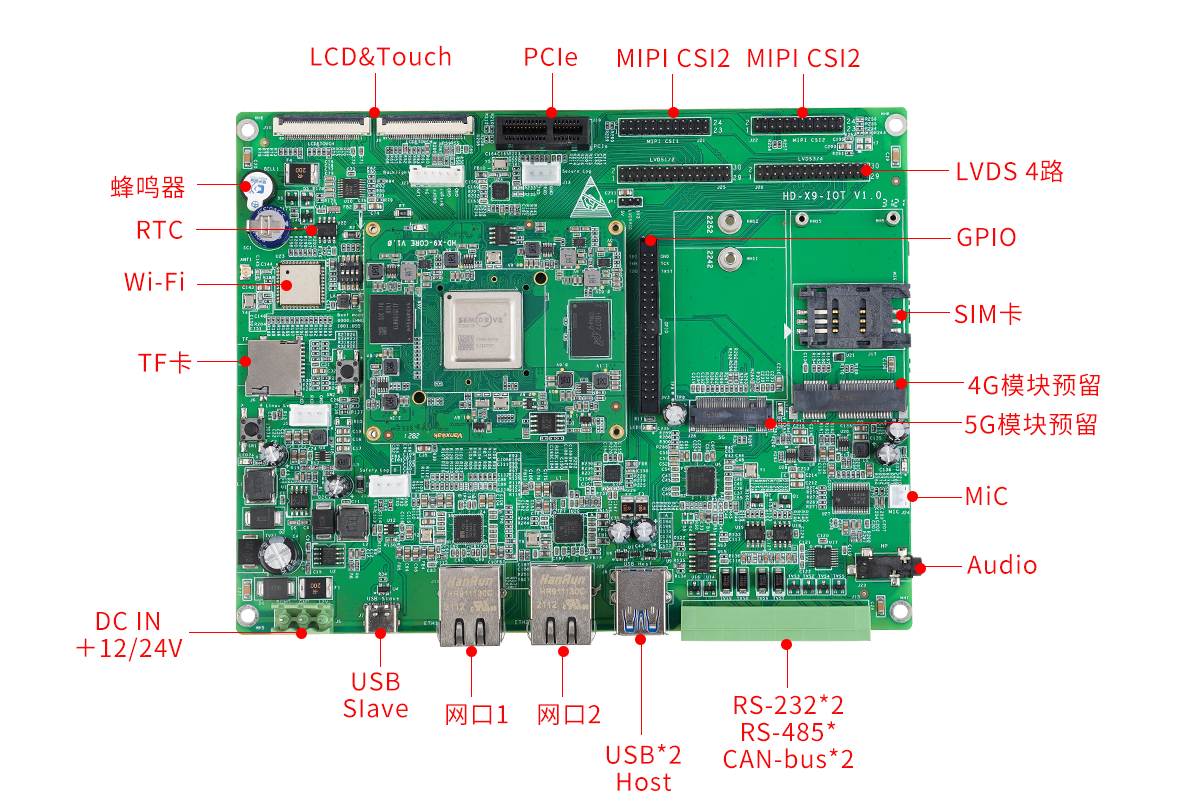

全功能评估板

双路网口、双路 CAN-bus、3 路 USB、7 路串口(2 路 RS-232、 2 路 RS-485、 3 路 TTL)、 LVDS、 LCD、 4G/5G、 WiFi 等, 接口丰富,方便用户评估核心板及 CPU 的性能。

芯驰X9全功能评估板

这篇关于国产车规级6核Cortex-A55-芯驰X9的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!