cortex专题

Cortex-A7:ARM官方推荐的嵌套中断实现机制

0 参考资料 ARM Cortex-A(armV7)编程手册V4.0.pdf ARM体系结构与编程第2版 1 前言 Cortex-M系列内核MCU中断硬件原生支持嵌套中断,开发者不需要为了实现嵌套中断而进行额外的工作。但在Cortex-A7中,硬件原生是不支持嵌套中断的,这从Cortex-A7中断向量表中仅为外部中断设置了一个中断向量可以看出。本文介绍ARM官方推荐使用的嵌套中断实现机

基于IMX6ULL的Cortex-A中断原理讲解,以及编写其中断向量表

首先借助STM32我们需要了解中断系统是如何构成的 会有一个中断源,也就是能够向CPU发出中断请求的设备或事件。中断源不分硬件和软件,也就是产生中断信号,就会执行中断服务函数 但是CPU是如何知道中断源产生后就找到对应的中断服务函数呢,这个时候就要引入中断向量表,它的主要功能是描述中断对应的中断服务函数,每个中断源都有一个唯一的中断号(也称向量号),

Cortex-M3架构学习

本学习参照 “Cortex-M3权威指南”学习,需要详细学习,建议自行观看。 Cortex-M3基础 CM3介绍 Cortex-M3 处理器内核其实就是单片机的中央处理单元( CPU )。 完整的基于 CM3 的 MCU 还需要很多其它组件,如下, Cortex-M3 是一个 32 位处理器内核; 内部的数据路径是 32 位的,寄存器是 3

cortex-m4系列绝对地址函数跳转问题

一、环境: cortex-m4,IAR,J-LINK。 二、问题: 1)、首先, 我将另一个程序中的函数扣出来,通过j-flash-lite下载到MCU的一个固定地址Flash中。 2)、然后, 声明一个变量为函数指针,同时将这个常量经过强转后赋值给该变量。 3)、接着, 用该变量做函数跳转。 形如:

Cortex-M --- 中断向量表

昨天在浏览STM32数据手册的时候在中断这一章看到了Vector table中断向量表,本文介绍一下对于向量表的理解,包括中断向量表何时执行,如何执行,存放的是什么,存放的大小。 话不多说先放图 图1 中断向量表 可以看到在M4内核的中断向量表中共包含了91+4,默认情况下95个中断优先级,而且需要注意的是中断优先级可以是负数,例如在这里REST中断的优先

【Arm Cortex-X925】 -【第二章】-Cortex-X925 core简介

2. Cortex-X925 核心 Cortex-X925 核心是一款高性能、低功耗的产品,采用了 Armv9.2-A 架构。Armv9.2-A 架构在 Armv8‑A 架构的基础上进行了扩展,涵盖了 Armv8.7‑A。 Cortex-X925 核心集成在 DSU-120 DynamIQ™ 集群内。它连接到 DynamIQ™ Shared Unit-120,该单元作为一个完整的互连系统,包含

【Arm Cortex-X925】 -【第九章】-L2 内存系统

9. L2 内存系统 Cortex®-X925 核心的 L2 内存系统通过 CPU 桥接器将核心与 DynamIQ™ Shared Unit-120 连接。它包括私有的 L2 缓存。 L2 缓存是统一的,并且对集群中的每个 Cortex®-X925 核心都是私有的。 以下表格显示了 L2 内存系统的特点。 9.1 L2 缓存 集成的 L2 缓存处理来自指令和数据侧的指令和数据请求,以及

【Arm Cortex-X925】 -【第七章】-L1 指令内存系统

7. L1 指令内存系统 Cortex-X925 核心的 L1 指令内存系统负责提取指令和预测分支。它包括 L1 指令缓存和 L1 指令转换后备缓冲区 (TLB)。L1 指令内存系统向解码器提供指令流。为了提高整体性能和降低功耗,L1 指令内存系统采用了动态分支预测和指令缓存技术。 下表显示了 L1 指令内存系统的特点。 注意 L1 指令 TLB 也位于 L1 指令内存系统中。然而,它是

《ARM Cortex-R 学习指南》-【第十七章】-调试

快速链接: . 👉👉👉 ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 付费专栏-付费课程 【购买须知】 个人博客笔记导读目录(全部) 第十七章 调试 调试是软件开发中的关键部分,通常被认为是最耗时(因此也最昂贵)的一部分。错误可能难以检测、重现和修复,并且很难预测解决缺陷所需的时间。当产品交付给客户时,解决问题的成本显著增加。在许多情况下,当产品的

《ARM Cortex-R 学习指南》-【第十四章】-为 Cortex-R 处理器编写代码

快速链接: . 👉👉👉 ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 付费专栏-付费课程 【购买须知】 个人博客笔记导读目录(全部) 第十四章 为 Cortex-R 处理器编写代码 你可以针对功耗、速度、代码密度或内存占用来优化代码。许多 GNU GCC 和 ARM 编译器功能利用 Cortex-R 系列设计生成优化代码。 14.1 编译器优化

Cortex-A7支持的内存类型详解及配置举例

0 参考资料 Introduction to memory protection unit management on STM32 MCUs.pdf ARM ArchitectureReference Manual ARMv7-A and ARMv7-R edition.pdf 1 Cortex-A7支持的内存类型详解 1.1 内存类型 ARM架构处理器支持的内存类型分为三种,分别是

《ARM Cortex-R 学习指南》-【第二章】-ARM 架构与处理器

第二章 ARM 架构与处理器 ARM 会定期发布新版本的架构,这些版本会增加新功能或对现有行为进行更改。这些更改几乎总是向后兼容的,这意味着在旧版本架构上运行的用户代码在新版本上仍然可以正确运行。当然,利用新功能编写的代码将无法在缺乏这些功能的旧处理器上运行。 在所有版本的架构中,某些系统特性和行为是实现定义的。例如,架构并不定义缓存大小或单个指令的周期时间,这些由具体的处理器和 SoC 决定

ARM交叉编译工具链下载地址_cortex-M, cortex-A, linaro

目录 1.STM32的gcc编译器下载 2.cortex-A编译器下载 3.Linaro交叉编译工具 1.STM32的gcc编译器下载 Arm GNU Toolchain | GNU Arm Embedded Toolchain – Arm Developer 2.cortex-A编译器下载 Arm GNU Toolchain | GNU-A Downloads – Arm

Cortex-A7的GIC(通用中断控制器):专有名词简介

0 资料 ARM® Generic Interrupt Controller Architecture version 2.0 Architecture Specification 1 专有名词简介 1.1 中断状态 说明: Inactive:未激活,中断无效。中断非挂起或非激活。 Pending:挂起,中断有效。等待被处理的中断。 Active:激活,中断有效。正在被CPU处理的中断

Cortex-M4 HardFault原因查找方法

Cortex-M4 HardFault原因查找方法 文章目录 Cortex-M4 HardFault原因查找方法写此博客背景思想简说我的做法Step 1:Step 2:Step 3:Step 4:Step 5:Step 5: 结果分析 写此博客背景 最近几日在Github上看到一个叫Armink的大神做了一个追踪Cortex-M系列的HardFault项目,具体连接:请点

微型操作系统内核源码详解系列五(1):arm cortex m3架构

系列一:微型操作系统内核源码详解系列一:rtos内核源码概论篇(以freertos为例)-CSDN博客 系列二:微型操作系统内核源码详解系列二:数据结构和对象篇(以freertos为例)-CSDN博客 系列三:微型操作系统内核源码详解系列三(0):空间存储及内存管理篇(前置篇)-CSDN博客 微型操作系统内核源码详解系列三(1):任务及切换篇(任务函数定义)

电机专用32位MCU PY32MD310,Arm® Cortex-M0+内核

PY32MD310是一颗专为电机控制设计的MCU,非常适合用做三相/单相 BLDC/PMSM 的主控芯片。芯片采用了高性能的 32 位 ARM® Cortex®-M0+ 内核,QFN32封装。内置最大 64 Kbytes flash 和 8 Kbytes SRAM 存储器,最高48 MHz工作频率,多达 16 个 I/O,均可作为外部中断。 PY32MD310单片机的工作温度范围为 -40℃ ~

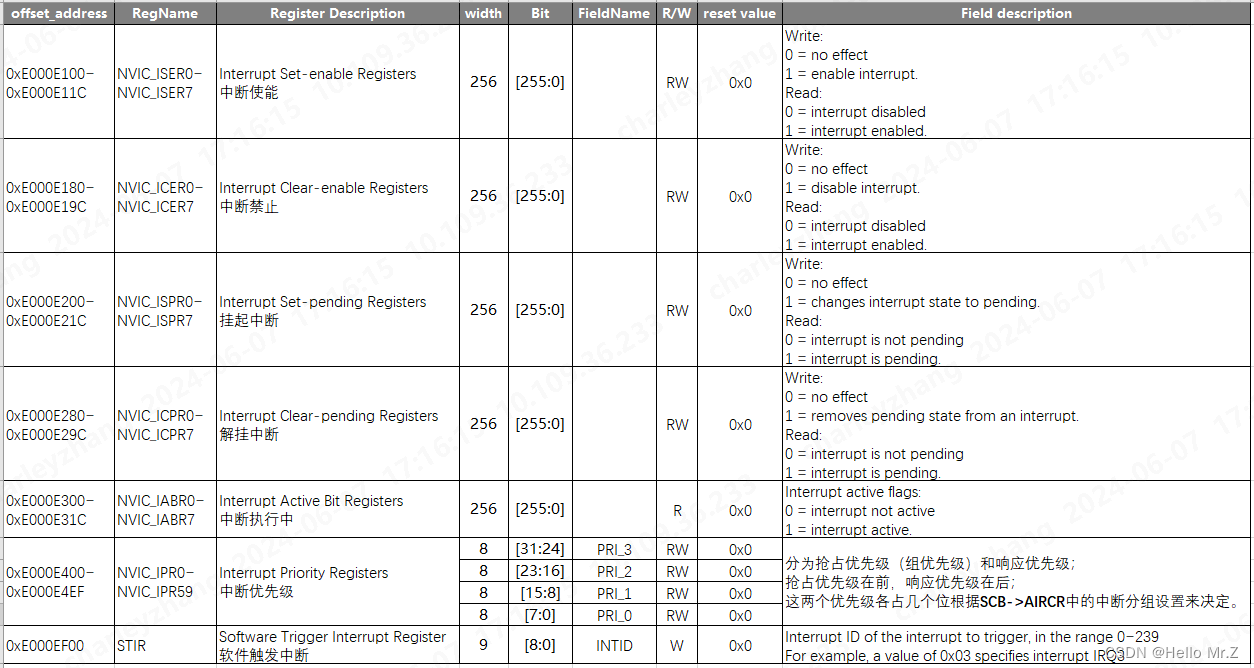

Cortex-M7——NVIC

Cortex-M7——NVIC 小狼@http://blog.csdn.net/xiaolangyangyang 一、NVIC架构 二、中断及异常编号 三、中断屏蔽寄存器(__disable_irq和__enable_irq操作的是PRIMASK寄存器) 四、中断分组寄存器(SCB->AIRCR[10:8]) 五、NVIC寄存器

汇编指令——ARM Cortex-M指令分析

cpsid i 这条指令 cpsid i 是 ARM Cortex-M 处理器的汇编语言指令,用于关闭全局中断。在 ARM Cortex-M 处理器中,cpsid i 指令的作用是将处理器的中断(IRQ)禁用,以防止中断干扰当前的执行流程。这意味着在执行这条指令后,CPU 将不再响应任何中断请求,直到相应的使能指令被执行以重新开启中断。 ldr ldr 是 ARM 汇编语言中的一个指令,用于

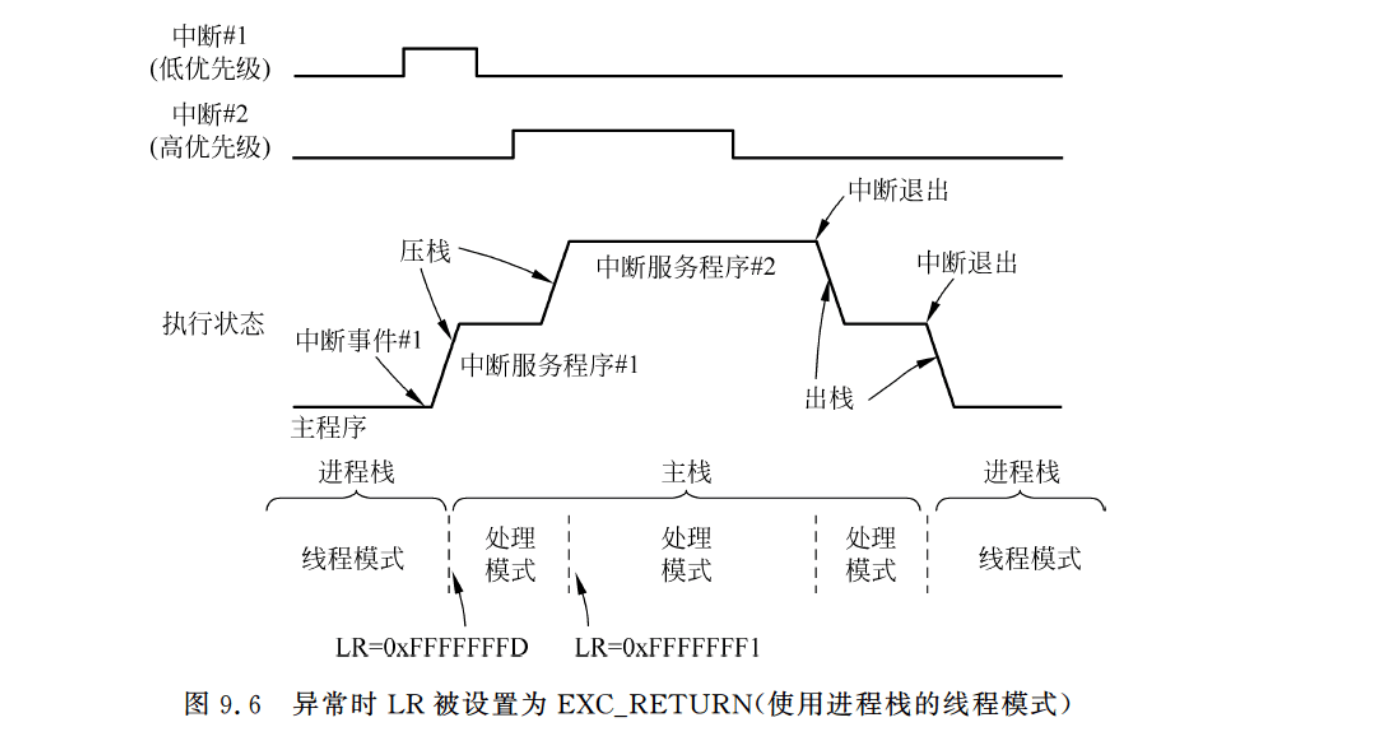

ARM cortex-M3 异常处理分析

一、进入异常之前处理器可能的状态有: 1. handler 2. 线程,MSP 3. 线程,PSP 二、产生异常时: 1、 有一个压栈的过程,产生异常时使用PSP,就压入到PSP中,产生异常时使用MSP,就压入到MSP中 2、 会根据处理器的模式和使用的堆栈,设置LR的值(当然设置完的LR的值再压栈) 三、异常返回时: 根据LR的值,判读使

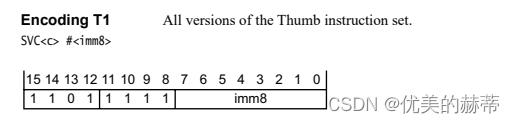

arm cortex-m架构 SVC指令详解以及其在freertos的应用

1. 前置知识 本文基于arm cortex-m架构描述, 关于arm cortex-m的一些基础知识可以参考我另外几篇文章: arm cortex-m 架构简述arm异常处理分析c语言函数调用规范-基于arm 分析 2 SVC指令 2.1 SVC指令位域表示 bit15 - bit12:条件码(Condition Code),用于控制指令的条件执行(EQ,NE,… )。bit11-

基于Cortex的MCU设计

基于Cortex的MCU设计 今日更新的存货文档,发现日更文章还是很花时间的。保证一周更新三篇文章就行啦,本篇文章的内容起始主要取自于《Cortex-M3 权威指南》和知网下载的论文。写的不详细,想进一步了解的就去看这篇文档或网上找别的资料,有错误的地方评论区留言或者私信我,我再更改。书本网盘链接如下,永久有效链接。 链接:https://pan.baidu.com/s/1Zp0L1rAnCJ

cortex-m单片机厂商及特点

主要厂商有以下5个意法半导体兆易创新NXP瑞芯微新唐科技microchip 也是单片机厂家,但是用的是 mips 架构 和 自有架构 TI 也是单片机厂家,但是用的是 mips 架构 和 自有架构 atmel 也是单片机厂家,但是用的是 arm 架构 和 自有架构 瑞萨 也是单片机厂家,但是用的是 arm 架构 和 自有架构 工程角度对各厂家cpu的介

cortex-m 单片机在 arm产品中的位置及类别

cortex-m 单片机在arm产品中的位置 https://developer.arm.com/ip-products/processors 下面有1类 processor ,是 cortex-mThe Arm Cortex-M series contains the smallest/lowest power processors build by Arm, optimized for di

【ARM Cortex-M 系列 2.1 -- Cortex-M7 Debug system registers】

请阅读【嵌入式开发学习必备专栏】 文章目录 Debug system registers中断控制状态寄存器(ICSR)Debug Halting Control and Status Register, DHCSR Debug 寄存器DCRSR与DCRDRCPU 寄存器读操作CPU 寄存器写操作CPU 寄存器选择CPU 寄存器读写示例 调试故障状态寄存器(DFSR) Deb

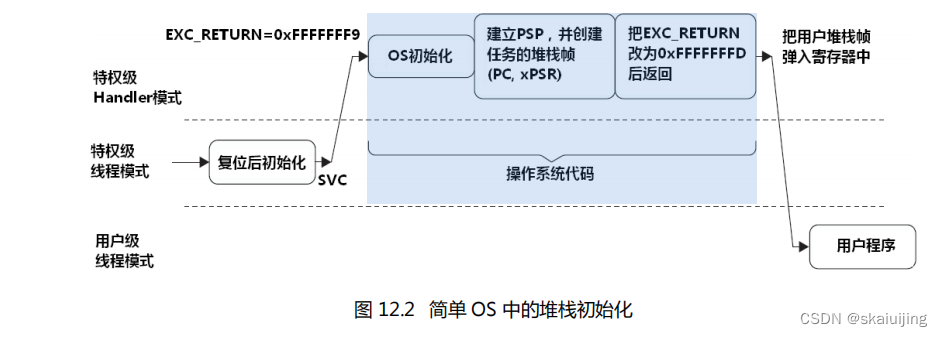

【ARM Cortex-M3指南】8:中断行为

文章目录 八、中断行为8.1 中断/异常流程8.1.1 压栈8.1.2 取向量8.1.3 寄存器更新 8.2 异常退出8.3 嵌套中断8.4 末尾连锁中断8.5 延迟到达8.6 进一步了解异常返回值8.7 中断等待8.8 中断相关的错误8.8.1 压栈8.8.2 出栈8.8.3 取向量8.8.4 非法返回 八、中断行为 8.1 中断/异常流程 异常发生时,同时会伴随着多种情