片上专题

浅谈SOC片上系统LoRa-STM32WLE5数据安全防御机制

随着物联网设备的普及,数以亿计的设备正在通过无线网络进行通信,传输大量的敏感数据。这种大规模的设备联网带来了便捷性,但也伴随着巨大的安全风险。SoC片上系统通过将无线通信、处理器、存储和安全机制集成在同一个芯片中,为物联网应用提供了高度集成的解决方案。这种设计大大简化了硬件开发流程,同时提高了设备的整体性能和安全性。SoC不仅能够满足长距离、低功耗的无线通信需求,还能通过先进的加密技术,确保数据在

【微处理器系统原理和应用设计第六讲】片上微处理器系统系统架构

一、概念辨析 首先来厘清以下概念:微处理器,微控制器,单片机,片上微处理器系统 (1)微处理器:即MPU(Microprocessor Unit),微处理器是一种计算机的中央处理单元 (CPU),通常集成在一个或多个集成电路 (IC) 中。微处理器执行指令,并处理计算机中的数据。微处理器一般不包含存储器、I/O接口等外围组件,通常需要搭配外部芯片(如RAM、ROM、I/O接口等)来构成完整的计

STM32基础篇:SPI片上外设

SPI外设简介 STM32芯片内部集成了SPI片上外设,可由硬件自动执行时钟生成、数据收发等功能,减轻CPU负担。对于STM32F103C8T6,其SPI资源有SPI1、SPI2。 一些参数配置: 8位/16位数据帧高位先行/低位先行时钟频率:PCLK/(2,4,8,16,32,64,128,256)支持多主机模型、主或从操作可精简为半双工/单工通信支持DMA兼容I2S协议 【注意】SPI

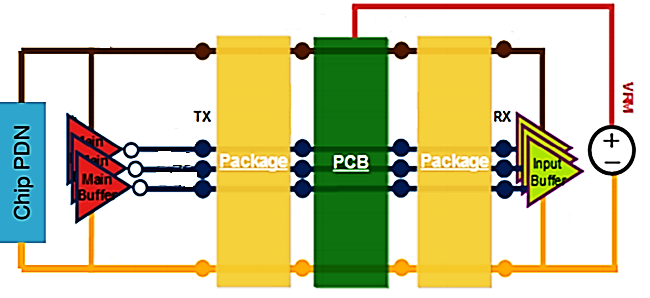

高速接口IO片上SSN分析方法

Gbps信号在当今的高速IO设计中非常常见。由于封装和板上的寄生电感,高速信号在高频下汲取电流,导致大的电源尖峰或骤降。像DDR5这样的并行总线接口有20多个高速IO一起切换,导致同时切换噪声(SSN)。SSN的不期望的产物是定时抖动或等效地称为PSIJ。随着并行总线中信号数量的增加,SSN进一步增加。当多个输出缓冲器同时改变其逻辑状态时,会产生大功率和接地反弹,如图所示。 SSN产

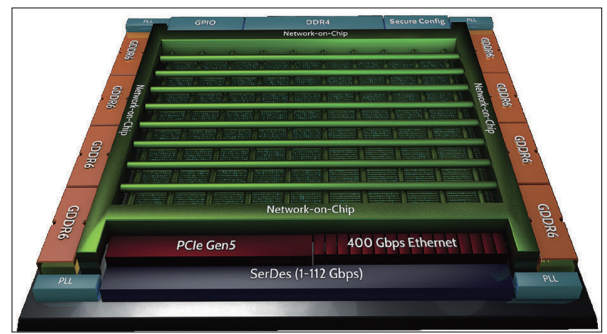

BookSim2 安装步骤教程 Network-on-Chips (NoCs) 片上网络模拟器 含视频

BookSim简介 BookSim2 一个用于Network-on-Chips (NoCs) 芯片上网络的周期精确模拟器。该模拟器的设计是为了实现网络组件的模拟灵活性和精确建模。 BookSim1 是一个通用的网络模拟器,并不专门针对片上环境。不支持在片上网络环境中提出的一些更先进的功能和拓扑结构。 背景 随着集成在单个芯片上的核心和模块数量的不断增加,片上网络正成为现代微处理器不可或缺

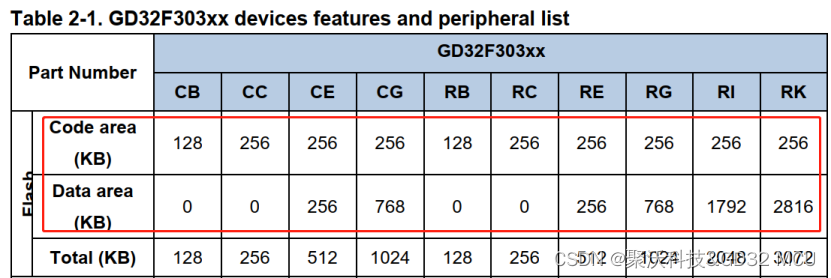

GD32F系列MCU片上Flash中Code区和Data区使用解密

GD32F系列MCU产品片上Flash分Code区和Data区,以GD32F303系列为例,从GD32F303xx Datasheet中可以获取code区和data区大小,那Code区和Data区在代码执行上有什么差别呢? Code区代码运行0等待,一般用于存放实时性要求高的代码,比如中断服务程序等;Data区代码运行有较大延迟(平均比Code区慢一个数量级),Data区一般用于存放对实时性

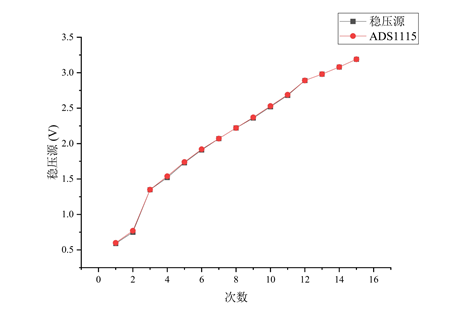

ESP32片上模数转换ADC精度简单测试方案及测试数据分享

了解ESP32测量电压的品质 ***ESP32结合Phyphox进行移动实验的技术,渐而形成为一个创作而学术的氛围,至少在国内是这样——大家能够把实验中遇到的问题和灵感互相启发,这确实是相当好的事情——此刻,大家把目光重新转向了实验的最底层保证,ESP32测量电压的准确程度怎么样*** 直接使用ESP32来测量电压,这个功能在单片机的术语里,是有专有词的:ADC,模数转换,Analog to

常关型p-GaN栅AlGaN/GaN HEMT作为片上电容器的建模与分析

来源:Modeling and Analysis of Normally-OFF p-GaN Gate AlGaN/GaN HEMT as an ON-Chip Capacitor(TED 20年) 摘要 提出了一种精确基于物理的解析模型,用于描述p-GaN栅AlGaN/GaN高电子迁移率晶体管(HEMT)的栅电容。该模型在形成泊松方程时考虑了p-GaN帽层中受主的不完全离子化以及Mg受主向A

stm32l0片上eeprom的读写操作

文章目录 一、介绍1.1 片上eeprom介绍1.2 写eeprom操作 二、编程三、测试3.1 测试代码3.2测试结果 四、例程 一、介绍 1.1 片上eeprom介绍 L0的片上eeprom特性主要用来存储系统的配置信息,f103如果需要存储配置信息,还需要额外的一颗eeprom芯片,片上eeprom的机制也符合这系列的低功耗的属性。 1.2 写eeprom操作 此操作

片上网络(NoC)技术的发展及其给高端FPGA带来的优势

片上网络(NoC)技术的发展及其给高端FPGA带来的优势 1. 概述 在摩尔定律的推动下,集成电路工艺取得了高速发展,单位面积上的晶体管数量不断增加。 片上系统(System-on-Chip,SoC)具有集成度高、功耗低、成本低等优势,已经成为大规模集成电路系统设计的主流方向,解决了通信、图像、计算、消费电子等领域的众多挑战性的难题。 随着片上系统SoC的应用需求越来越丰富,SoC需

stm32 片上flash用作EEPROM(掉电保存)(绝对可用)

一、源码: #if !defined (_FLASH_H)#define _FLASH_H#define FLASH_ADR 0x08010000 //要写入数据的地址#define u8 INT8U#define u16 INT16U#define u32 INT32Uunion union_temp16{unsigned int un_temp16;unsigned cha

【工程源码】Altera FPGA 开启引脚片上上拉电阻功能

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。 Cyclone IV E FPGA的通用输入输出管脚都支持内部弱上拉电阻,但是时钟输入脚不支持。所以,当需要上拉电阻的信号(如本例中的矩阵键盘Row信号和IIC协议中的SDA、SCL信号)连接到了FPGA的通用输入输出管脚上,在一些要求不高的场合,就可以使用片上上拉电阻来为这些信号设

片上网络NoC(7)——流控制

目录 一、概述 二、消息、数据包、flit和 phit 三、基于消息的流控制 四、基于数据包的流控制 4.1 存储转发流控制 4.2 虚拟直通流控制 五、基于flit的流控制 六、虚拟通道流控制 一、概述 流控制(flow control)负责管理网络缓冲区和链路的分配。它决定何时为消息分配相应的缓冲区和链路资源,以及分配资源的粒度,另外还决定如何在许多

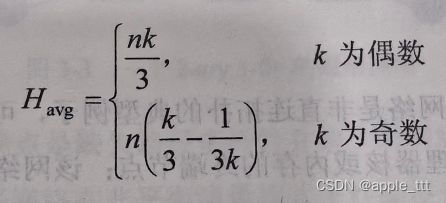

片上网络NoC(4)——直连拓扑

目录 一、前言 二、直连拓扑 三、总结 一、前言 本文中,我们将继续介绍片上网络中拓扑相关的内容,主要介绍直连拓扑,在此之前,我们已经介绍过了拓扑的指标,这将是继续阅读本文的基础,还没有了解相关内容的读者可以阅读以下文章。 片上网络NoC(3)——拓扑指标https://blog.csdn.net/apple_53311083/article/details/1

单板计算机(SBC)-片上系统(SOC)嵌入式C++和FPGA(VHDL)

要点: 片上系统/单板计算机嵌入式C++及VHDL编程单板计算机(Raspberry Pi)C++实现MQTT监控房间门锁,灯光,并使用RESTful提示状态单板计算机(ESP8266)C++ 无线网络 MQTT土壤湿度监测仪,实现HTTP服务器,创建网页版监控界面,构建ESP8266监控固件,单板计算机集成到IP网络,添加二氧化碳检测传感器,使用GPIO和PWM控制继电器和直流压控风扇片上系统

[STM32F407ZET6] 片上资源介绍

学习心得 学习一款单片机步骤: 了解有芯片上有哪些硬件资源了解内存映射, 和地址总线时钟体系 硬件资源可以让我们知道, 这个芯片都有哪些功能, 内存映射让我们知道, 我们的代码存到了哪里, 运行内存在哪里, 外设寄存器在哪里. 了解时钟体系, 是必要的, 时钟是通信的核心, 是单片机运行的心脏, 如果不了解时钟体系, 通信必然会出现不可预估的问题. STM32F407ZET6这款芯片硬件资

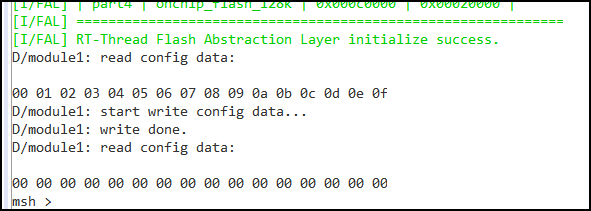

RT_Thread_使用FAL组件配置stm32f407片上flash读写

1、RT_Thread Settings打开FAL组件 2、定义struct fal_flash_dev类型的flash设备 2.1、struct fal_flash_dev 先看下struct fal_flash_dev的具体成员,有flash设备名字、flash起始地址、flash大小、块大小(执行擦除时的最小颗粒)、操作函数(init、read、write、erase)、写操作

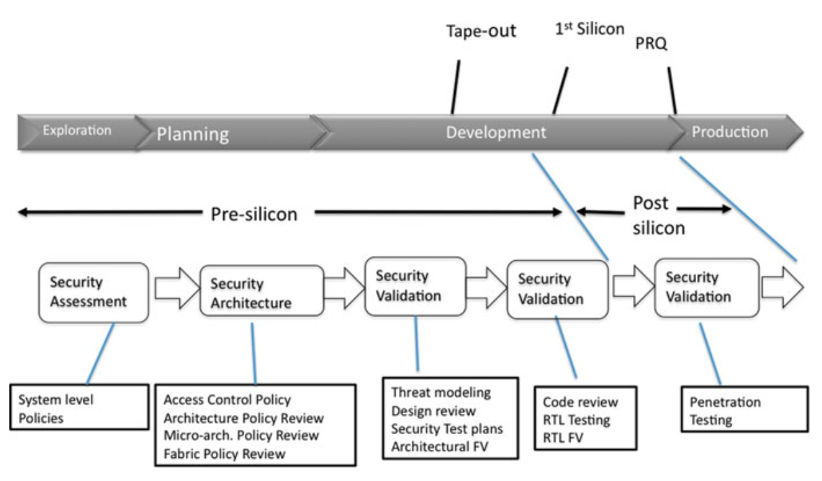

片上系统设计中的安全策略:规范,实施和验证(2)

第 1 章 SoC 安全策略:实践现状 1.1 概述 我们生活在一个被数十亿个计算系统包围的世界,这些系统识别、跟踪和分析我们的一些私密个人信息,包括健康、睡眠、位置、朋友网络等。这种设备的发展趋势是更加普及,预计到 2020 年将有 75B 台智能互联设备。这些设备生成、处理和交换大量敏感信息和数据(通常统称为“安全资产”或简称为“资产”)。除了私人最终用户信息外,资产还包括在系统架构期间引入

【K70例程】006片上RTC实时时钟

By Mcuzone 使用J-LinkV8 MDKKeil版本4.71 调试串口波特率:115200 基于MDKK70-EK_T43硬件平台 实验现象: 串口输出: Mcuzone_K70 FW_Version:100 External Pin Reset Family:K70 PinCnt:256 SiliconRevID:1.0 PFlash Size: 1024K

FPGA片上RAM、片上ROM Nios 程序不起作用的解决方法

ctrl + B 编译Nios工程 将 Nios software 的 meminit.qip onchip_rom.hex onchip_ram.hex meminit.spd 文件拷贝到FPGA目录下,再编译FPGA能起作用 Nios设置: reset 设置为 ROM 异常设置为 RAM 无优化

【ARM CoreLink 系列 1 -- SoC 片上互联介绍】

文章目录 概述1.1 片上互连架构的发展1.1.1 BUS 共享总线结构1.1.2 Crossbar 结构1.1.3 Ring 结构1.1.4 Mesh 网格结构 1.2 ARM 总线互联特点小结1.2.1 NOC 总线互联的特点 下篇文章:【ARM CoreLink 系列 1.1 – CoreLink 系列 产品介绍】 概述 在摩尔定律的推动下,集成电路工艺取得了高速发展

![[STM32F407ZET6] 片上资源介绍](https://img-blog.csdnimg.cn/direct/af9f94e59c4a4d39a91390fef30ffba3.png)